# Semiconductor Circuit Design Vol. III

Edited by: Bryan Norris, Manager, Applications Laboratory, Texas Instruments Limited

### Semiconductor Circuit Design

Bryan Norris, Texas Instruments Ltd.

This is the third in a series of text books published by Texas Instruments Limited to enable the reader to keep up-to-date with the latest developments in the field of circuit design using semiconductors.

Most of the material used in these volumes has been written by members of the Texas Instruments Applications Laboratory in Bedford. Other material has been drawn from T.I. Laboratories throughout Europe and the U.S.A. This volume has been compiled and edited by Bryan Norris from the most up-to-date information available. The four sections of the book deal with MOS integrated circuits, special purpose bipolar integrated circuits, field effect transistors and high frequency power applications. Three sections are preceded by an introductory chapter.

This book in common with the first two volumes, is therefore of use both to the moderately advanced student and to the designer in industry who can apply the circuits as they stand or adapt them as required.

The authors contributing to this volume include:

JUREK BUDEK

ALAN CHAPPELL

HOWARD COOK

JONATHAN DELL

GARRY GARRARD

JEAN-MARIE KRAUSENER

RICHARD MANN

BOB PARSONS

DALE PIPPENGER

MIKE STEVENS

ISBN 0 904047 02 4

# Semiconductor Circuit Design

### Vol. III

Edited by: Bryan Norris Manager, Applications Laboratory, Texas Instruments Limited

#### Copyright 1974 by Texas Instruments Limited

#### All Rights Reserved

This publication, or parts thereof, may not be reproduced in any form without the permission of the publishers, Texas Instruments Ltd. Texas Instruments reserve the rights to make changes at any time in order to improve design and supply the best product possible. Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patent or rights of others which may result from its use. No licence is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

### **Preface**

The popularity of the two preceding volumes of this Semiconductor Circuit Design series gave the incentive to produce this third volume. The chapters on Circuit Design again cover a wide range of semiconductor devices and I have followed the previous format by grouping them into broad device-type sections. These are MOS Integrated Circuits, Special Purpose Bipolar Integrated Circuits, Field Effect Transistors and Radio Frequency Power Transistors. Again, the first chapter of each section is of an introductory nature.

In the first section on MOS I.C.s the Applications Chapters cover what are, in my opinion, the most important areas: Memory, Terminals, Computational and Interconnecting or Interfacing with other devices.

A wide range of special bipolar integrated circuits exists today but only a small number of their applications can be described. However, the spectrum is covered from circuits which are mainly digital with linear peripherals, such as Line Drivers and Receivers and Read-Only Memories, to completely linear circuits, such as the Double Balanced Mixer and the Audio Power Amplifier.

The major areas in which the FET is used, i.e. R.F. applications, high impedance and switching or 'chopping' circuits, are described in specific chapters of the third section.

Finally, the chapters of the fourth section explain the use of power transistors in tuned and single-sideband amplifiers and as frequency multipliers.

I should like to thank all the authors - for without their efforts this book would obviously not exist - and in particular, my colleague, David Bonham, for his help in tying up the loose ends.

**BRYAN NORRIS**

Applications Manager, Texas Instruments Limited. April, 1974.

# **Contents**

## **SECTION 1. MOS INTEGRATED CIRCUITS**

|             |                                   |      |      | Page |

|-------------|-----------------------------------|------|------|------|

| Chapter I   | PROCESS TECHNOLOGIES              |      |      | 1    |

|             | Basic Construction                |      |      | 1    |

|             | Standard Thick Oxide Process      |      |      | 2    |

|             | Nitride Process                   |      |      | 2    |

|             | Silicon Gate Process              |      |      | 3    |

|             | Complementary MOS Process         |      |      | 5    |

|             | Charge Coupled Devices            |      |      | 6    |

|             | References                        |      |      | 8    |

| Chapter II  | MOS IN TERMINALS                  |      |      | 9    |

| •           | Receiver/Transmitter              |      |      | 9    |

|             | Code Converters                   |      |      | 12   |

|             | Digital Storage Buffers (DSBs)    |      |      | 15   |

|             | Character Generators              |      |      | 17   |

|             | Display Systems                   |      |      | 22   |

|             | Keyboard Encoder                  |      |      | 27   |

| Chapter III | THE RANDOM ACCESS MEMORY          |      |      | 31   |

| Chapter III | Desire Description                | •• • |      | 31   |

|             | Operation of the DAM              |      |      | 36   |

|             | Operation of the DAM              | •••  |      | 36   |

|             | Former ding the Manner            | ••   | • •• | 38   |

|             | Control Circuits for 1k RAM       | ••   | • •• | 41   |

|             | Control Cinquita for Ala DAM      | ••   | • •• | 46   |

|             | A                                 | •••• | • •• | 40   |

|             | • •                               | •• • | • •• |      |

| Chapter IV  | ARITHMETIC PROCESSOR              |      | • •• | 49   |

|             | Internal Organisation             |      |      | 49   |

|             | Input/Output and Control Function |      | • •• | 49   |

|             | Interfacing                       |      | • •• | 53   |

|             | Practical Applications            |      |      | 54   |

| Chapter V   | INTERFACING MOS DEVICES           |      |      | 61   |

| -           | Requirements                      |      |      | 61   |

|             | Worked Examples                   |      |      | 68   |

|             | Conclusion                        |      |      | 71   |

# SECTION 2. SPECIAL PURPOSE BIPOLAR INTEGRATED CIRCUITS

|              |                                  |       |     |      |     |     |     |     | Page |

|--------------|----------------------------------|-------|-----|------|-----|-----|-----|-----|------|

| Chapter VI   | LINE DRIVERS AND RECEIVERS       |       |     |      |     |     |     |     | 75   |

| •            | Data Transmission                |       |     |      |     |     |     |     | 75   |

|              | Transmission Lines               |       |     |      |     |     |     |     | 76   |

|              | Relevant Device Characteristics  |       |     |      |     |     |     |     | 78   |

|              | Practical Devices                |       |     |      |     |     |     |     | 79   |

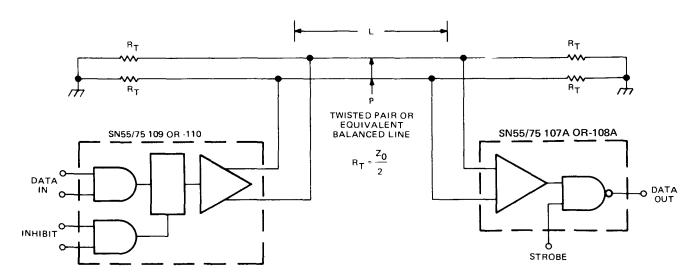

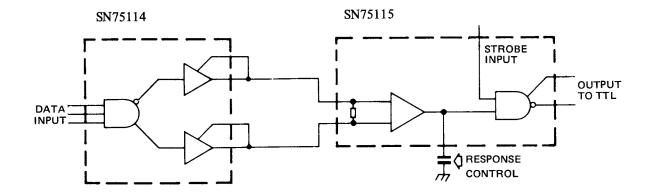

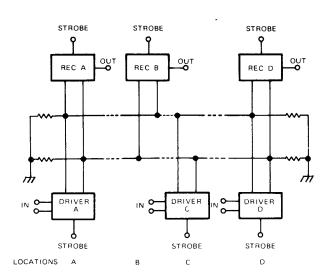

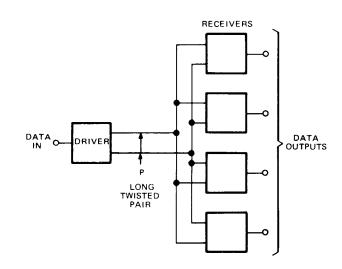

|              | System Applications              |       |     |      |     | • • |     | • • | 82   |

| Chapter VII  | (PROGRAMMABLE) READ-ONLY M       | EMORJ | ES  |      |     |     |     |     | 91   |

| 1            | Description of the SN7488 I.C    |       |     |      |     |     |     |     | 91   |

|              | Organisation of ROMs             |       |     |      |     |     |     |     | 92   |

|              | Random Logic Function Generators |       |     |      |     |     |     |     | 95   |

|              | Micro Program Store              |       |     |      |     |     |     |     | 95   |

|              | Code Converters                  |       |     |      |     |     |     |     | 97   |

|              | Sequence Generators              |       |     |      |     |     |     |     | 98   |

|              | Arithmetic Operations            |       |     |      | • • | • • | • • |     | 99   |

|              | Analogue Applications            | • •   | • • | • •  |     | • • | • • | • • | 101  |

|              | References                       | • •   | • • | • •  | • • | • • | • • | • • | 106  |

| Chapter VIII | ZERO CROSSING DETECTOR AND       | PULSE | GEN | ERAT | OR  |     |     |     | 107  |

| -            | Circuit Description              |       |     |      |     |     |     |     | 107  |

|              | Transformer and Inductive Loads  |       |     |      |     |     | • • | • • | 108  |

|              | References                       |       | • • |      | • • | • • | • • | • • | 112  |

| Chapter IX   | A DOUBLE BALANCED MIXER          |       |     |      |     |     |     |     | 113  |

| •            | Circuit Description              |       |     |      |     |     |     |     | 113  |

|              | Applications                     |       |     |      |     |     |     |     | 114  |

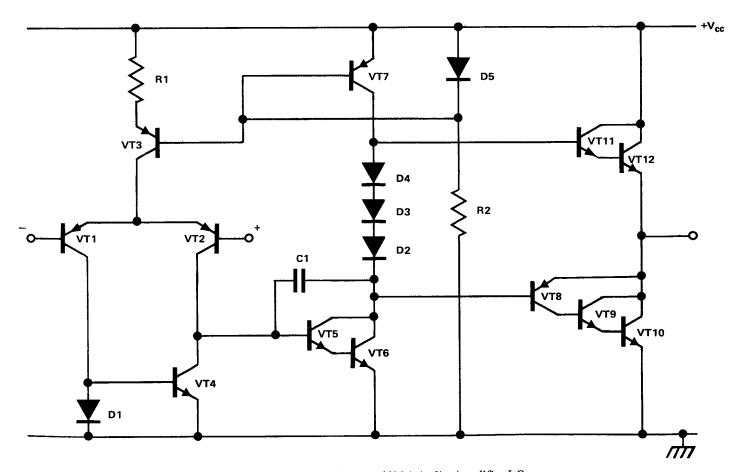

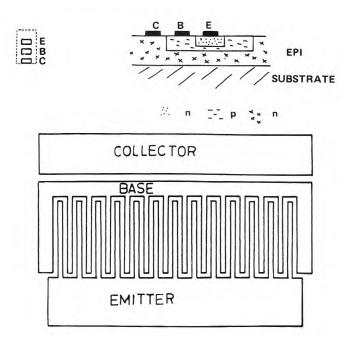

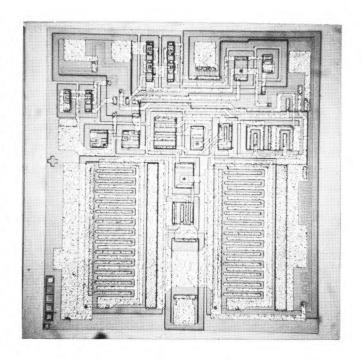

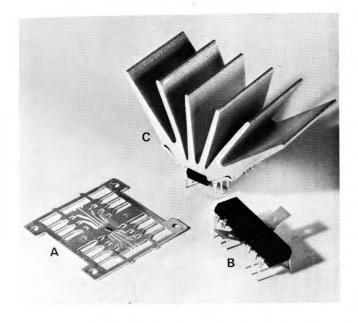

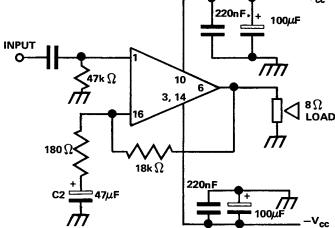

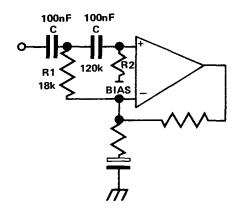

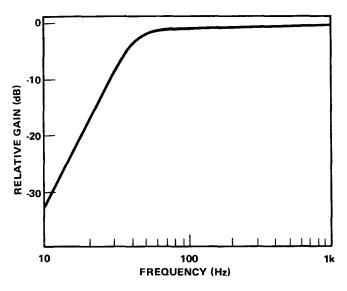

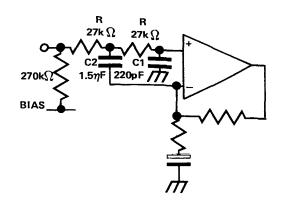

| Chapter X    | AN AUDIO POWER AMPLIFIER         |       |     |      |     |     |     |     | 127  |

| chapter 11   | Circuit Description              |       |     | • •  |     |     |     |     | 127  |

|              | Fabrication                      |       |     |      |     |     |     |     | 128  |

|              | Mounting                         |       |     |      |     |     |     |     | 128  |

|              | Power Dissipation                |       |     |      |     |     |     |     | 128  |

|              | Applications                     |       |     |      |     |     |     |     | 129  |

|              | Characterisation                 |       |     |      |     |     |     |     | 131  |

|              | References                       |       |     |      |     |     |     |     | 132  |

# **SECTION 3. FIELD EFFECT TRANSISTORS**

|              |                                                 |      | Page |

|--------------|-------------------------------------------------|------|------|

| Chapter XI   | THEORY AND OPERATION                            |      | 135  |

|              | Theory                                          |      | 135  |

|              | Construction of Practical FETs                  |      | 139  |

|              | Static Characteristics                          |      | 141  |

|              | Biasing the FET                                 |      | 143  |

|              | References                                      |      | 147  |

| Chapter XII  | RF APPLICATIONS                                 |      | 149  |

| -            | Non-Linear Devices                              |      | 149  |

|              | Cross-Modulation and Intermodulation Distortion |      | 149  |

|              | Conversion Gain                                 |      | 154  |

|              | Practical Junction FET Mixer Circuits           |      | 155  |

|              | A Tunor using MOSEETs                           |      | 160  |

|              | References                                      |      | 162  |

| Chapter XIII | HIGH INPUT IMPEDANCE CIRCUITS                   |      | 163  |

| <b>r</b>     | Basic Design Conditions                         |      | 163  |

|              | Theoretical Temperature Considerations          |      | 163  |

|              | Practical Temperature Considerations            | •    | 165  |

|              | The Balanced Amplifier                          | • •• | 167  |

|              | High Input Impedance Amplifier                  | • •• | 169  |

|              | Reference                                       |      | 171  |

|              | A January 1 day was a                           | • •• | 171  |

|              | A 1.                                            | • •• |      |

|              | ••                                              | • •• | 172  |

| Chapter XIV  | SWITCHING OR 'CHOPPING' CIRCUITS                |      | 175  |

|              | Relevant Characteristics                        |      | 175  |

|              | The Series Chopper                              |      | 177  |

|              | The Shunt Chopper                               |      | 182  |

|              | The Series/Shunt Chopper                        |      | 185  |

|              | Conclusions                                     |      | 188  |

# **SECTION 4. RADIO FREQUENCY POWER APPLICATIONS**

|                 |                                               |      |         | Page |

|-----------------|-----------------------------------------------|------|---------|------|

| Chapter XV      | RF POWER TRANSISTORS                          | <br> | <br>    | 193  |

| -               | Class of Operation                            | <br> | <br>    | 193  |

|                 | Modulation and Transistor Requirements        | <br> | <br>    | 194  |

|                 | Broadband Amplifier Technique                 | <br> | <br>    | 195  |

|                 | Impedances                                    | <br> | <br>    | 196  |

|                 | Heat Sink Design                              | <br> | <br>    | 200  |

|                 | References                                    | <br> | <br>    | 200  |

| Chapter XVI     | TUNED AMPLIFIER DESIGN 3124                   | <br> | <br>    | 201  |

|                 | Graphical Approach to Filter Design           | <br> | <br>    | 201  |

|                 | Simple Mathematical Approach to Filter Design | <br> | <br>    | 206  |

|                 | 66-88 MHz Amplifier                           | <br> | <br>    | 211  |

|                 | References                                    | <br> | <br>    | 212  |

| Chapter XVII    | LOW VOLTAGE SINGLE SIDEBAND AMPLIFIERS        | <br> | <br>    | 213  |

| <b>F</b>        | Circuit Description                           | <br> | <br>    | 213  |

|                 | Driver Stage                                  | <br> | <br>    | 216  |

|                 | References                                    | <br> | <br>    | 216  |

| Chapter XVIII   | FREQUENCY MULTIPLIERS                         | <br> | <br>    | 217  |

| Chapter 24 viii | Tuned Frequency Multipliers                   | <br> | <br>• • | 217  |

|                 | Push-Push Frequency Doublers                  | <br> | <br>    | 221  |

| Index            |        |       |        |         |       |        |    | <br> | <br> | <br> | <br>225 |

|------------------|--------|-------|--------|---------|-------|--------|----|------|------|------|---------|

| Contents of Semi | condu  | ictor | Circui | t Desi  | gn Vo | lume l | [  | <br> | <br> | <br> | <br>231 |

| Contents of Semi | icondi | ictor | Circui | it Desi | gn Vo | lume l | II | <br> | <br> | <br> | <br>233 |

# SECTION 1. MOS INTEGRATED CIRCUITS

#### I PROCESS TECHNOLOGIES

#### by Howard Cook

To understand why metal-oxide-silicon, MOS, technologies are used for the manufacture of digital integrated circuits to the extent that they are today, it is necessary to examine the basic device and manufacturing processes which are used in its implementation. As opposed to bipolar processes which use the conventional pnp or npn bipolar transistors as the basic circuit elements, MOS processes rely on the field effect transistor (FET) principles.

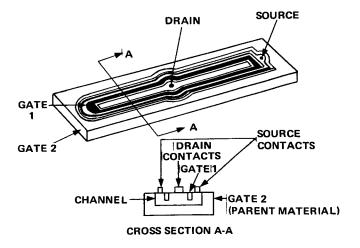

#### **BASIC CONSTRUCTION**

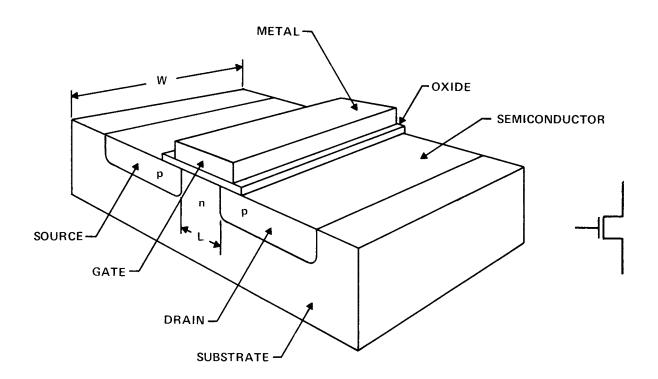

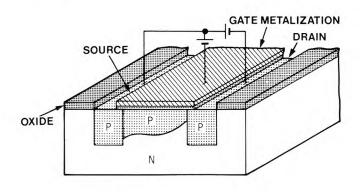

Figure 1 shows the basic construction of a p channel MOS FET and its schematic symbol. The n type substrate has two p type diffusions in its surface which form the Source and Drain of the device. A thin layer of silicon dioxide covers the area of the n type substrate between the Source and Drain diffusion. An aluminium electrode is deposited on the surface of this oxide layer and forms the Gate electrode. With no bias voltage applied between the gate electrode and n type substrate, there is no conduction path between the two p type diffusions. However, if a negative bias is applied to the gate electrode, the field beneath the electrode may be sufficient to cause the n type substrate material in this area to invert and become p type,

thus forming a conduction channel between the two p type diffusions<sup>1</sup>. The applied gate voltage at which this conduction channel just begins to form is called the 'threshold voltage' of the device. In this case, since the conduction channel is formed by the n type material inverting to p type, this is called a p channel device.

Most of the advantages of this type of device arise from two main features. The first of these features is the very high input impedance and isolation between source and drain. This allows the driver device to fan out to many similar devices in a circuit, since no input dc current is drawn, and also, to isolate charge on capacitive nodes of a circuit, giving rise to a data storage facility. This can be used to construct dynamic circuits, where the power supply to the circuit is disconnected for the majority of the time to reduce power dissipation. Another feature of the MOSFET is that it exhibits bilateral symmetry. The same device may be used to both charge or discharge the subsequent node in the circuit, thus reducing the number of devices necessary to implement many functions. A further advantage of MOS devices is the much lower number of process steps required to fabricate an active element compared with bipolar processing. Although the basic model

FIGURE 1. Basic Construction and Schematic Symbol

shown in Figure 1 is somewhat idealised, it does resemble the most simple of the current processing techniques, i.e. the standard thick oxide process.

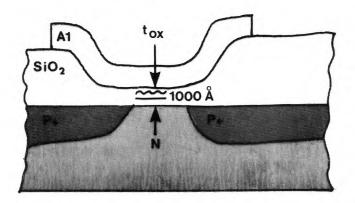

FIGURE 2. Standard Thick Oxide MOS Process

#### STANDARD THICK OXIDE PROCESS

In practice, the diffusion areas and metal depositions cannot be controlled to the extent suggested by the drawing in Figure 1 and the more irregular appearance shown in Figure 2 is nearer to the actual shapes of these areas. It can be seen that there is considerable overlap between the gate metal electrode and the source and drain diffusions. This gives rise to appreciable capacitances between these electrodes as well as from the electrodes to the substrate. A second feature of this simple device is that threshold voltage is too high,  $\stackrel{\triangle}{}$  4V, for the device to be directly compatible with TTL.

As already stated, the threshold voltage of an FET is the applied gate bias at which the conduction channel just forms. If this device is to be driven from a common saturated transistor logic family, such as T.T.L., then it is necessary for the threshold voltage of the FET to be similar to the voltage switching levels of the logic family. For operation with T.T.L. this should be in the region of 2·2V. If the threshold voltage is not directly compatible with the logic family, then it becomes necessary to interface either passively or actively, between the logic system and the MOS system, as described in Chapter V.

The threshold voltage can be derived from the expression:

$$V_T = \Phi_{MS} - \frac{Q_s}{C_{OX}} + 2.\phi_f - \frac{Q_b}{C_{OX}}$$

where

V<sub>T</sub> = Threshold voltage

$\Phi_{MS}$  = Work function metal – silicon

Q<sub>S</sub> = Charge per unit surface area at silicon-oxide interface

$C_{OX}$  = Gate capacitance corresponding to oxide over channel area

$\phi_f$  = Fermi potential

Qb = Bulk charge/unit area associated with channel depletion region

It can be seen that a significant factor in this expression is the capacitance  $C_{OX}$  and increasing this gives rise to a lower value of threshold voltage  $V_T$ . The value of capacitance  $C_{OX}$  is given by

$$C_{OX} = \frac{\epsilon_O \times \epsilon_{OX}}{t_{OX}}$$

where

$t_{OX}$  = Gate oxide thickness

$\epsilon_{OX}$  = Relative permittivity of oxide

$\epsilon_0$  = Permittivity of free space (constant)

Hence the capacitance of the gate region can be increased by reducing the thickness of the gate oxide layer, or by changing the insulating material in the gate region from oxide to another material with higher relative permittivity. Reducing the oxide thickness can cause problems in production yields and repeatability, but using a higher permittivity material is feasible, and this method gives rise to the Nitride MOS process.

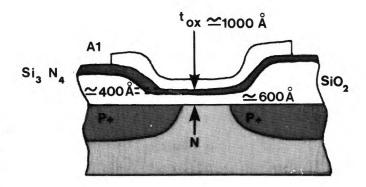

#### NITRIDE PROCESS

Figure 3 shows the construction of a device using this process. The oxide layer in the gate region has been reduced in thickness compared with the standard thick oxide process, but a layer of Silicon Nitride, Si<sub>3</sub>N<sub>4</sub>, has been added making the total thickness of the gate insulator tox. This is normally the same value as t<sub>OX</sub> for the thick oxide process but the permittivity of the gate insulator is increased by the use of the nitride layer, which has a higher value of  $\epsilon$ than the oxide. This arrangement gives rise to a lower threshold voltage and the device can be made TTL compatible by using a negative voltage rail in the order of -12V. It is not possible to entirely replace the oxide layer with nitride due to effects at the nitride - substrate interface causing variations in VT. The stability of the threshold voltage is one factor which limits the extent to which this process technique may be applied, although it does have an extra advantage, in that the nitride layer acts as a good surface protection against contamination.

FIGURE 3. Nitride MOS Process

#### STANDARD THICK OXIDE MOS PROCESS DISADVANTAGES **ADVANTAGES** SIMPLE PROCESS NON-TTL COMPATIBLE $(V_T = -4.0V)$ LOW COST +12, - 12V POWER RAIL NEEDED WELL PROVEN AND UNDERSTOOD FOR TTI COMPATIBILITY RELIABILITY ESTABLISHED POOR SPEED POWER PERFORMANCE INDUSTRY STANDARD-WIDE SECOND SOURCING NITRIDE MOS PROCESS DISADVANTAGES **ADVANTAGES** SIMPLE PROCESS THRESHOLD STABILITY POOR SPEED/POWER PERFORMANCE TTL COMPATIBILITY $(V_T = -2 \text{ to } -2.5V)$ -12V RAIL NEEDED IN TTL SYSTEM: LOW COST/HIGH YIELD IMPROVED DENSITY

Table 1 shows a comparison of the advantages and disadvantages of these two processes. They are both simple processes using few steps in production and capable of giving high production yields. This gives rise to low cost, and good reliability. Both processes suffer from a poor speed power performance figure, due to the relatively high values of inter-electrode (gate-source, gate-drain, and source-drain) capacitances.

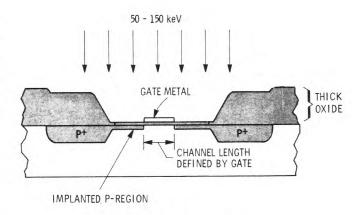

A method of improving the speed/power performance by reducing inter-electrode capacitance is by using an ion implantation technique to achieve the doping of the source and drain areas of the chip. Ions of the dopant material are accelerated to high velocity and directed at the surface of the chip. By adjusting the accelerating voltage, the energy of the ion beam can be controlled, and thus the depth of penetration of the ions into the surface of the silicon can also be controlled. Thin layers of silicon oxide will be transparent to the ion beam, but thick oxide areas will stop the ions from being absorbed. Figure 4 shows how this may be used to accurately define the edges of the source and drain diffusions by using the gate metal electrode to mask the gate oxide area from the ion beam. The thin oxide layer at the sides of the gate electrode allows the beam to penetrate to the surface of the substrate and form the edges of the p diffusions. This gives rise to a much smaller overlap between the gate and the source and drain. The ion beam can also be used to modify the doping of the substrate surface in the conduction channel, thus modifying the threshold voltage of the device. Using this method, the threshold voltage can be made as small as required, and, in fact, can be made zero, or even positive. This latter condition would mean that the device would be normally 'on' and would only turn 'off' at a positive value of gate bias. Such devices are useful as Depletion Mode load devices in place of conventional Enhancement Mode load devices which operate in the usual way, (negative V<sub>T</sub>).

FIGURE 4. Ion Implant Process

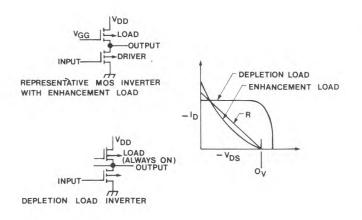

Figure 5 shows two inverters, one using a conventional enhancement load device, and the other using a depletion mode load. The graph shows the characteristics of these devices. It can be seen that the depletion mode device is always 'on' for negative VDS and acts as a current source, supplying constant drain current.

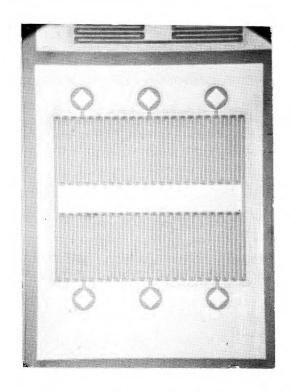

#### SILICON GATE PROCESS

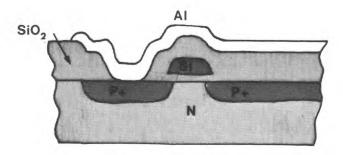

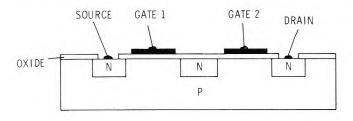

Another method used to accurately define the gatesource and gate-drain geometries is the Silicon Gate process. In this construction the gate electrode is made of polycrystalline silicon buried in silicon oxide, as shown in

FIGURE 5. Load Devices and Load Lines

Figure 6. This has two main advantages. The first is that the polycrystalline silicon gate electrode may be used as a mask for the source and drain diffusions, thus making the correct alignment of gate, source and drain automatic. This gives rise to good manufacturing yields and lower interelectrode capacitances. The second major advantage is that the polycrystalline silicon has a lower work function  $\Phi_{MS} = 0.6V$ , than aluminium, giving rise to a lower threshold voltage. Devices made using this process may be directly TTL compatible, and are capable of a much better speed-power performance than the processes previously described.

FIGURE 6. P Channel Silicon Gate

Table 2 shows a comparison of the silicon gate process with ion implant processes.

An additional advantage of the silicon gate process is the provision of another level of interconnection between devices on the same chip. As well as having a metal interconnection pattern on the surface, and the p+ diffusions under the surface, there is now the polycrystalline silicon conductor material buried in the oxide, which may be used for interconnecting.

All the examples discussed so far have used an 'n' type substrate inverting to a 'p' type conduction channel under the influence of negative gate bias, thus forming p channel devices. There is a major advantage in using the opposite type of construction, i.e. using a p substrate material with n+ diffusions into it. This relies on a conduction channel being formed by the p substrate material inverting to n type under the influence of a positive applied gate bias. In a n channel device, the majority carriers in the

Table 2

| ION IMPLA                                                                                                                                                                                                                    | ANT PROCESS                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| ADVANTAGES  SIMPLE PROCESS  ESTABLISHED METAL GATE PROCESS  HIGH YIELD (CONTROLLABLE V <sub>T</sub> )  GOOD SPEED/POWER PERFORMANCE  TTL COMPATIBILITY POSSIBLE  IMPROVED PACKING DENSITY POSSIBLE  DEPLETION LOADS POSSIBLE | DISADVANTAGES  ONLY 2 LEVELS INTERCONNECT (Si GATE = 2½)                    |

| SILICON GATE PRO                                                                                                                                                                                                             | DCESS (P-CHANNEL)                                                           |

| ADVANTAGES  TTL COMPATIBILITY  2½ LEVEL INTERCONNECT CAPABILITY  HIGHER DENSITY THAN METAL GATE  BETTER SPEED/POWER THAN NITRIDE (SELF ALIGNED GATE)                                                                         | DISADVANTAGES  CONSIDERABLY MORE COMPLEX THAN METAL GATE  HIGH PROCESS COST |

#### **N-CHANNEL SILICON GATE**

#### **ADVANTAGES**

- EXCELLENT SPEED/POWER PERFORMANCE

- 2½ LEVEL INTERCONNECT

- HIGHER PACKING DENSITY THAN P-CHANNEL SI GATE OR METAL GATE

- TTL COMPATIBLE

- SINGLE RAIL (5V) OPERATION POSSIBLE (DEPLETION LOADS)

#### DISADVANTAGES

- MORE COMPLEX PROCESS THAN METAL GATE

- LOW FIELD THRESHOLD

channel are electrons, which have a higher mobility than holes, giving rise to a much better speed/power performance. The advantages and disadvantages of this process are shown in Table 3.

So far, various methods of fabricating MOSFETS have been described with some of the basic parameters highlighted to justify the existence of all these processes to non-process engineers. There are other factors which are also important, such as the transconductance (gm) which is defined <sup>2</sup> as

$$g_m = \frac{\partial I_D}{\partial V_G} \Big|_{V_D}$$

If the g<sub>m</sub> per unit area is higher for a given process, then if all other conditions are equal, the device will operate at a faster speed. Alternatively, the size of the device can be reduced, without losing performance.

An expression from which gm may be derived is:-

$$g_{\rm m} = \frac{\mu.\epsilon_{\rm O}.\epsilon_{\rm OX}.W}{t_{\rm OX}.L} \times (V_{\rm G} - V_{\rm T})$$

where W and L are the device dimensions shown in Figure 1. From this expression it can be seen that with the nitride process, for example, where  $C_{\rm OX}$  is increased, then the  $g_{\rm m}$  of the device is increased.

#### COMPLEMENTARY MOS PROCESS

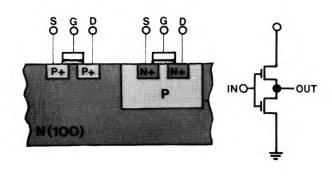

The MOS designer has available all these different processing techniques from which to choose the most suitable for the particular application. If the completed MOS device is not going to be used with any other type of logic family, then there is no need to strive to make the device, for example, TTL compatible. There is, however, another design technique which is gaining acceptance as being a major technology in MOS integrated circuit design. This is not so much a new process, but the concept of using both n channel and p channel devices in complementary pair configuration on the same chip, forming the basis of the Complementary MOS process. Figure 8 shows an n

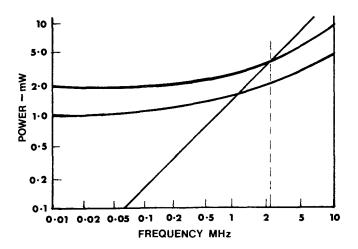

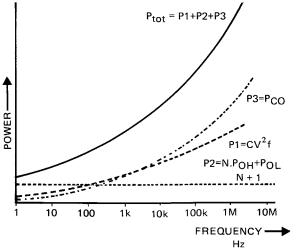

channel and a p channel FET both on the same n type substrate. To implement the n channel device (the righthand FET) it is necessary to first diffuse a 'tub' of p type material, which not only takes up considerable chip area, but also substantially increases the number of process steps required. The major advantage of this complementary circuit design technique is that very low power dissipation may be achieved for a given function. The two devices in Figure 8 are shown in the schematic diagram, on the righthand side, connected as an inverter. The gates are connected together, and hence when a logic 'high' level is applied to the gate, the n channel device will turn 'on' and the p channel device will turn 'off'. When a logic 'low' is applied at the input, the opposite will occur. Thus at no time is there a path for dc current to flow through the circuit. The only current that does flow is a transient during the change over time from 'high' to 'low' or 'low' to 'high' state. This gives rise to very low power dissipation at low operating frequencies, which is very useful for battery operated equipment, etc. However, as the frequency of operation increases, the power dissipation due to the current transient at changeover becomes more significant, and at approximately 2 MHz, the dissipation is equal to that of Schottky Low Power TTL (Series 74LS). This is shown in Figure 9.

FIGURE 8. Basic Complementary MOS Construction

FIGURE 9. Comparison of CMOS and Bipolar Power Consumption with Operating Frequency

A summary of the salient features of all these processes is shown in the comparison chart of Table 4. As the process complexity increases down the table, so the process economy decreases. However, improvements in

manufacturing techniques tend to keep pace with the increasing process complexity, and make these more sophisticated processes a viable proposition.

#### **CHARGE COUPLED DEVICES**

There is a new concept in MOS circuit design which does not use the FET as the basic element. Instead it relies on charge being driven from one stage of the circuit to the next stage by the electric field under a pattern of conductors on the surface of the device. By using multiphase clocks, the charge on one stage may be stepped through successive stages, giving rise to a very simple shift register structure. This is the principle of operation of Charge Coupled Devices (CCD).

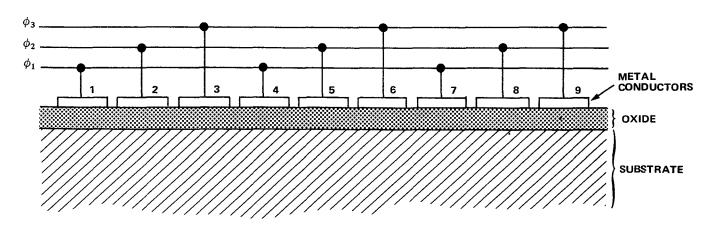

Figure 10 shows a cross section through a CCD structure. The metal electrodes are connected to the three phases  $(\phi_1, \phi_2, \phi_3)$ , of the system clock as shown. The bias applied to electrodes 1, 4, 7, etc. by clock  $\phi_1$ , causes a 'well' in the depletion layer in the surface of the silicon substrate. Similarly, phases  $\phi_2$  and  $\phi_3$  cause 'wells' under

|                         | SPEED POWER | PROCESS<br>ECONOMY | TTL<br>COMPATIBILITY | PACKING<br>DENSITY | SPECIAL<br>FEATURES |

|-------------------------|-------------|--------------------|----------------------|--------------------|---------------------|

| STANDARD<br>THICK OXIDE |             | ••••               |                      | •                  |                     |

| NITRIDE                 | •           | •••                | ••                   | •                  |                     |

| ION<br>IMPLANT          | ••          | •••                | •••                  | ••                 |                     |

| SILICON GATE<br>(P—CH)  | ••          | ••                 | ••                   | •••                |                     |

| SILICON GATE<br>(N-CH)  | •••         | ••                 | •••                  | ••••               | HIGH SPEED-<br>RAMs |

| COMPLEMENTARY           | ••••        |                    | ••••                 |                    | ULTRA LOW<br>POWER  |

Table 4. Process Comparison

THE MORE ●● THE BETTER

FIGURE 10. Cross Section Through CCD Structure

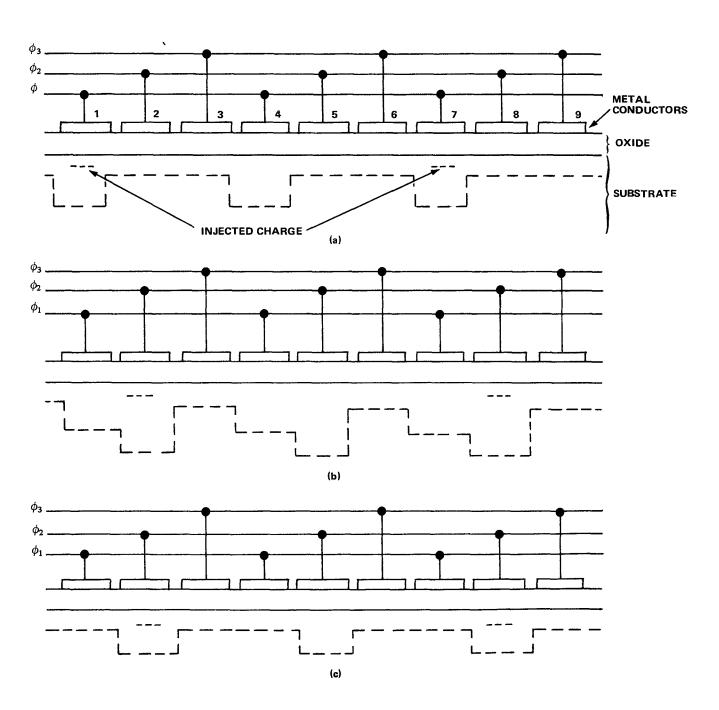

electrodes 2, 5, 8 etc. and 3, 6, 9 etc. As illustrated in Figure 11, a charge of minority carriers is injected into the depletion region at the beginning of the device (represented by...) and is propagated along the device by the action shown. In Figure 11(a), charge has been injected into the potential wells under the electrodes. In Figure 11(b), a larger bias has been applied to the  $\phi_2$  electrodes, causing a deeper potential 'well' under them. The stored charge then moves towards the deeper 'well'. Figure 11(c) shows that the  $\phi_1$  bias has been removed, and the charge remains isolated in the  $\phi_2$  'wells'. By applying a suitable sequence of potentials to the electrodes, the charge can be propagated along the full length of the device.

The stored charge constitutes the signal, and since, in theory, the full charge is transferred from stage to stage, operation can be digital or analogue. Hence this technology is suitable for digital shift registers, and analogue delay lines. Another field of application is for light image sensing, since light falling on the chip will modify the charge stored at each node according to the light intensity at that point. The construction geometry of these devices is extremely simple and gives rise to very high packing density of storage nodes. This, coupled with the small number of process steps required, makes CCD potentially a very low cost process, and the first devices using this technology are just beginning to appear.

FIGURE 11. CCD Operation

#### REFERENCES

- 1. The Engineering Staff of A.M.I., M.O.S. Integrated Circuits, Van Nostrand, 1972.

- 2. Robert H. Crawford, MOSFET in Circuit Design, Texas Instruments Electronic Series, McGraw Hill, 1967.

#### **II MOS IN TERMINALS**

The functions performed by terminals are data processing operations such as entry, buffering, transmission/reception and the display of the digital data. MOS/LSI is particularly well suited for these functions.

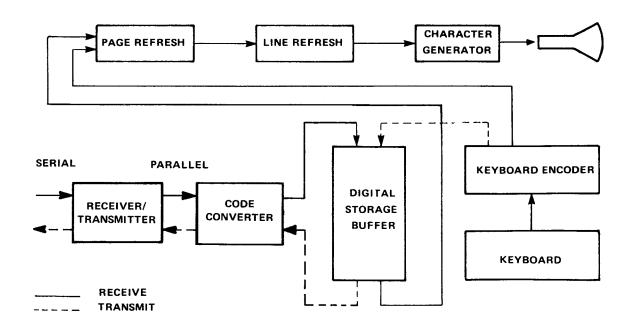

Figure 1 shows a block diagram of a typical terminal system.

Relative to data processing times, the communications link varies from very slow to slow. Teletype grade lines are generally used for asynchronous transmissions and are limited to about 120 characters per second. Voice grade lines are used for synchronous data transmission and are good for about 600 characters per second. Wideband lease lines are available for up to 1200 characters per second. The modem on the end of the communication line prepares the data for transmission down a serial data channel.

#### RECEIVER/TRANSMITTER

Serial data from the line is accepted and translated to parallel data for use in the terminal. For transmission, the parallel data is converted to serial.

A device or subsystem, which is designed to perform these functions, is known as a Universal Asynchronous Receiver Transmitter (UART). An example of such a subsystem made using MOS technology is the TMS 6011 JC/NC UART.

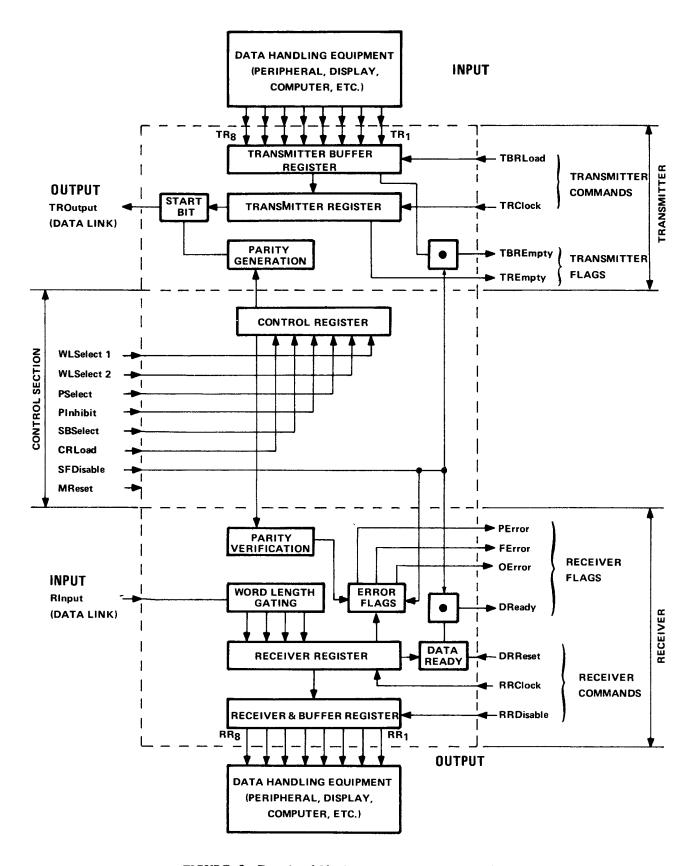

Figure 2 shows a functional block diagram of the TMS 6011 JC/NC. The receiver section of this device will accept serial data from the transmission line and convert it to parallel data. The serial word will have start, data and stop bits. Parity may be generated and verified. The receiver section will validate the received data transmission by checking the proper parity, start and stop bits and convert the data to parallel. The transmitter section will accept parallel data, convert it to serial form and generate the start, parity, and stop bits. Receiver and transmitter sections are separate and the device can operate in full duplex mode.

To allow maximum flexibility of operation, the unit has also been designed as a fully programmable circuit. The device can operate either in full duplex (simultaneous transmission and reception) or in half duplex (alternate transmission and reception). The data word may be externally selected to be 5, 6, 7, or 8 bits long. The baud rate is externally selected by the clock frequency, which can vary between 0 and 160 Hz. The parity, which is generated in the transmit mode and verified in the receive mode, can be selected as either odd or even. It is also possible to disable the parity bit by inhibiting the parity generation and verifi-

FIGURE 1. Block Diagram of a Typical Terminal System

FIGURE 2. Functional Block Diagram of TMS 6011 JC/NC

cation. The stop bit can be selected as either a single- or double-bit stop. Static logic is used to maximize flexibility of operation and to simplify the task of the user. The data holding registers are static and will hold a data word until it is replaced by another word.

To allow for a wide range of possible configurations, triple-state push-pull buffers have been selected on all outputs except serial transmission and TREmpty flag. They allow the wire-OR configuration.

The subsystem can be used in a wide range of data handling equipment such as Modems, peripherals, printers, data displays, and minicomputers. By taking full advantage of the latest circuit design and processing techniques it has been possible to implement the entire transmit, receive, and format function necessary for digital data communication, in a single package, avoiding the cumbersome circuitry previously necessary.

P-channel enhancement-mode low-threshold technology permits the use of standard power supplies (+5 V, -12 V) as well as direct TTL/DTL interface. No external components are needed.

The operation of this device can be best understood by visualizing the subsystem as three separate sections: 1) transmitter, 2) receiver, and 3) common control. The transmitter and receiver sections are independent while the control section directs both receive and transmit.

#### **Transmitter Section**

The transmitter section will accept data in parallel form, serialize it, format it, and transmit it in serial form. Parallel input data is received on the transmitter buffer register data inputs TR1 through TR8. Serial output data is transmitted on the TROutput terminal. Input data is stored in the transmitter buffer register. A logic 'low' on the TBRLoad command terminal will load a character in the transmitter buffer register. If words of less than 8 bits are used, only the least significant bits are accepted. The character is justified into the least significant bit, TR1.

The data is transferred to the transmitter register when TBRLoad terminal goes from 'low' to 'high'. The loading of the transmitter register is delayed if the transmitter section is presently transmitting data. In this case the loading of the transmitter register is delayed until the transmission has been performed.

Data is transmitted in serial form on the TROutput terminal. The data is clocked out by TRClock. The clock rate is 16 times faster than the data rate. The data format is as follows: start bit, data, parity bit, stop bits (1 or 2). Start bits, parity bits, and stop bits are generated by the subsystem. When no data is transmitted the output TROutput sits at a logic 'high'. The start of the transmission is defined as the transition of TROutput from a logic high to a logic 'low'

Two flags are provided. A logic 'high' on the TBREmpty flag indicates that a word has been transferred to the transmitter register and that the transmitter buffer

register is now ready to accept a new word. A logic 'high' on the TREmpty flag indicates that the transmitter section has completed the transmission of a complete word including stop bits. The TREmpty flag will sit at a logic 'high' until the start of transmission of a new word. Both transmitter buffer register and transmitter registers are static and will perform dc storage of data.

#### **Receiver Section**

The data is received in serial form on the receiver input RInput. The data is presented in parallel form on the eight data outputs RR1 through RR8. RInput is the data input terminal. The data from RInput enters the receiver register at a point determined by the character length, the parity, and the number of stop bits. RInput must be maintained high when no data is being received. The data is clocked through the RR clock. The clock rate is 16 times faster than the data rate. Data is transferred from the receiver register to the receiver buffer register and appears on the 8 RR outputs. The MOS output buffers used for the eight RR terminals are triple-state push-pull output buffers which permit the wire-OR configuration through use of the RRDisable terminal. When a logic 'high' is applied to RRDisable, the RR outputs are floating. If the word length is less than 8 bits, the most significant bits will be at a logic 'low'. The output word is right justified. RR1 is the least significant bit and RR8 is the most significant bit.

A logic 'low' applied to the DRReset terminal resets the DReady output to a logic 'low'. Several flags are provided in the receiver section. There are three error flags (parity error, framing error and overrun error) and a data-ready flag. All status flags may be disabled through a logic high on the SFDisable terminal.

A logic 'high' on the PError terminal indicates an error in parity. A logic 'high' on the OError terminal indicates an overrun. An overrun occurs when the previous word was not read, i.e., when the DReady line was not reset before the present data was transferred to the data receive holding register. A logic 'high' on the DReady terminal indicates that a word has been received, stored in the receiver buffer register and that the data is available on outputs RR1 through RR8. The DReady terminal can be reset through the DRReset terminal.

#### **Common Control Section**

The common control section directs both the receiver and the transmitter sections. The initialization of the subsystem is performed through the MReset terminal. The Master Reset is strobed to a logic 'high' after power turn-on to reset all registers and to reset the serial output line to a logic 'high'. All status flags (parity error, framing error, overrun error, data ready, transmitter buffer register) are disabled when the SEDisable is at a logic 'high'. When disabled, the status flags float. (3 state buffers in 3rd state). The number of bits per word is controlled by the WLSelect 1 and WLSelect 2 lines. The word length may be 5, 6, 7, or 8 bits.

The selection is as follows:

| WORD LENGTH | WLS1 | WLS2 |

|-------------|------|------|

| 5           | Low  | Low  |

| 6           | Low  | High |

| 7           | High | Low  |

| 8           | High | High |

The parity to be checked by the receiver and generated by the transmitter is determined by the PSelect line. A logic 'high' on the PSelect line selects even parity and a logic 'low' selects odd parity. The parity will not be checked or generated if a logic 'high' is applied to PInhibit; in this case the stop bit or bits will immediately follow the data bit. When a logic 'high' is applied to PInhibit, the PError status flag is brought to a logic 'low', indicating a no-parity error because parity is disregarded in this mode. To select either one or two stop bits, the SBSelect terminal is used. A logic 'high' on this terminal will result in two stop bits while a logic 'low' will produce only one. To load the control bits (WLSelect 1, WLSelect 2, PSelect, PInhibit, SBSelect) a logic 'high' is applied to the CRClock terminal. This terminal may be strobed or hardwired to a logic 'high'.

#### **CODE CONVERTERS**

A terminal system is designed to operate with one code, USASCII for example. For it to use information from sources using other than USASCII code, Selectric for example, a code converter must be included in the terminal system.

Codes are used to transfer information over data links between such equipment as peripherals, terminals, and computers.

A code word is a binary word that represents either an alphanumeric character or a command.

For instance:

The letter A is represented

by 1000001 in USASCII code

The command DEL (delete)

is represented by 1111111 in USASCII code

Depending on the code used, the size of the alphabet (characters and commands) may vary between 64 and 256. The number of bits in a common alphanumeric code word may vary between 6 and 8.

Many different codes are commonly used in data processing equipment. Equipment is built for a specific code and for that code only. To build a system from several pieces of data processing gear using different codes, it is necessary to convert codes.

MOS ROMs are ideally suited for code conversion. The code to be translated is fed at the input of the ROM and the output of the ROM represents the translated input code.

The most popular ROM size for code converter applications is the 2048-bit organized as 256 words x 8 bits. A ROM this size will handle all the usual codes for data transmission. (The most cumbersome code is the EBCDIC

with room for 256 characters of 8 bits.) Because most codes use a 7-bit word and a 128-character alphabet, it is. often possible to make a 2048-bit ROM, organized as 256 words of 8 bits, work both ways and not only translate code A into code B but also, upon command, translate B into A.

#### **Codes and Their Definitions**

An almost endless variety of codes exists for data transmission. This causes a problem because users have difficulty in agreeing on a code, and when they do they often modify it slightly for their own purposes. Some of the most popular codes are:

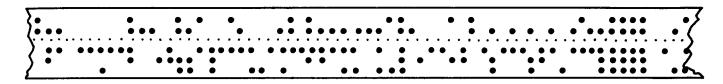

Hollerith: Hollerith is used on punched cards. It is a 12-bit code with a very large alphabet (256 characters and commands). This is the code used on the 80-column punched cards as shown in Figure 3. A normal card punch machine will only punch 64 characters. Because of these limitations, the Hollerith code is not generally used for data transmission.

BCD Code (Binary Coded Decimal): BCD is a very simple code with 64 characters of 6 bits. This is the code used with the new SYSTEM 3 IBM punched cards (96 columns, 6 bits/column).

EBCDIC (Extended Binary-Coded-Decimal Interchange Code): EBCDIC is a widely-used code with room for 256 characters of 8 bits as shown in Figure 4.

USASCII (USA Standard Code for Information Interchange): USASCII is the only code on which seems to agree with everybody throughout the world. The code uses 128 characters, 7 bits per character. Often, users are not interested in the full 128 characters and need only the 64 characters subset boxed within the table in Figure 5. In this case, only 6 bits per character are needed, and either b7 or b6 may be dropped.

The international version of USASCII is called ISO. The 7-bit ISO is almost identical to the USASCII, except that certain characters may be replaced by national characters (£ instead of \$ for instance). The 6-bit ISO is obtained by dropping b<sub>6</sub>.

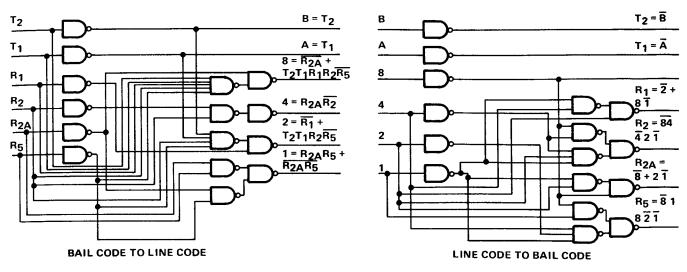

Selectric Line Code: Because IBM Selectric Typewriters are commonly used as terminals, several Selectric codes are being used. The most common is the IBM Correspondence Selectric Line Code. It is a 7-digit 128-character code. A certain amount of logic is necessary to go from Selectric Line Code to Selectric Bail Code shown in Figure 6.

Baudot Code: A very simple 32-character 5-bit code, the Baudot is used mainly in teletype equipment, illustrated in Figure 7.

```

BCDEFGHIJKLMNOPQRSTUVWXYZ 1234567890 @g*<-/

1 2 1 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 20 29 30 31 32 33 34 35 36 37 30 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 67 68 69 70 71 77 73 74 75 76 77 78 79 80

1 2 3 4 5 6 7 6 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

```

FIGURE 3. Card with Hollerith Code

|      | 5 —       |    |         |         | <b>→</b>            | 0 0 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>1 | 1<br>0<br>0 | 1<br>0<br>1 | 1<br>1<br>0 | 1 1 |

|------|-----------|----|---------|---------|---------------------|-----|-------------|-------------|-------------|-------------|-------------|-------------|-----|

| Bits | <b>b4</b> | b3 | b2<br>↓ | b1<br>↓ | Column<br>→<br>Row↓ | 0   | 1           | 2           | 3           | 4           | 5           | 6           | 7   |

|      | 0         | 0  | 0       | 0       | 0                   | NUL | DLE         | SP          | 0           | @           | Р           | ,           | р   |

|      | 0         | 0  | 0       | 1       | 1                   | son | DC1         | 1           | 1           | Α           | Q           | а           | q   |

|      | 0         | 0  | 1       | 0       | 2                   | STX | DC2         | ,,          | 2           | В           | R           | b           | r   |

|      | 0         | 0  | 1       | 1       | 3                   | ETX | DC3         | #           | 3           | С           | S           | С           | s   |

|      | 0         | 1  | 0       | 0       | 4                   | EOT | DC4         | \$          | 4           | D           | Т           | d           | t   |

|      | 0         | 1  | 0       | 1       | 5                   | ENQ | NAK         | %           | 5           | E           | C           | е           | u   |

|      | 0         | 1  | 1       | 0       | 6                   | ACK | SYN         | &           | 7           | F           | >           | f           | v   |

|      | 0         | 1  | 1       | 1       | 7                   | BEL | ETB         | ,           | 7           | G           | ٧           | g           | w   |

|      | 1         | 0  | 0       | 0       | 8                   | BS  | CAN         | (           | 8           | Н           | ×           | h           | х   |

|      | 1         | 0  | 0       | 1       | 9                   | нт  | EM          | )           | 9           | 1           | Y           | i           | У   |

|      | 1         | 0  | 1       | 0       | 10                  | LF  | SUB         | *           | :           | J           | Z           | j           | z   |

|      | 1         | 0  | 1       | 1       | 11                  | ۷Ť  | ESC         | +           | ;           | к           | [           | k           | *   |

|      | 1         | 1  | 0       | 0       | 12                  | FF  | FS          | ,           | <           | L           | ١           | l           |     |

|      | 1         | 1  | 0       | 1       | 13                  | CR  | GS          | -           | =           | М           | 1           | m           | }   |

|      | 1         | 1  | 1       | 0       | 14                  | so  | RS          |             | >           | 2           | ٨           | n           | ~   |

| i    | 1         | 1  | 1       | 1       | 15                  | SI  | US          | /           | 7           | 0           | -           | 0           | DEL |

FIGURE 5. USA Standard Code for Information Interchange (USASCII)

| b0       | 3 - |         |    |   | •               | 000 | 0 0 1 | 0 0 1 | 0 1 | 0 1 0 | 0 1 0 1 | 0 1 0  | 0 1 1 | 100 | 0 0 1 | 1 0 1 | 1 0 1 | 1 0 0 | 1 0 1 | 1 1 0 | 1<br>1<br>1 |

|----------|-----|---------|----|---|-----------------|-----|-------|-------|-----|-------|---------|--------|-------|-----|-------|-------|-------|-------|-------|-------|-------------|

| 5        |     | ţ<br>bs | b6 |   | Column<br>Row ↓ | 0   | 1     | 2     | 3   | 4     | 5       | 6      | 7     | 8   | 9     | 10    | 11    | 12    | 13    | 14    | 15          |

|          | 0   | 0       | 0  | 0 | 0               | NUL | DLE   | DS    |     | SP    | &       |        |       |     |       |       |       |       |       |       | 0           |

|          | 0   | 0       | 0  | 1 | 1               | SOH | DC1   | sos   |     |       |         |        |       | а   | J     |       |       | А     | J     |       | 1           |

|          | 0   | 0       | 1  | 0 | 2               | STX | DC2   | FS    | SYN |       |         |        |       | b   | k     | s     |       | В     | К     | S     | 2           |

|          | 0   | 0       | 1  | 1 | 3               | ETX | тм    |       |     |       |         |        |       | С   | •     | t     |       | С     | L     | Т     | 3           |

|          | 0   | 1       | 0  | 0 | 4               | PF  | RES   | ВҮР   | PN  |       |         |        |       | d   | m     | u     |       | D     | М     | U     | 4           |

|          | 0   | 1       | 0  | 1 | 5               | нт  | NL    | LF    | RS  |       |         |        |       | е   | n     | v     |       | E     | N     | ٧     | 5           |

|          | 0   | 1       | 1  | 0 | 6               | LC  | BS    | EOB   | UC  |       | ,       |        |       | f   | 0     | w     |       | F     | 0     | w     | 6           |

| ĺ        | 0   | 1       | 1  | 1 | 7               | DL  | IL    | PRE   | EOT |       |         |        |       | g   | р     | ×     |       | G     | Р     | ×     | 7           |

|          | 1   | 0       | 0  | 0 | 8               |     | CAN   |       |     |       |         |        |       | h   | q     | У     |       | Н     | Q     | Υ     | 8           |

|          | 1   | 0       | 0  | 1 | 9               |     | EM    |       |     |       |         |        |       | t   | r     | z     |       | ı     | R     | Z     | 9           |

| <u> </u> | 1   | 0       | 1  | 0 | 10              | SMM | сс    | SM    |     | ¢     | 1       |        |       |     |       |       |       |       |       |       |             |

|          | 1   | 0       | 1  | 1 | 11              | VT  |       |       |     |       | \$      | ,      | #     |     |       |       |       |       |       |       |             |

|          | 1   | 1       | 0  | 0 | 12              | FF  | IFS   |       | DC4 | <     | *       | %      | @     |     |       |       |       |       |       |       |             |

| <u>[</u> | 1   | 1       | 0  | 1 | 13              | CR  | IGS   | ENQ   | NAK | (     | )       | Allina | ,     |     |       |       |       |       |       |       |             |

| L        | 1   | 1       | 1  | 0 | 14              | so  | IRS   | ACK   |     | +     | ;       | >      | =     |     |       |       |       |       |       |       | ~           |

| Į        | 1   | 1       | 1  | 1 | 15              | SI  | IUS   | BEL   | SUB | ı     |         | 7      | ,,    |     |       |       |       |       |       |       |             |

FIGURE 4. Extended Binary-Coded-Decimal Interchange Code (EBCDIC)

FIGURE 6. Conversion Necessary to go from Selectric Line Code to Selectric Bail Code and Vice-Versa.

FIGURE 7. Example of Baudot Code

Other common codes include: IBM System 360 8-bit code, Honeywell 64 characters, GE 64 characters, UNIVAC 64 characters, Burroughs 64 characters, and IBM 47 characters.

#### **Practical Implementation**

The ROMs are very adaptable to code conversion and can be programmed for this application. Because of the wide variations within a code family, in each case a truth table of the codes to be converted is needed before the device can be implemented.

The particular device is determined by the number of codes, the number of characters in a code, and the number of bits in a code word, e.g. TMS 4103 JC/NC ROM has 5 codes, 64 characters and 7 bits.

#### **DIGITAL STORAGE BUFFERS (DSBs)**

It is often necessary to buffer information between the transmission line and a terminal. The rate of data transmission sometimes may be different from the rate of display. Such a function may be accomplished through storage registers but in this case the data is not always available at the output. A good solution for this problem is the use of an organized digital storage buffer also called Silo Buffer.

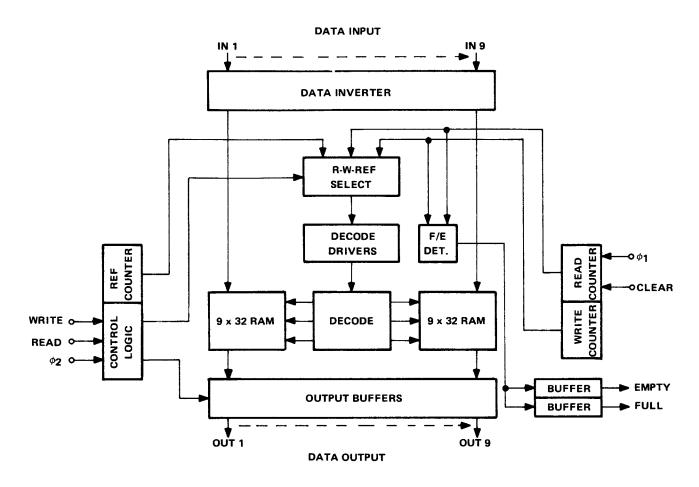

An example of such a device is the TMS 4024 JC/NC whose functional block diagram is shown in Figure 8. This is a first-in first-out digital storage buffer that will store up to 64 nine-bit words. The major components of the device include a 9 x 64 dynamic random access memory (RAM),

three shift counters, and comparison and control logic. A RAM-type organization results in zero ripple-through time. Data written at the input when the register is empty is immediately available on the output. The input and output are completely independent of each other. Input and output timing can be dependent on the clock timing (synchronous mode) or can be operated independently (asynchronous mode). The dynamic RAM requires two-phase continuous clocking at a specified minimum frequency. The clocks can be driven directly from TTL logic. Again low-threshold, thick-oxide, MOS p-channel enhancement-mode technology is employed to allow interfacing with TTL/DTL circuits without external components.

The device will process data at any desired rate from dc to one-half the continuous clock frequency. At a nominal 500 kHz clock rate the maximum data rate is 250 kHz. Data is processed in parallel format, word by word. Write and read commands are used to enter and dump data. Data entry and dump may be either synchronous or asynchronous (in relation to the clock). Asynchronous operation is limited to data rates of less than one-third of the clock frequency. A positive-going edge on the read or write line is recognised as a command. It must occur while  $\phi 1$  is 'high' for synchronous operation. A write command causes the data present on the input to be transferred into the buffer. Data-in must be true for the periods during which φ2 is 'low'. For asynchronous operation the Data-in must be true for two periods after the write command is given, because the write command may be given at any time in relation to the clock. If both the read and write lines are brought to a logic 'high', the device is disabled and the data

FIGURE 8. Functional Block Diagram of TMS 4024 JC/NC Digital Storage Buffer

FIGURE 9. Digital Storage Buffers Cascaded

outputs are floating. The data present in the register is conserved while the chip is disabled. A Clear command is provided to clear all contents of the digital storage buffer. When the Clear line is brought to a logic 'high', it invalidates all other commands. Completion of a Clear operation is detected by a logic 'high' on the 'Empty' status output. Status outputs (Empty and Full) are provided to indicate the state of the register and avoid invalid operation. A logic 'high' on the Full status output invalidates Write commands and a logic 'high' on the Empty status output invalidates Read commands.

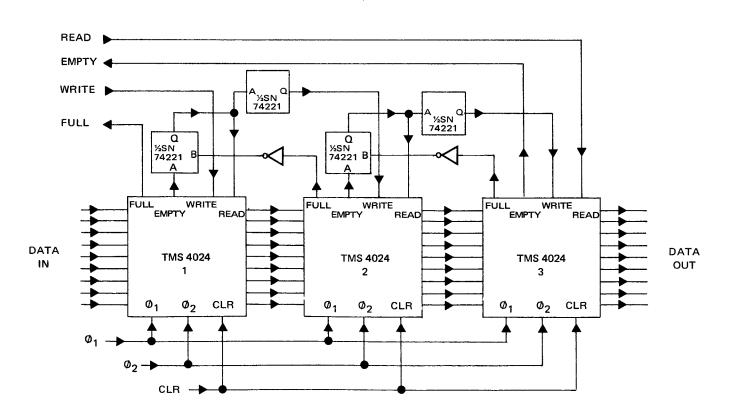

It can be 'cascaded' to form multiples of 64 words (x 9 bits) by using the arrangement as shown in Figure 9. Here the Empty output of device 1 is connected to the A input of the first monostable. The Full output of device 2 is inverted and connected to the B input of the monostable as an inhibit function. The O output of the monostable is connected to the Read input of device 1 and the Write mono. of device 2. This may be repeated for as many stages as required. The example shown is of three stages giving 192 words of 9 bits. Assuming the sequence begins with a clear command, all Empty flags will be 'high' and Read 'low'. The first Data word is written into device 1 by taking its Write input to a logic '1' level, for a maximum of one clock period. The Empty output of device 1 goes to a logic '0' and triggers the first monostable, to give a pulse of approximately one clock period. This causes the data to be read out of device 1 and written into device 2. In this way the data 'ripples' through all the devices, and is eventually stored in the last device. When the last device is full, the Full output changes to a logic '1' level. This puts a logic '0' on the B input to the monostable of the previous stage, thus inhibiting any further data transfer into the last device until some data is read out of it. The Full output will then return to logic '0'. It should be realised that it takes several

clock cycles for data to ripple through all the devices from the time it is entered into the first device, until it is available at the output of the last device. The number of clock cycles obviously depends upon the number of stages.

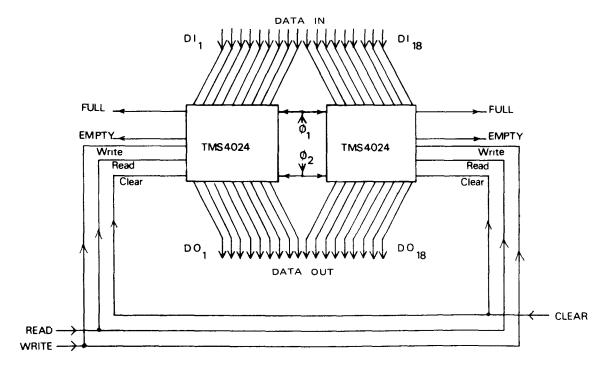

To expand the memory in parallel, the simple arrangement shown in Figure 10 can be used to extend the number of bits.

#### CHARACTER GENERATORS

MOS ROMs offer an extremely versatile approach to character generation which can be used advantageously in terminal systems.

They are programmed during manufacture to store data which may be read out on command to create the image of letters, numerals, and symbols in some sort of display system such as a cathode-ray-tube (CRT), array of lamps, or matrix-type printer. Each device can store more than 2000 bits of data (enough for 64 characters in one device) and includes addressing and decoding circuitry. The MOS circuitry is static rather than dynamic. No clocking is required.

Speed performance of static MOS ROMs is adequate for both low-speed applications and high-speed CRT data displays. Their small size and low power consumption in addition to their low cost make them attractive replacements for existing character generators in many display systems.

#### **Fundamentals**

Tube-type character generators take various forms. Some like the *monoscope* consist of an electron gun, electrostatic deflection plates, and a target on which the characters are formed. In a character generator of this type,

FIGURE 10. Digital Storage Buffers Paralleled

an incoming digital code specifying the character to be displayed is first converted to deflection voltages. The electron beam is deflected accordingly to the appropriate target location which contains a metallized image of the desired character. This beam then scans the target in synchronism with the beam in a cathode-ray tube (CRT) display. Secondary emission from the metal image provides a video signal for the CRT, reproducing the character on its face.

In some CRT displays the character generation is performed within the CRT itself. In this case, a thin metal stencil with character shapes etched through is used to extrude the beam to the desired character shape. After leaving the gun, the beam is deflected to a character location on the stencil, passes through the stencil, and is converged to the tube axis. It is then deflected again, this time to a position on the CRT face, where the shaped beam causes the selected character to appear.

With these tube-type character generators, the digital code specifying a character must first be converted to positional information before character selection can be achieved. On the other hand, digital character generators use a more direct approach than the tube type. Digital types generally consist of a read-only memory (ROM) in which a given input code produces a digital output describing a character specified by the user. This digital output is then converted into a visual image as described below. The use of ROMs for character generation eliminates the need for bulky tubes or special-purpose CRTs. They can also be used in non-CRT applications such as billboard displays and matrix type printers.

#### **Practical Implementation**

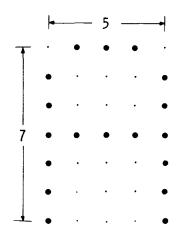

There are many different output code schemes that might be designed into an ROM character generator. However, the dot matrix output format is perhaps the easiest to visualize and use. Consider a 5 X 7 dot matrix used to present the letter A as shown in Figure 11. If each of

FIGURE 11. Letter "A" in 5 X 7 Dot Matrix

the dot positions is a lamp, then the dots in the letter A are on lamps, while the others are off. The on lamps correspond to logical '1' outputs of an ROM with a 35-bit output word, while the off states correspond to a logical '0' output. In CRT displays, the same logical two-state output can be used to blank and unblank the beam. A sequential output from an ROM is generally more desirable than 35 parallel outputs because video information can be supplied as the beam is moving.

In order to use a ROM to generate a variety of characters a large ROM is necessary. For most display applications 32 characters is a bare minimum. A 64 character alphabet corresponds to a wider range of applications. Certain data display applications will necessitate as many as 96 or even 128 characters. The size of the dot matrix used depends on the definition needed for the display. Most human factor experts agree on the fact that a 7 X 5 character font presents enough definition for most applications while a 7 X 9 character font is much more eye pleasing. A 7 X 9 font permits, for instance, a good representation of complex characters such as the money sign and the ampersand. The total number of bits needed is as follows:

| 32 characters 7 X 5  | 1120 bits |

|----------------------|-----------|

| 64 characters 7 X 5  | 2240 bits |

| 128 characters 7 X 5 | 4480 bits |

| 64 characters 7 X 9  | 4480 bits |

| 128 characters 7 X 9 | 8960 bits |

It would be costly and awkward to implement such a large number of bits through diode or classical bipolar logic. Core memories require special drive and sense circuits and are difficult to modify for different customer character requirements. Therefore in recent years, a viable alternative, especially as far as character generation is concerned, has been ROMs. The cost per bit is low, and likely to decrease further, and there are also savings in weight, size and power consumption.

Two examples of ROMs suitable for character generation are the TMS 2501 JC/NC with a row output format, and the TMS 4103 JC/NC with a column output.

Both these devices have been designed with a static logic source which permits the simplest system design and eliminates the need for the special clocking circuits required by dynamic MOS configuration.

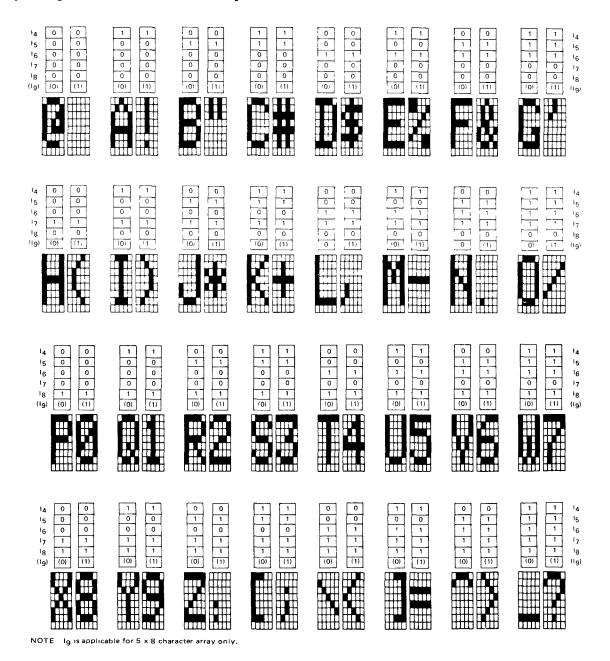

The TMS 2501 JC/NC series allow the user to display one out of 64 characters on a 7 x 5 matrix. Rather than having all outputs available simultaneously only one row of the dot matrix is available at a time. By addressing the 3 row select lines as shown in Figure 12 the corresponding row is displayed on the output. The direct character font of the TMS 2501 is represented in Figure 13.

The 3 bit row address input is internally decoded in 8 row select inputs. Only 7 of them will be used for most display applications. Such a 'row output' device will find its application in raster scan displays (TV monitor type displays).

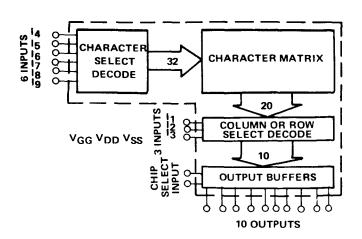

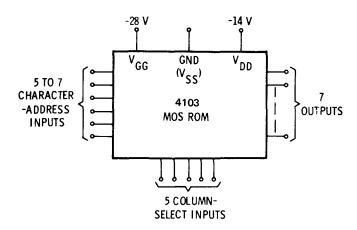

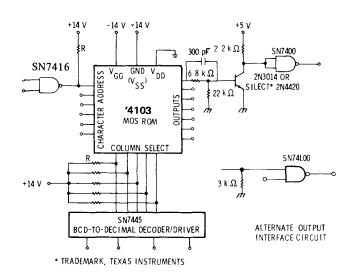

The TMS 4103 JC/NC device has been designed for use in CRT and billboard displays.

Rather than having all outputs available simultaneously, only one column of the dot matrix is available at a time. By driving one of the five column-select inputs shown

FIGURE 12. Functional Block Diagram of TMS 2501 JC/NC ROM

FIGURE 13. TMS 2501 JC/NC Character Font

in Figure 14, the corresponding column is made available at the output. Thus this character generator accepts USASCII input coding and provides 64 standard characters in a  $5 \times 7$  dot array, and an entire character can be obtained in less than  $1.5 \mu s$ .

FIGURE 14. Pin Functions of MOS ROM TMS 4103

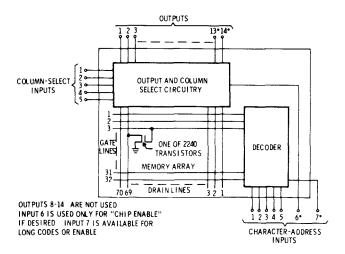

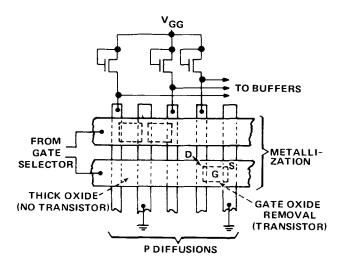

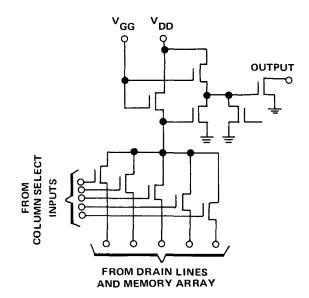

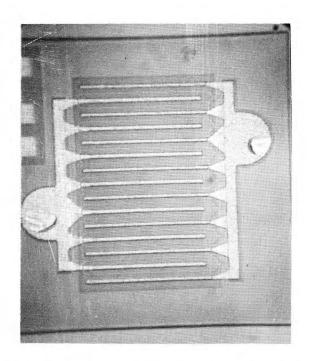

The memory matrix of the 4103 device consists of 2240 P-channel MOS devices arranged in a 32 X 70 array. As shown in Figure 15, the 32 horizontal lines drive the MOSFET gates, while their drains are connected to one of the 70 output lines. Every device has its source grounded. When one of the 32 gate lines is driven negative, those devices which have their gate connected are turned on, pulling down the voltage of the corresponding output line. Whether a gate is connected or not is determined by mask programming, with a connected gate corresponding to a dot in the output format.

The block diagram in Figure 15 shows the interconnection of all circuits in an ROM of the TMS 4103 type: the decoder, memory array, and output selection circuits. In order to arrange the 64 characters with a 5 X 7

FIGURE 15. Functional Diagram of all Circuits within an MOS ROM of the TMS 4103

matrix, two characters are encoded on each of the 32 gate lines. Five of the six bits (or six of seven) in the input code are used to drive the decoder, with the sixth bit, as shown in Figure 15, connected to the output buffer to choose between the two characters.

Programming of the MOS ROMs is done at the second-oxide-removal processing stage. Unused transistors have a layer of thick oxide over their gate regions (Figure 16). The other masks used during the process are the same for all the devices in one series. Fully computerised methods

FIGURE 16. An MOS Transistor can be Either Constructed or Omitted by Growing Either a Thin-Gate Oxide or a Thick-Gate Oxide

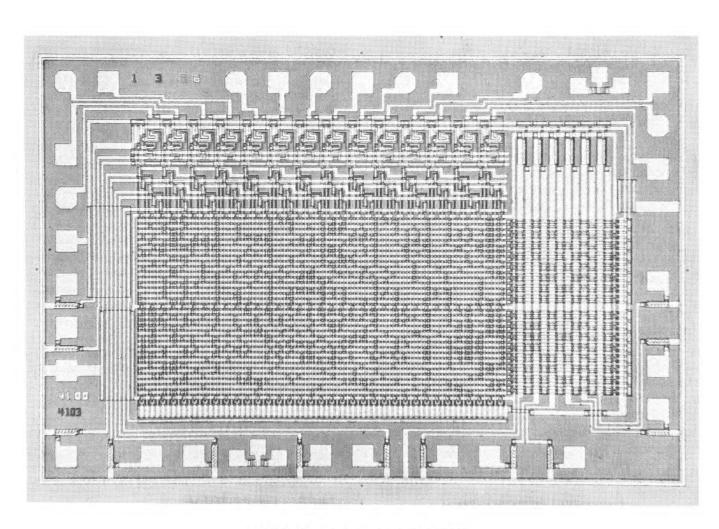

are used to cut the second-oxide removal mask ensuring fast turnaround time and completely eliminating code errors. A picture of the TMS4103 chip is shown in Figure 34 at the end of the chapter. The thin oxide, thick oxide, and metal are different shades of gray. The decoding, buffer and memory matrix sections are on the right, top and centre respectively, and the programmed areas can be seen in the memory matrix.

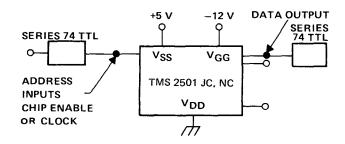

Power Supply Requirements: Two power supplies are required, VDD and VGG. The TMS 2501 JC, NC uses a  $V_{DD}$  of -5 V and a  $V_{GG}$  of -17 V. In most systems the designer will want to translate all power supplies up by 5 V and the following voltage VSS +5V, VDD = 0 V, VGG = -12 V. This will permit a TTL device interface. The typical power dissipation of this device at 50°C is 280 mW. VDD and  $V_{GG}$ , are nominally -14 V and -28 V for the 4103 device. No current is drawn from the -28 V V<sub>GG</sub> supply, since it is internally connected only to MOS gates. About 25 mA is drawn typically by the memory array from the -14 V V<sub>DD</sub> supply at 20°C ambient temperature, resulting in a 350-mW power dissipation. Additional power is dissipated in the output buffer devices, depending on the external output conditions. In most cases the designer will translate all power supplies by 14 V, and use  $V_{SS} = +14 \text{ V}$ ,  $V_{DD} = 0 \text{ V}$ ,  $V_{GG} = -14 \text{ V}$  as power supplies. This will also simplify TTL interface.

Address and Select Inputs: The TMS 2501 JC/NC type uses an exhaustive decoder (6 inputs in 64 x 8 x 5 organisation). It uses a 3 input address for the row (or column) select.

All of these inputs are connected to MOS gates. Each input is protected by a field-plate zener diode against gate damage due to static charge accumulation. Because only gates are being driven, the inputs appear capacitive and require no current other than the small leakage current associated with the protective zener.

The nominal logic voltage on the inputs are the following:

Logic High VSS Logic Low VDD

This leads to the following input definition:

| X        |

|----------|

| 3        |

|          |

| 5 to -12 |

|          |

| ιX       |

| λX       |

|          |

Output Characteristics: The TMS 2501 JC/NC features a triple-state push-pull output buffer connected between  $V_{SS}$  and  $V_{DD}$ . This will permit direct TTL capability. The fan-out of the TMS 2501 buffer is 2 TTL gates.

The' 4103 type character generators have a single transistor with an open drain at the output which can be returned to a negative voltage through external circuitry. A schematic showing a portion of the relevant internal MOS circuitry for this type appears in Figure 17. When a dot is to occur, the output device is turned on, pulling the drain toward ground. Otherwise, the device remains off.

As in a discrete MOSFET, the drain current of the output buffer is affected by its drain-to-source voltage  $V_{DS}$  and gate-to-source voltage  $V_{GS}$ . The value of  $V_{DS}$  is dependent on the external circuitry being driven, whereas  $V_{GS}$  is determined internally.

Speed Performance: The output current of an MOS character generator does not change instantaneously after a new input is applied. A delay occurs which is dependent on the following factors: the character program within the memory; whether a character-address, row-address or column-select input is changed; the characters involved if character address is altered; the direction of output change-on to off to on.

A primary source of delay is the charging of the gate lines in the memory array. The more gates connected or the more dots programmed in the character, the larger the capacitance and the longer the time required to charge the line. Position of the character storage area in the matrix

FIGURE 17. Portion of Output Circuitry

also affects delay due to the distributed-RC nature of the diffused drain lines.

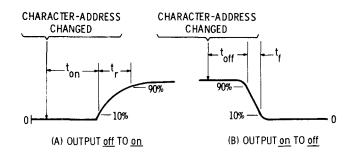

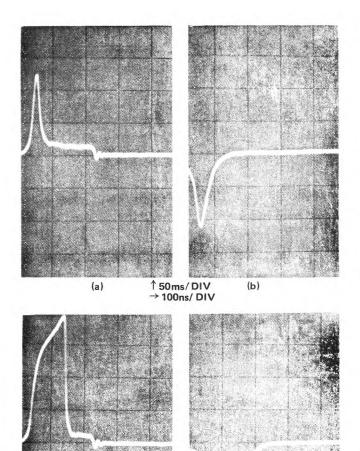

Response to a character-address change involves the longest delays. Beginning with an output initially off, if a column or row is selected and an input code is applied that will result in the output turning on, the resulting output current has the appearance in Figure 18(a). If the output is initially on and being turned off, Figure 18(b) is applicable.

FIGURE 18. Voltage Response of an MOS ROM

Output When Switched by a

Character-Address Change

For a given character,  $t_{\rm OI}$  is always greater than  $t_{\rm Off}$  because the output resistance of the decoder is greater when charging a gate line than when discharging it. Because these delay times are dependent on the particular character format desired by a customer, no definite values can be assigned to  $t_{\rm OI}$  and  $t_{\rm Off}$  for all memories.

Within a given memory, both  $t_{on}$  and  $t_{off}$  can vary, depending on the character chosen. Variations from 200 ns to 350 ns for  $t_{on}$  and from 60 ns to 160 ns for  $t_{off}$  are possible.

Turn-on and turn-off delays also exist when a column is enabled or disabled with a character-address input already applied. Both of these delays are typically less than 100 ns for the 4103 device.

The current rise time at an output is always greater than the fall time. Rise times can be as long as 200 ns while fall times are generally less than 100 ns.

The discussion of the speed is not only theoretical. There are many cases when the system design makes a maximum access time mandatory. When a plain TV monitor (625 lines) is used, the image is regenerated 25 times per second. If the desirable 80 characters per line of text is to be used a character must be obtained every 625 ns.

At 400 ns over this temperature range the TMS 2501 has speed to spare. The access times of the two character generators are as follows:

TMC 4102

|                     | 1M3 2301 | 1M3 4103 |

|---------------------|----------|----------|

| Character           | 400 ns   | 700 ns   |

| Row (column) select | 300 ns   | 300 ns   |

TMC 2501

Input and Output Interfacing: The TMS 2501 JC/NC interfaces directly to TTL, DTL as seen in Figure 19. All inputs, outputs, chip select and column select lines are directly TTL compatible without external components.

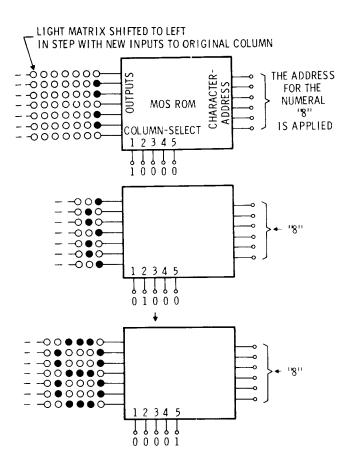

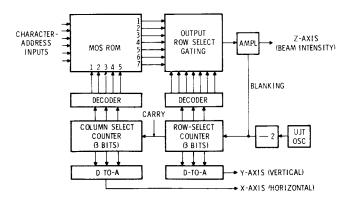

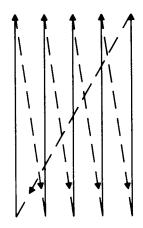

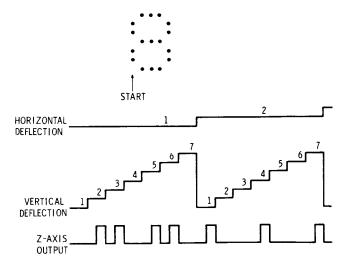

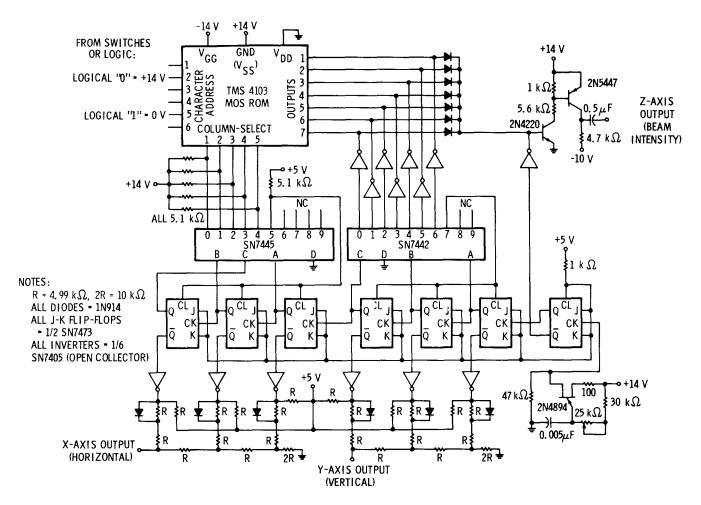

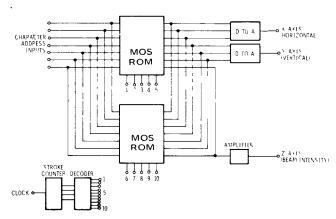

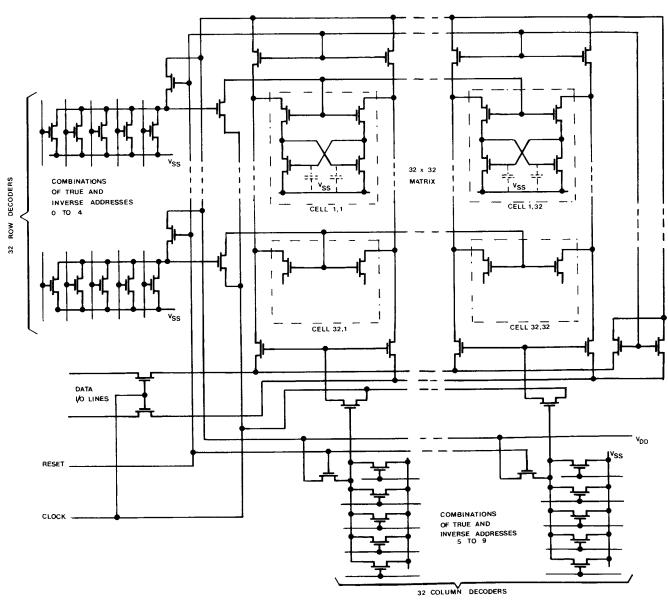

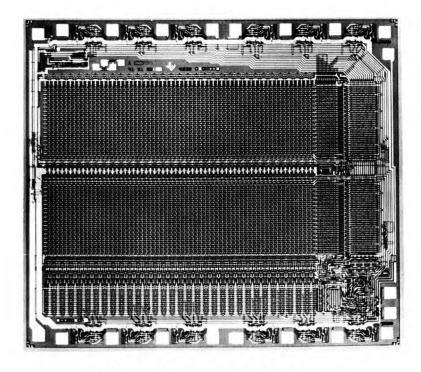

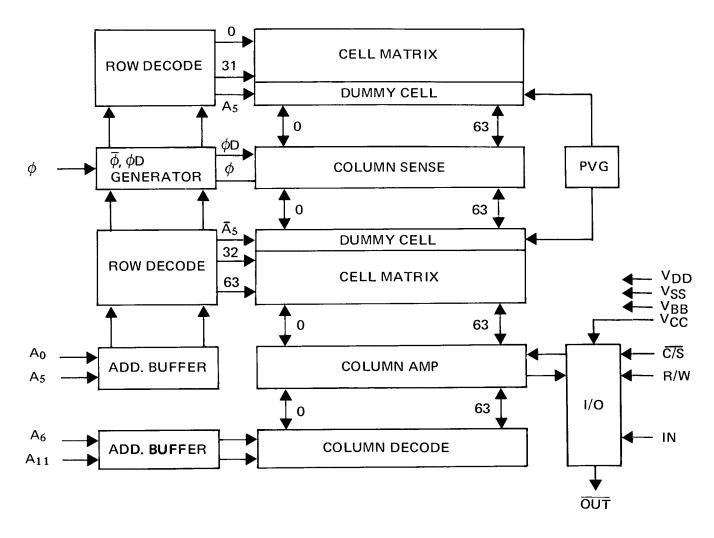

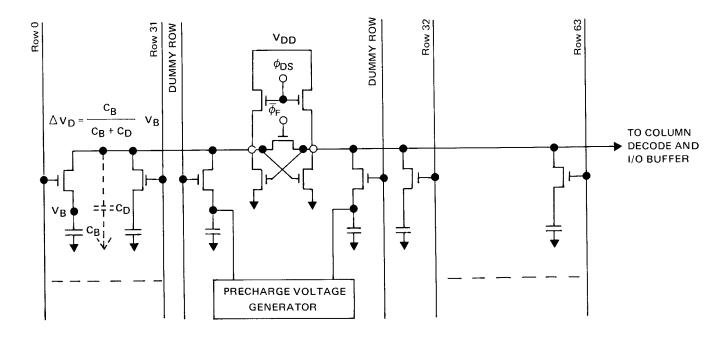

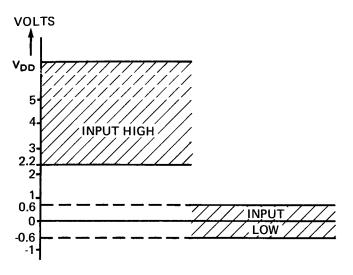

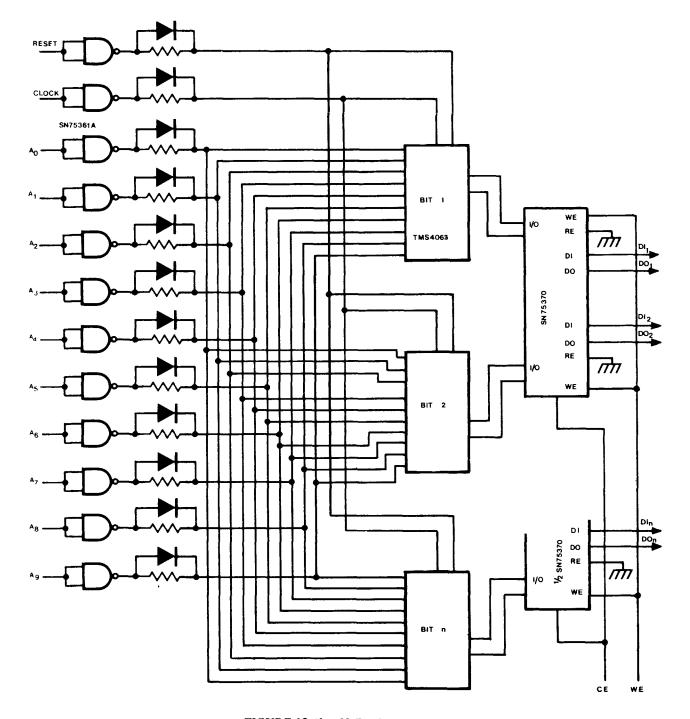

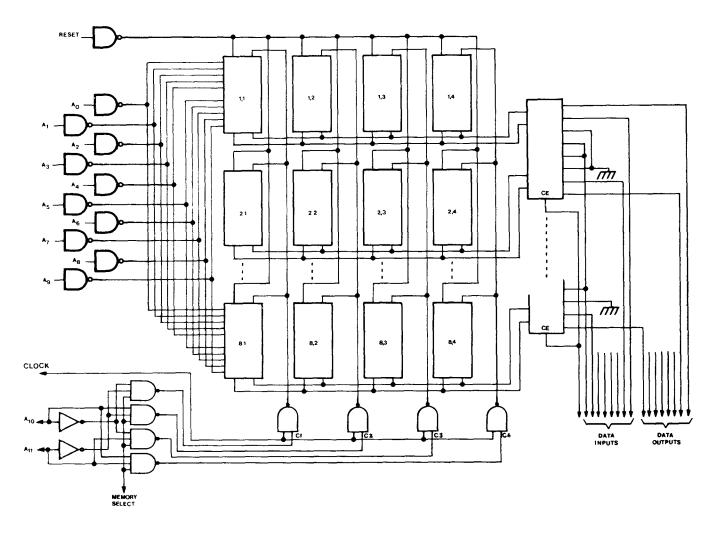

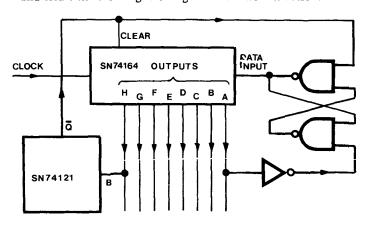

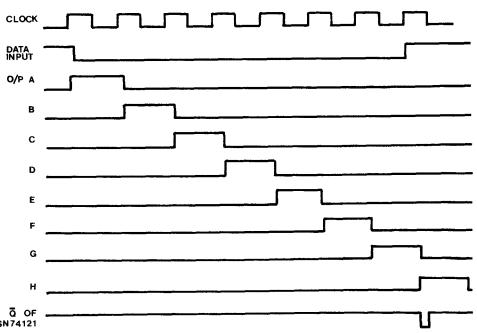

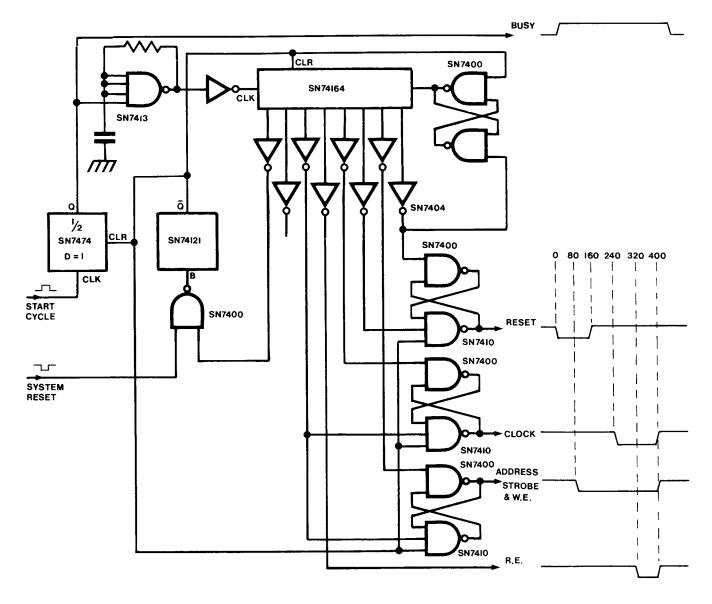

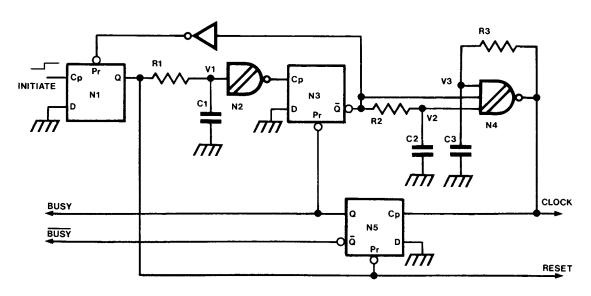

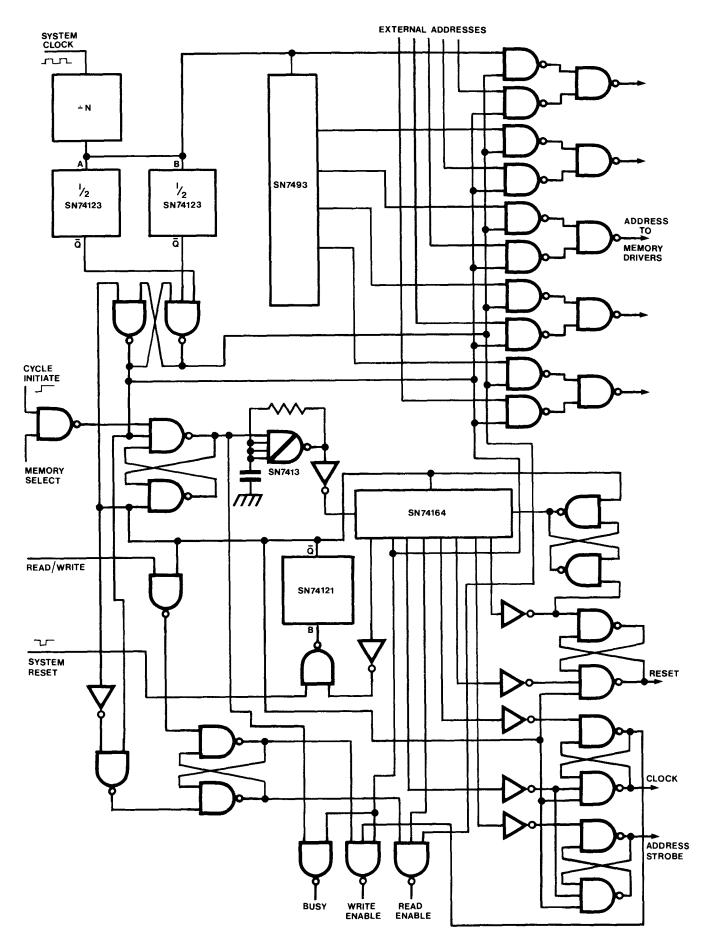

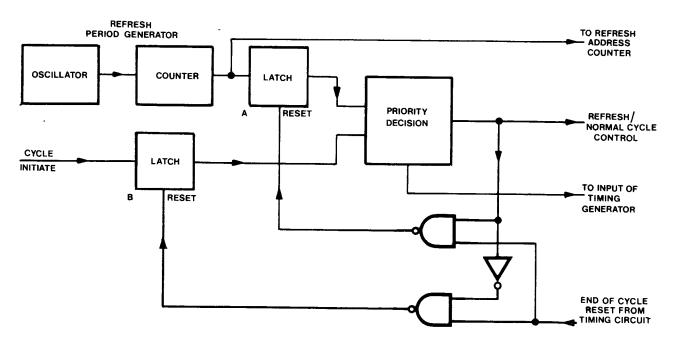

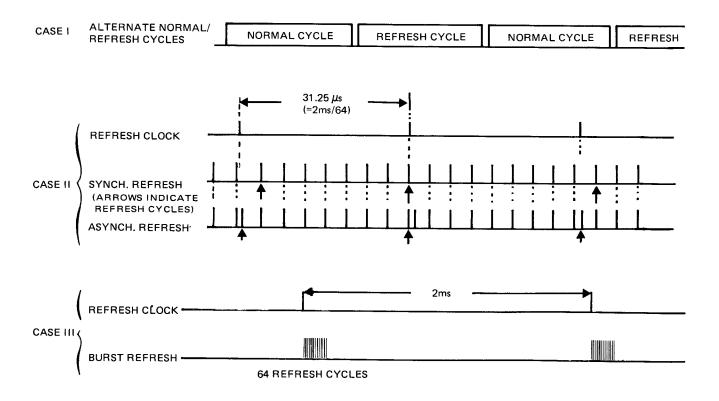

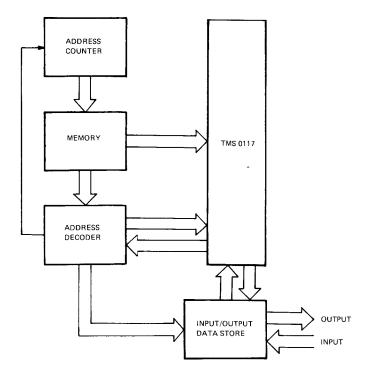

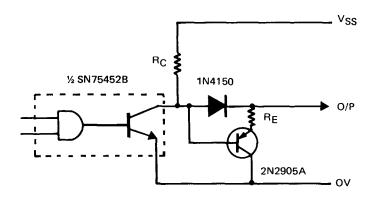

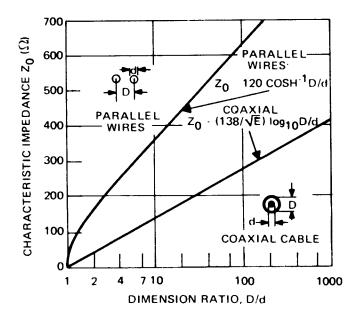

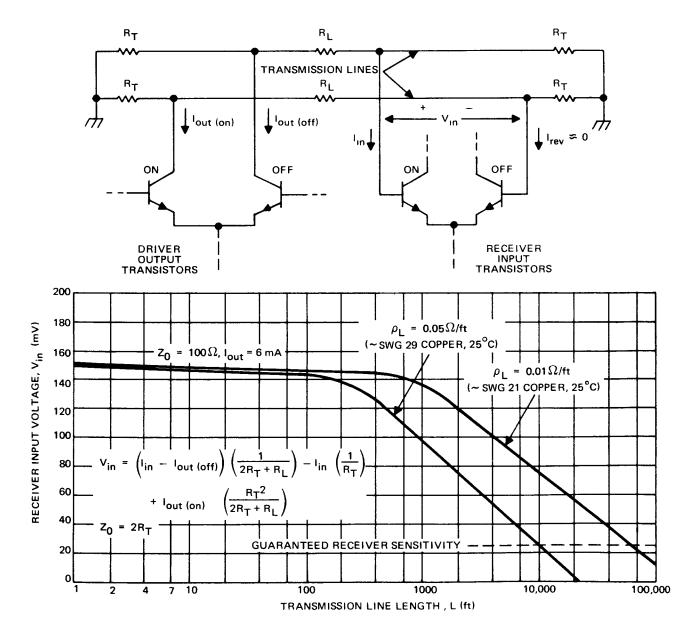

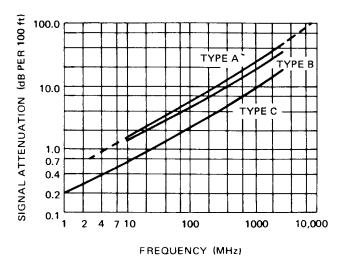

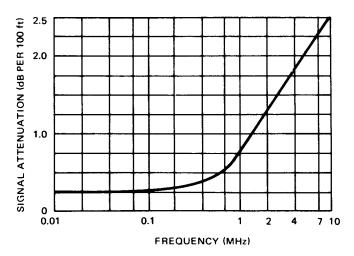

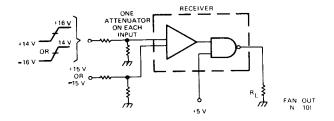

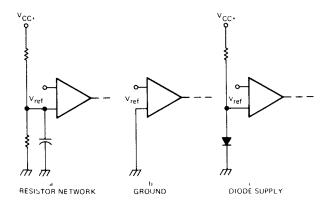

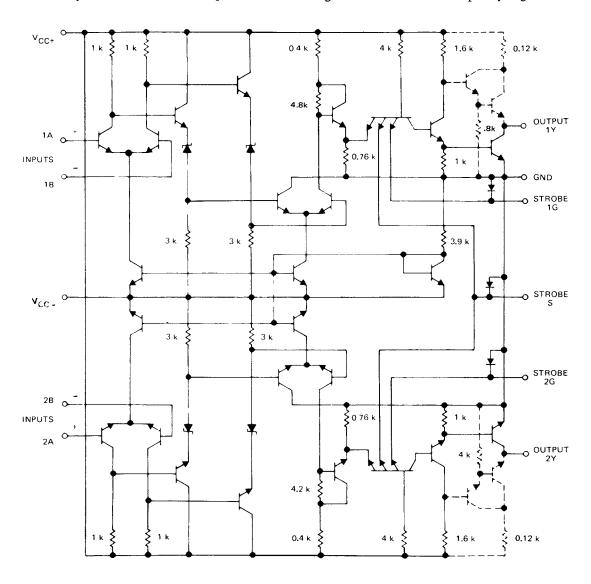

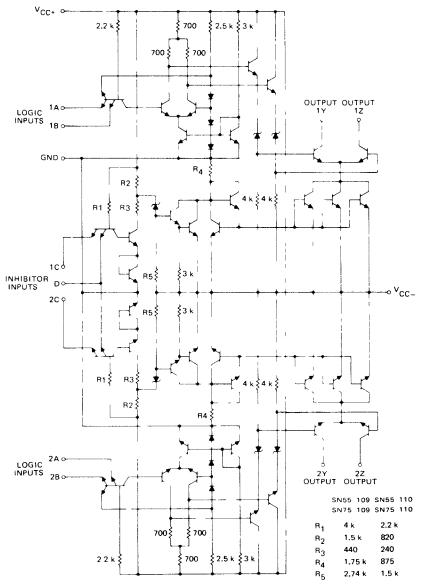

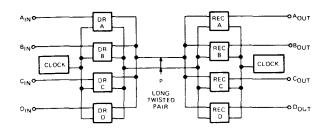

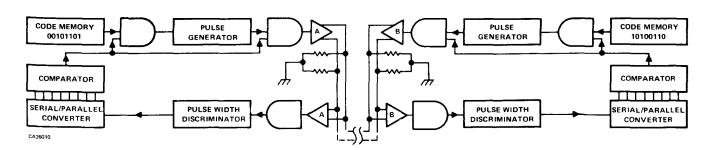

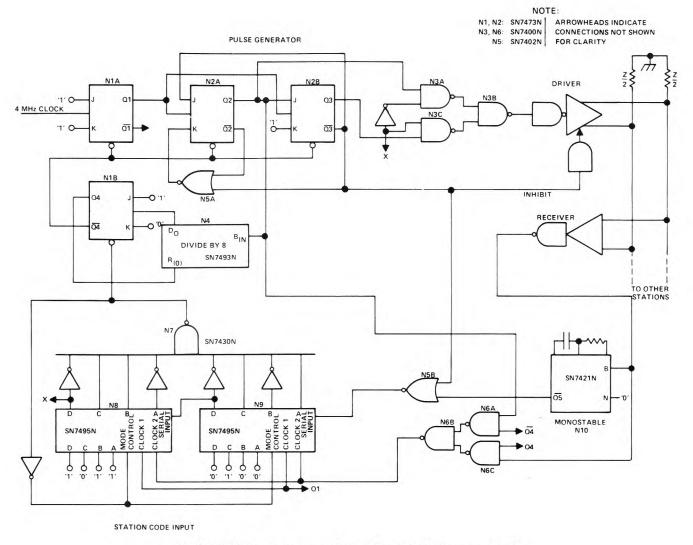

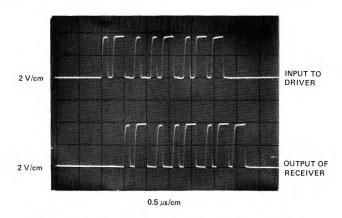

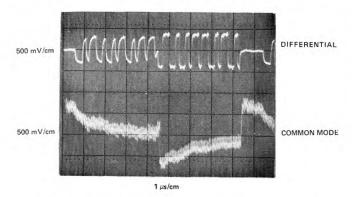

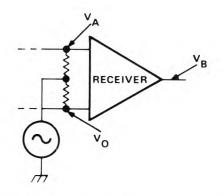

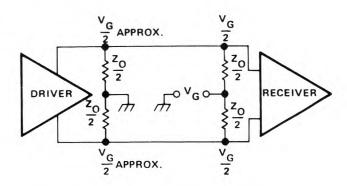

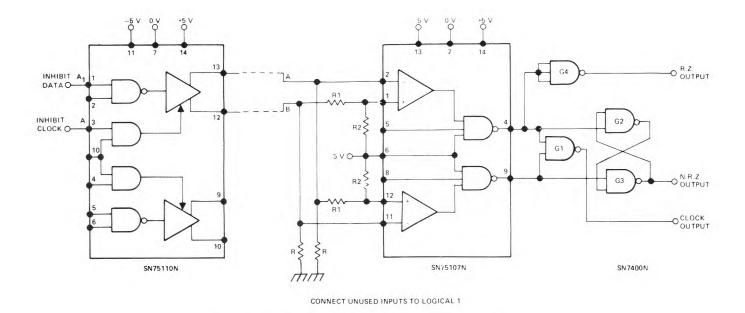

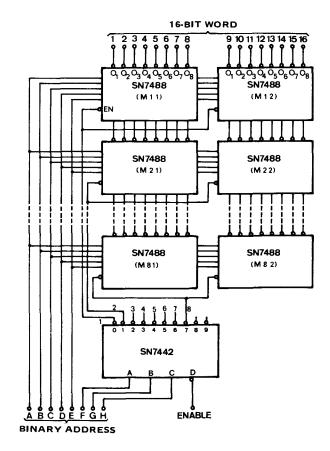

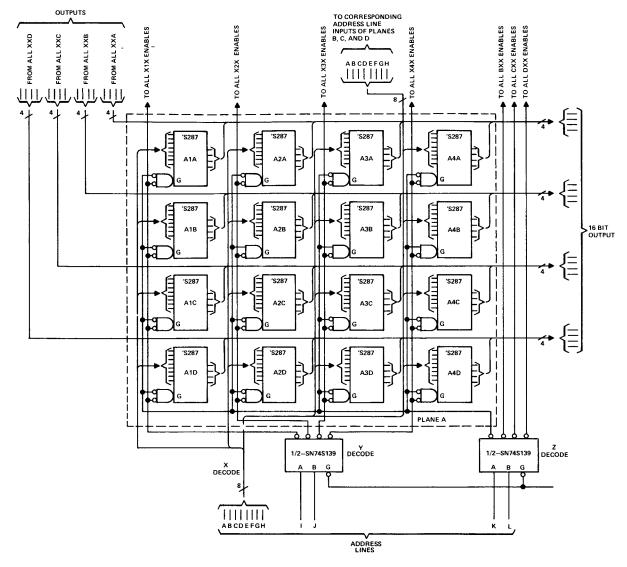

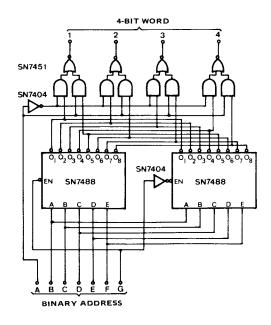

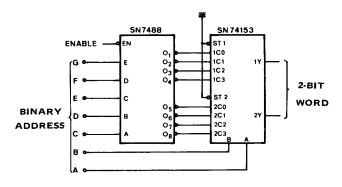

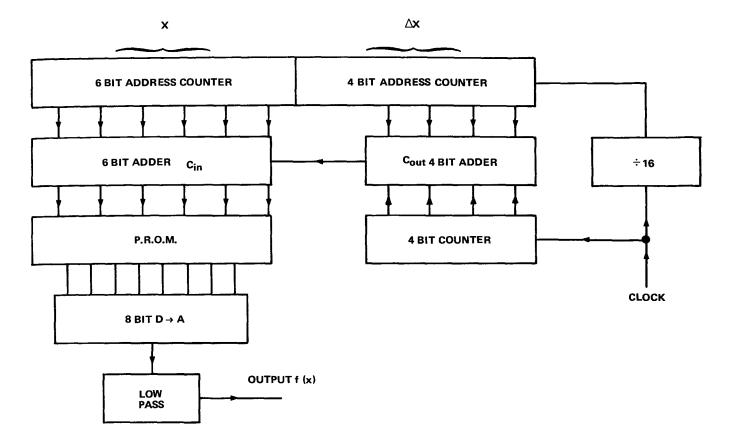

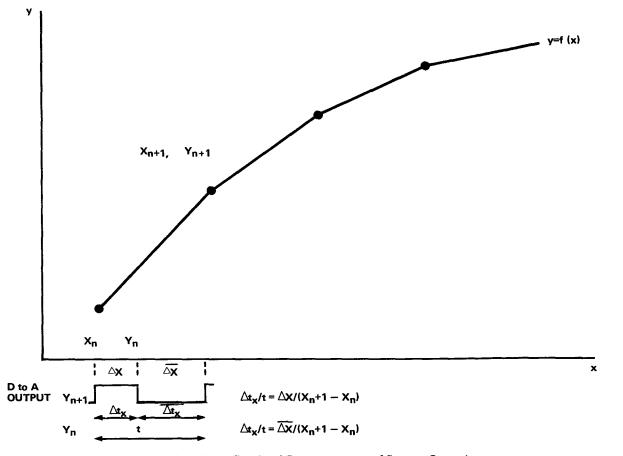

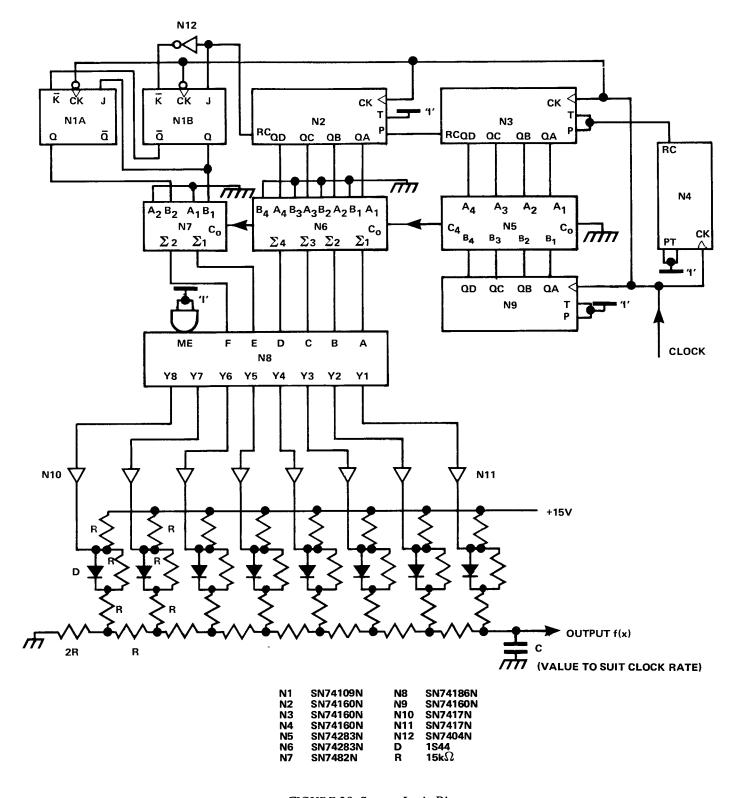

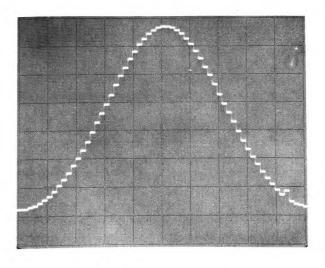

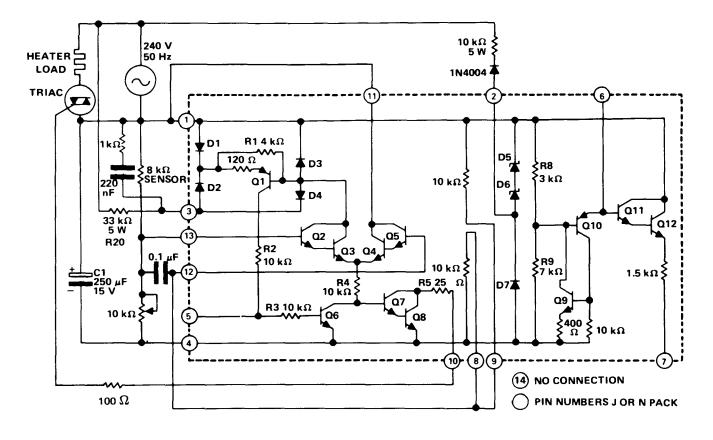

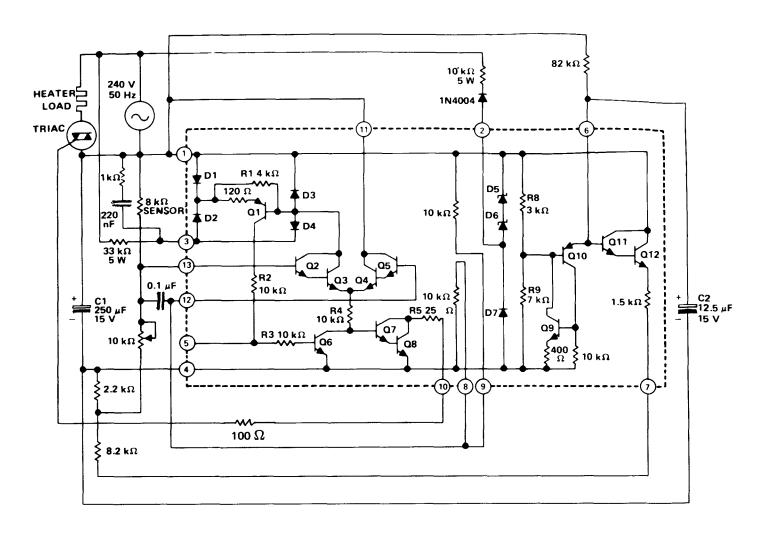

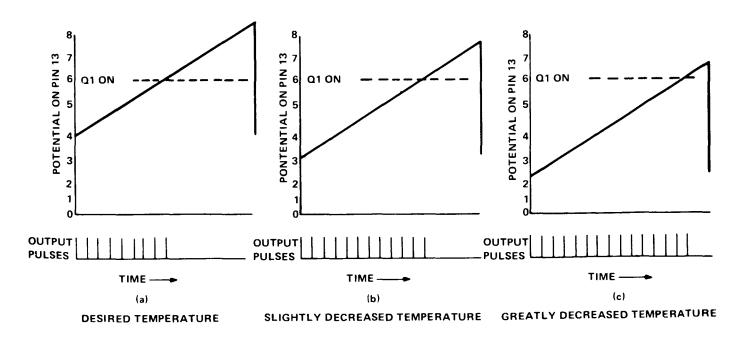

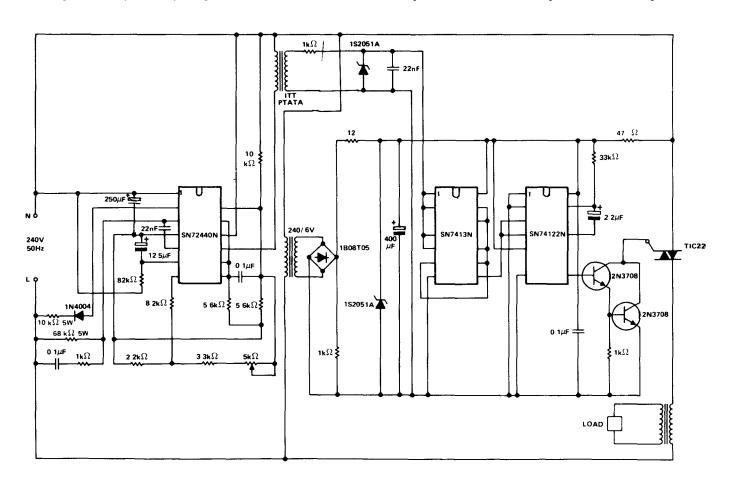

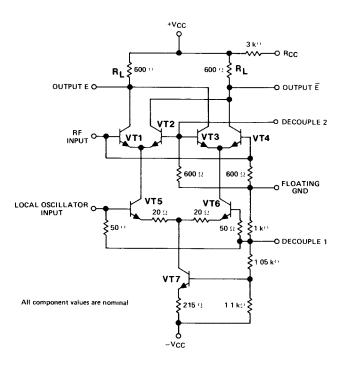

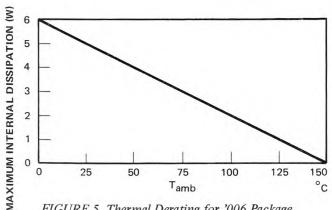

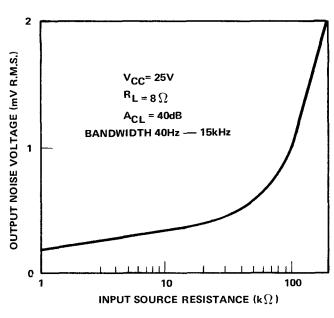

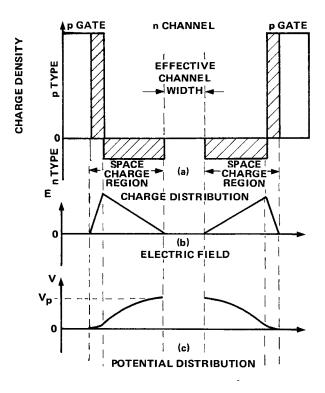

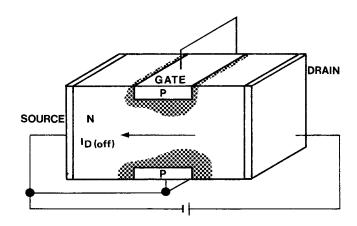

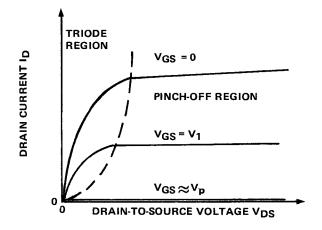

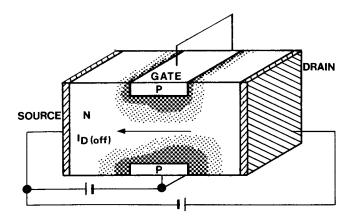

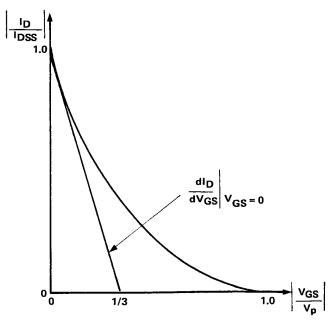

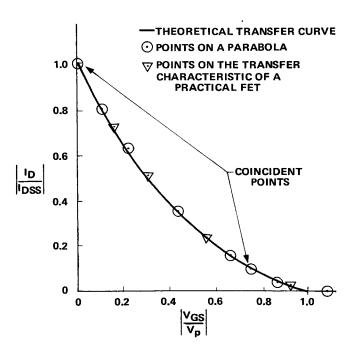

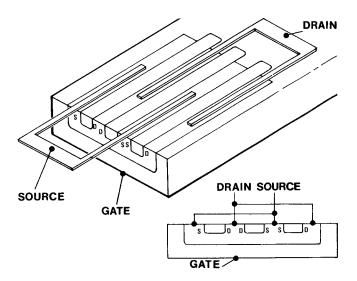

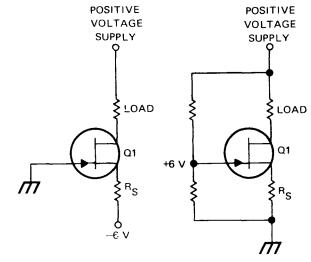

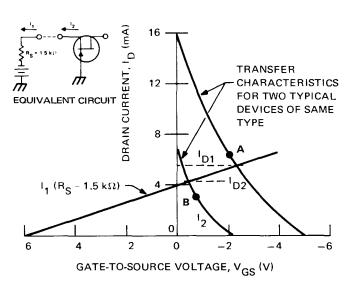

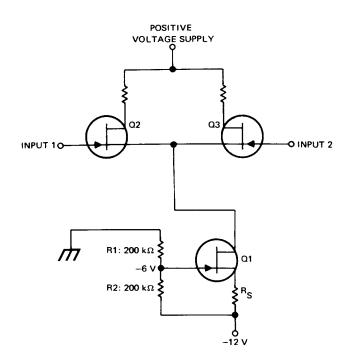

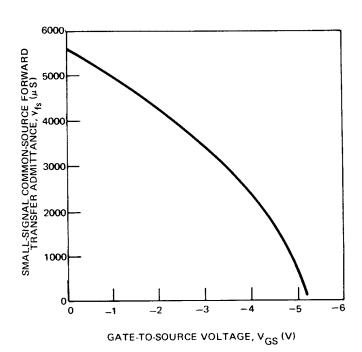

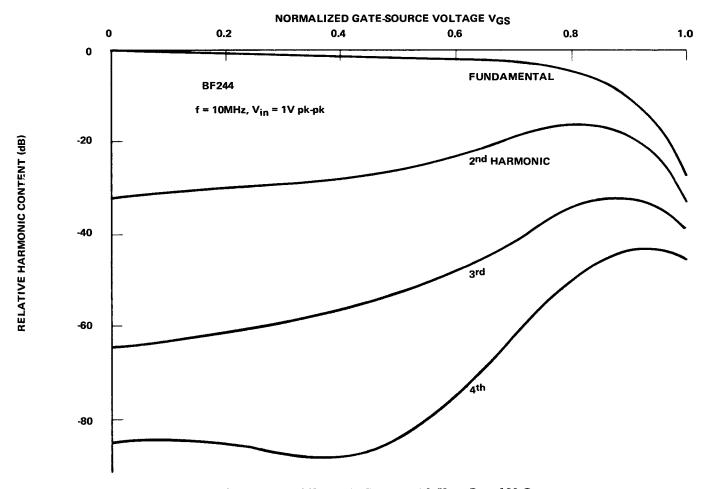

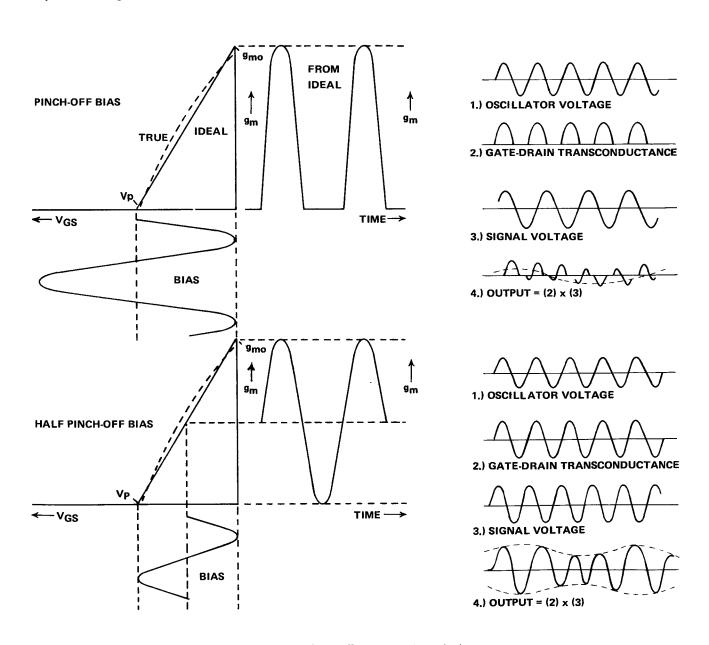

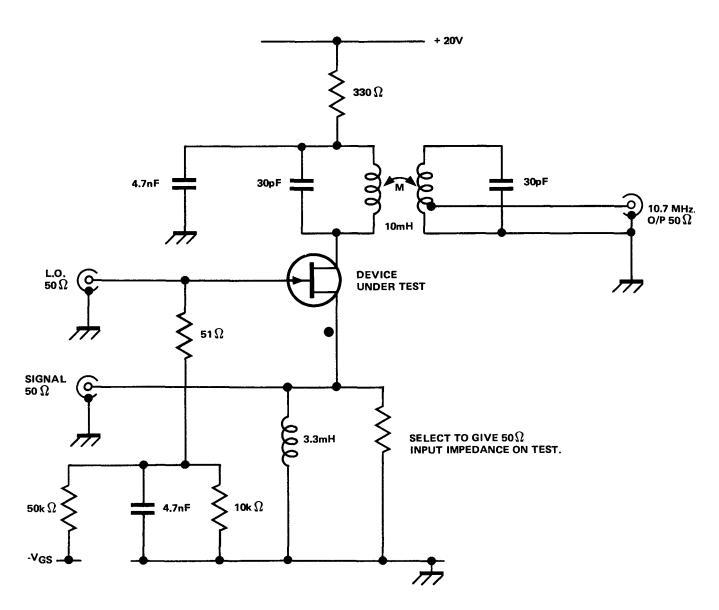

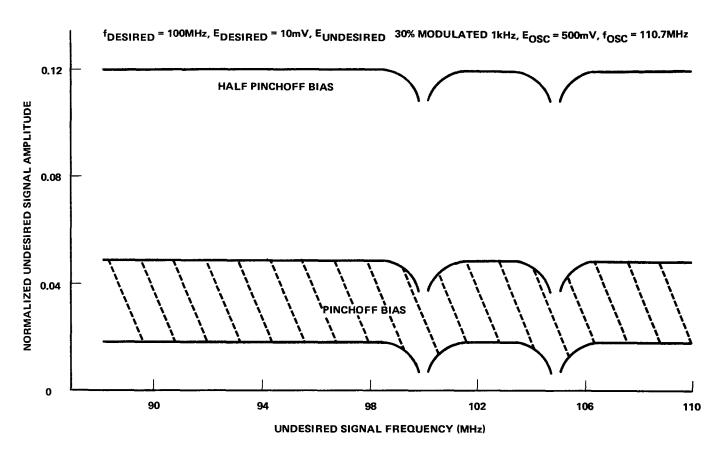

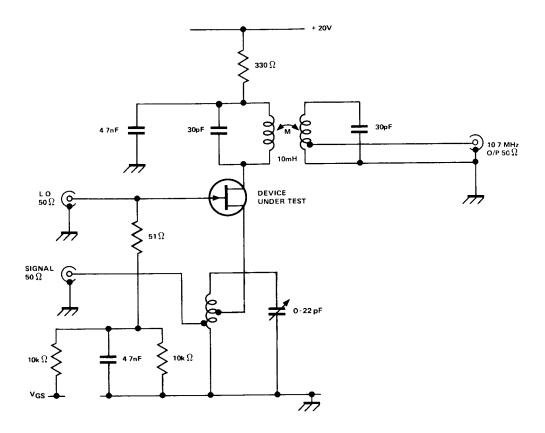

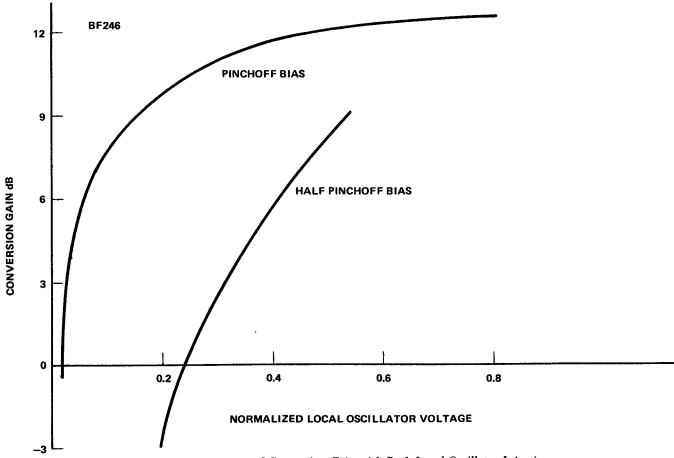

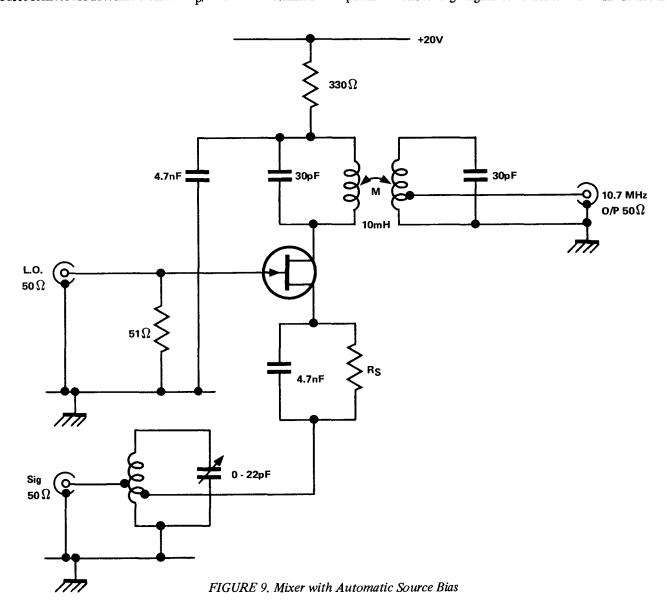

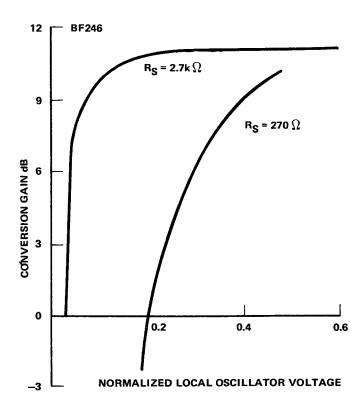

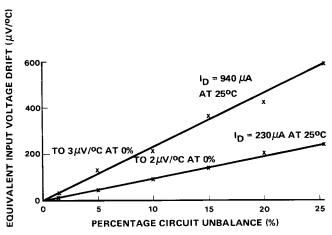

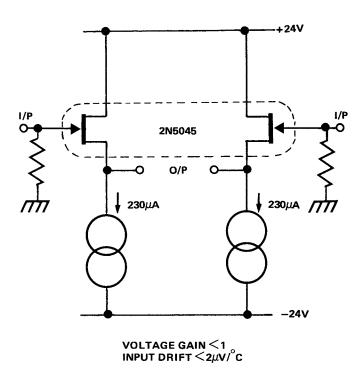

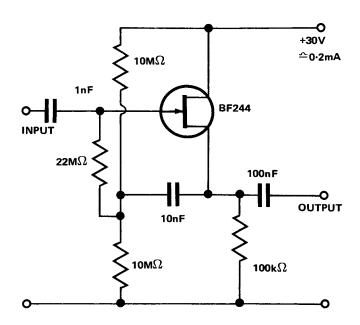

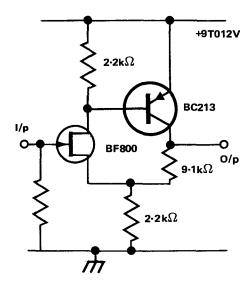

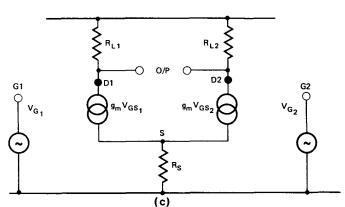

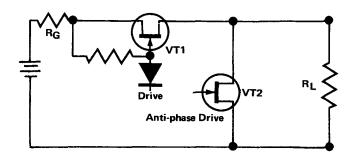

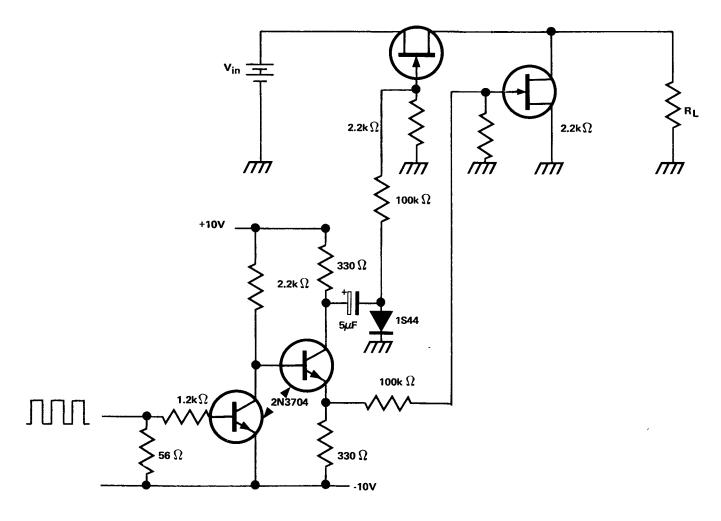

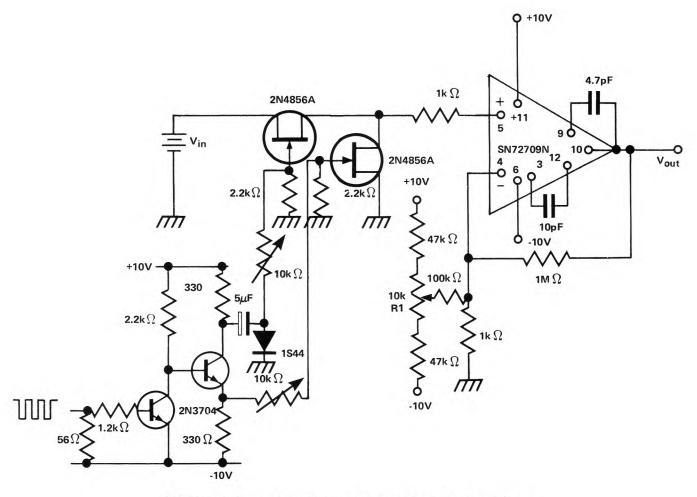

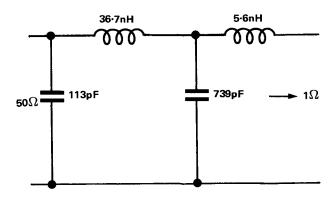

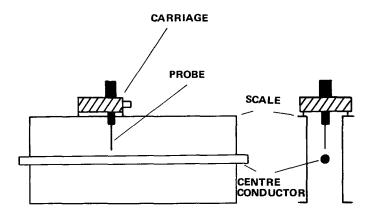

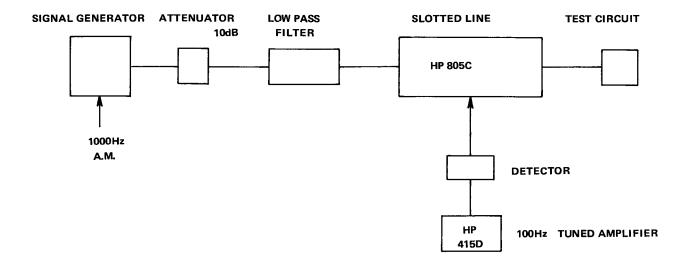

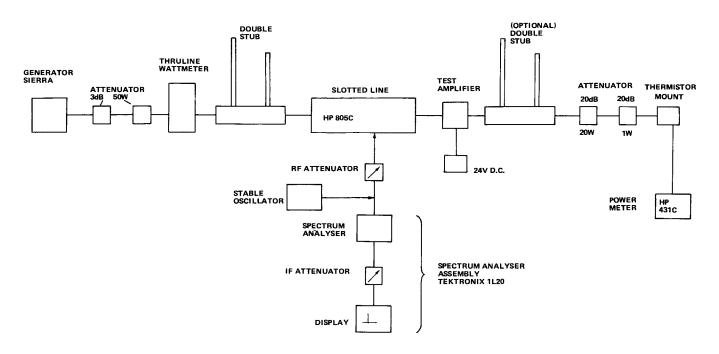

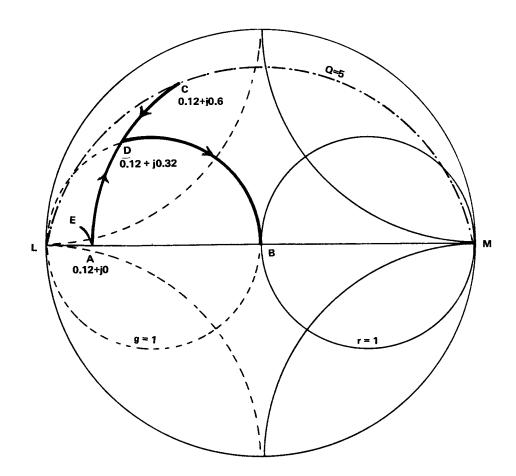

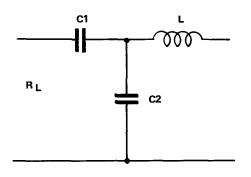

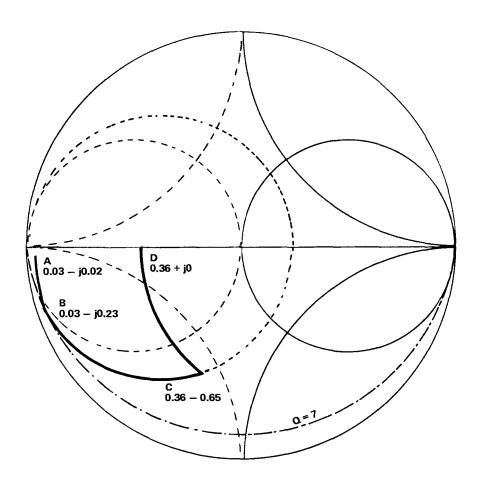

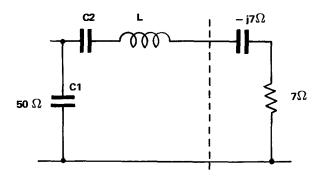

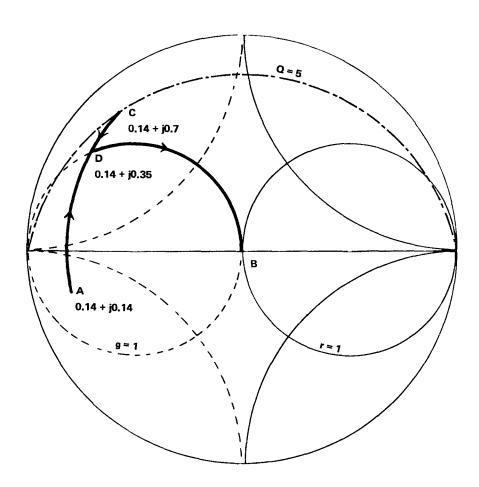

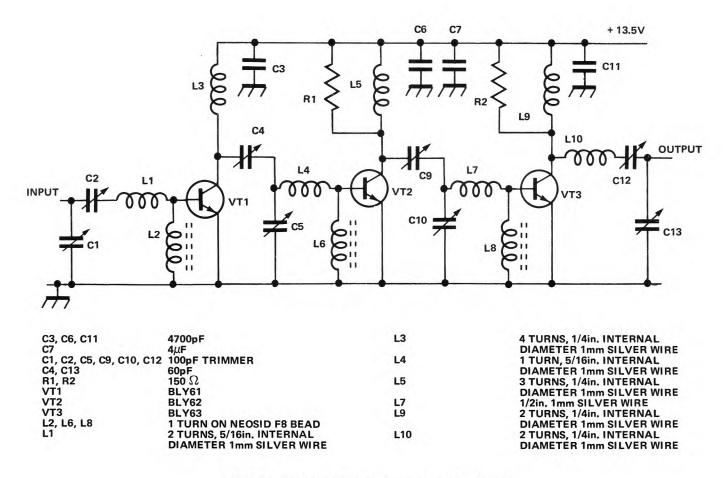

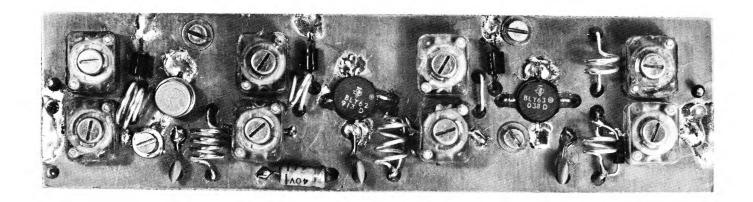

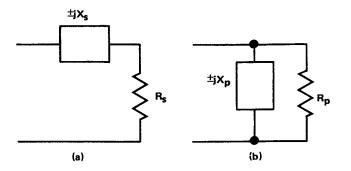

FIGURE 19. Interfacing TMS 2501 JC/NC With Series 74 TTL