# Semiconductor Circuit Design

Edited by: Bryan Norris, Manager, Applications Laboratory, Texas Instruments Limited

### Semiconductor Circuit Design

Bryan Norris, Texas Instruments Ltd.

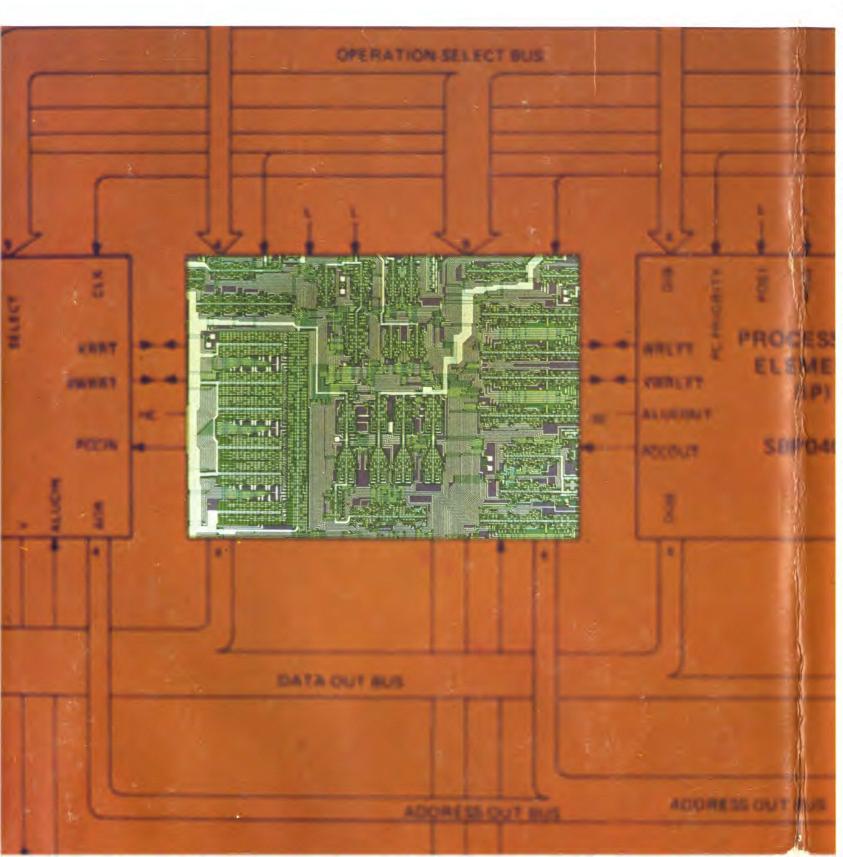

This is the fourth in a series of text books published by Texas Instruments Ltd to enable the reader to keep up to date with the latest developments in circuit design using semiconductors. The majority of material in this volume has been written by members of the Texas Instruments Applications Laboratory in Bedford. The series of text books is edited by Bryan Norris who has been manager of the Bedford Application Laboratory since 1967 and has a wide experience in all areas of circuit design. This latest volume is divided into two sections which deal broadly with Power Control and Digital Processing Techniques. In each section are chapters covering operational data and a wide range of applications for devices such as Power Transistors, Rectifiers, Triacs, Programmable Unijunction Transistors, Numeric Displays and complex Bipolar and MOS I.C.s. There are also chapters on I<sup>2</sup>L technology and I.C. Microprocessors.

In common with the other books in the series this volume is intended to be of use both to the moderately advanced student and the designers in industry who can apply the circuits as they stand or adapt them to a specific need.

The authors contributing to this volume include:

DAVID A. BONHAM

JUREK BUDEK

HOWARD COOK

STEVEN CRAFT

PETER VAN CUYLENBURG

PAUL GRÜNENFELDER

MICK MAYTUM

BOB PARSONS

JOHN READ

KEN SALMON

PETER WILSON

ISBN 0 904047 03 2

# Semiconductor Circuit Design

Vol. IV

Edited by: Bryan Norris Manager, Applications Laboratory, Texas Instruments Limited

Copyright 1975 by Texas Instruments Limited

All Rights Reserved

This publication, or parts thereof, may not be reproduced in any form without the permission of the publishers, Texas Instruments Ltd. Texas Instruments reserve the rights to make changes at any time in order to improve design and supply the best product possible. Information contained in this publication is believed to be accurate and reliable. However, responsibility is assumed neither for its use nor for any infringement of patent or rights of others which may result from its use. No licence is granted by implication or otherwise under any patent or patent right of Texas Instruments or others.

ISBN 0 904047 03 2

1st Edition May 1975 2nd Impression September 1975 3rd Impression January 1977

Printed in Great Britain by Morrison and Gibb Ltd, London and Edinburgh. Artwork produced by Newnorth Artwork Ltd, Bedford.

#### **Preface**

The aims of this series of Semiconductor Circuit Design books are to provide up to date information on a broad range of semiconductors, and to give straightforward examples of how the devices may be used in practice. All the chapters have therefore been written by practising professional engineers with these aims in view.

The arrangement of sections differs from proceding volumes in that, instead of grouping the chapters by device types, I have sectioned the book into two broad application areas, namely Power Control and Digital Processing Techniques.

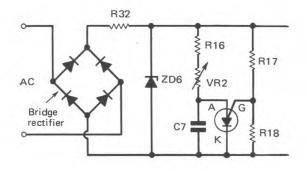

In the first section there are three chapters which examine Rectifiers, High Voltage Power Transistors and Programmable Unijunction Transistors respectively. The following two chapters describe circuits in which these devices are employed, and the section is completed by chapters on touch control and phychedelic lights control.

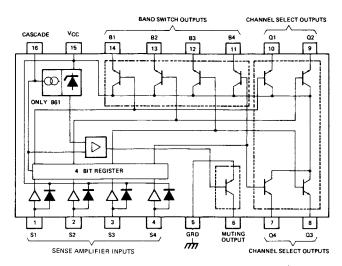

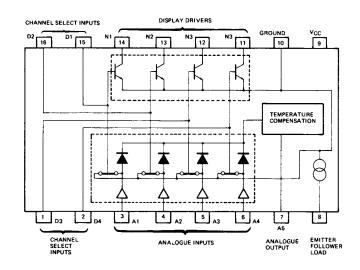

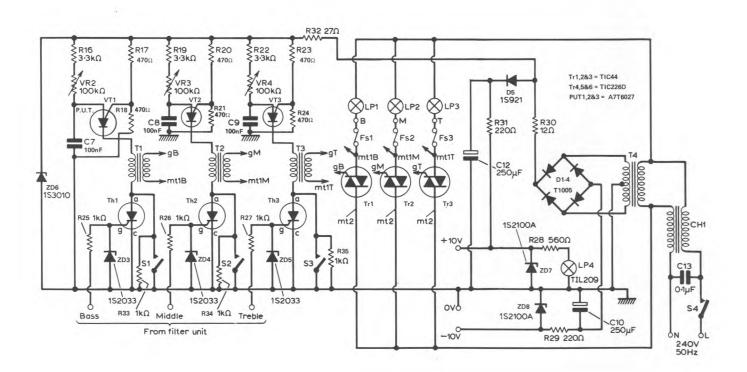

The Digital Processing section opens with one chapter defining and grouping microprocessors and microcomputers and explaining the use of two specific types, and a second describing how, by using Schottky T.T.L. I.C.s, a fast microcomputer may be produced. The succeeding chapters are concerned with peripheral devices and circuits, e.g. Programmable Read Only Memories, T.T.L. Random Access Memories, Universal Asychronous Receiver/Transmitter, Binary and Decimal Rate Multipliers, Priority Encoders and Numerical Displays. The final chapter describes the evolution, fabrication and applications of a new technology, Integrated Injection Logic (I<sup>2</sup>L).

I should again like to express my thanks to all the contributing authors, and also the editor of Practical Wireless, Lionel Howes, for permission to use material originally written for that magazine, on which Chapter VII is based.

**BRYAN NORRIS**

Applications Manager Texas Instruments Limited April 1975

# **Contents**

## **SECTION 1. POWER CONTROL**

|             |                                           | Page   |

|-------------|-------------------------------------------|--------|

| Chapter I   | USE OF RECTIFIERS                         | <br>1  |

|             | Single Phase Rectifier Circuits           | <br>1  |

|             | Three Phase Rectifier Circuits            | <br>13 |

|             | Three Phase Power System                  | <br>14 |

|             | References                                | <br>22 |

| Chapter II  | USE OF HIGH VOLTAGE SWITCHING TRANSISTORS | <br>23 |

|             | Construction                              | <br>23 |

|             | Effect on Parameters                      | <br>24 |

|             | A Circuit Operation                       | <br>25 |

|             | Transistor Ratings                        | <br>27 |

|             | Switching Requirements                    | <br>28 |

|             | Control of Base Current                   | <br>29 |

|             | Measurement Parameters                    | <br>29 |

|             | Measuring Systems                         | <br>29 |

|             | Measurement Procedure                     | <br>30 |

|             | Device Dissipation                        | <br>31 |

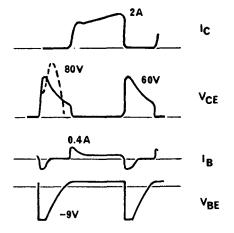

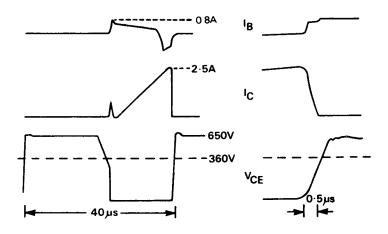

|             | Analysis of Waveforms                     | <br>32 |

|             | Transient Analysis                        | <br>33 |

|             | References                                | <br>34 |

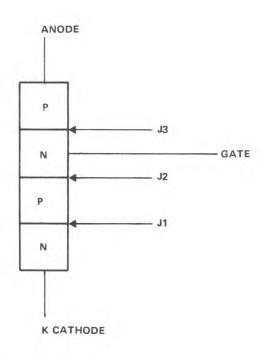

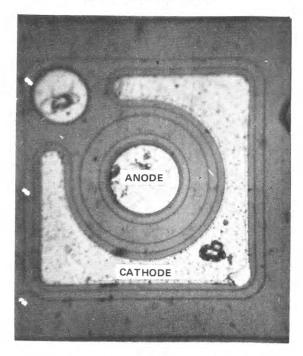

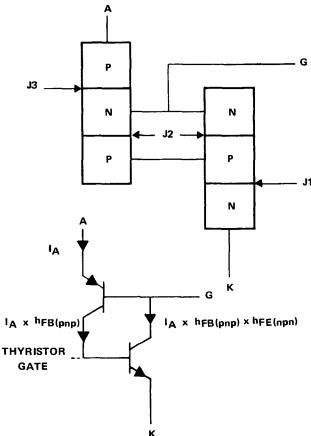

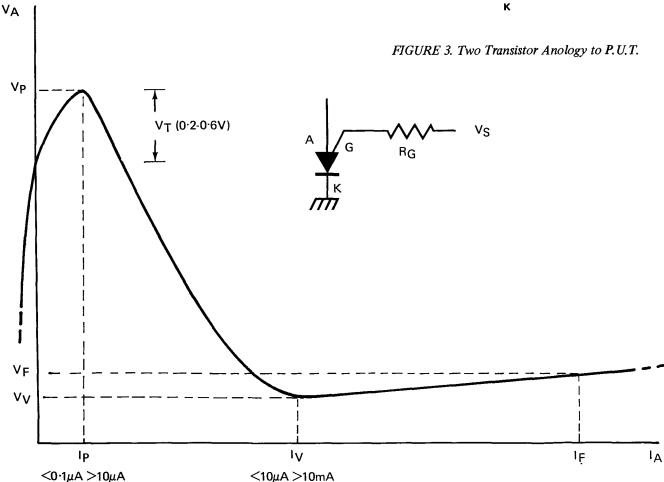

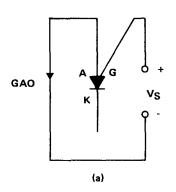

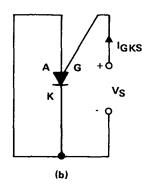

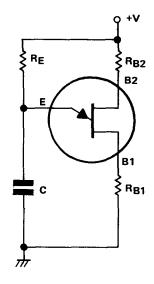

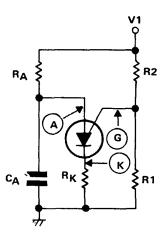

| Chapter III | PROGRAMMABLE UNIJUNCTION TRANSISTORS      | <br>35 |

| -           | Device Characteristics                    | <br>35 |

|             | Definition of Parameters                  | <br>39 |

|             | Applications                              | <br>39 |

|             | Reference                                 | <br>46 |

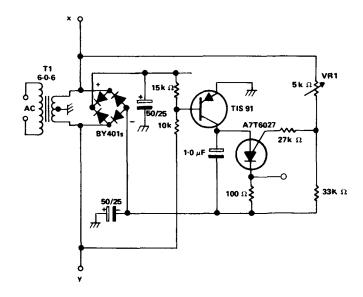

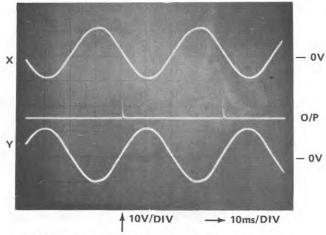

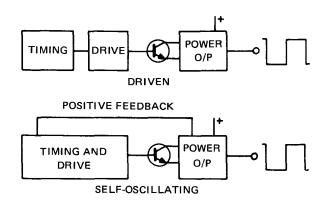

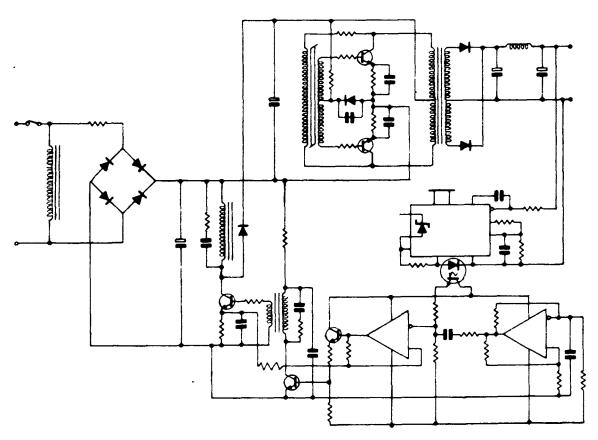

| Chapter IV  | INVERTER/CONVERTER SYSTEMS                | <br>47 |

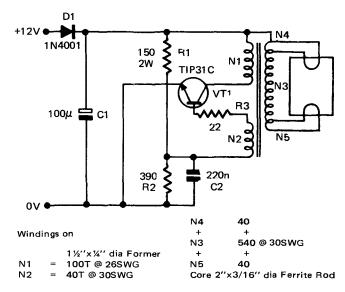

|             | Single Ended Self Oscillating Circuits    | <br>47 |

|             | Single Ended Driven Circuits              | <br>50 |

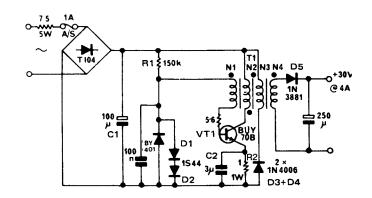

|             | Push-Pull Self Oscillation Circuits       | <br>55 |

|             | Push-Pull Driven Circuits                 | <br>57 |

|             | References                                | <br>64 |

|             | Acknowledgement                           | <br>64 |

|             |                                               | Page |

|-------------|-----------------------------------------------|------|

| Chapter V   | SWITCHING MODE POWER SUPPLIES                 | 65   |

| -           | Cascaded Approach                             | 65   |

|             | Design Example (Single Power Device Approach) | 68   |

|             | References                                    | 75   |

|             | Appendix                                      | 76   |

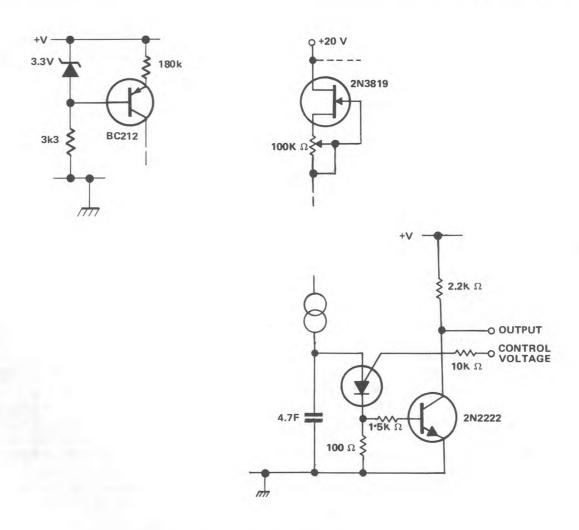

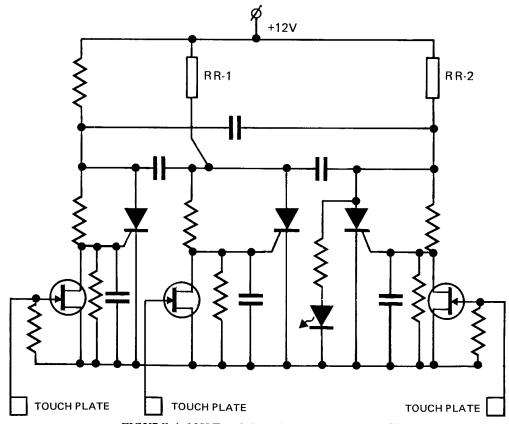

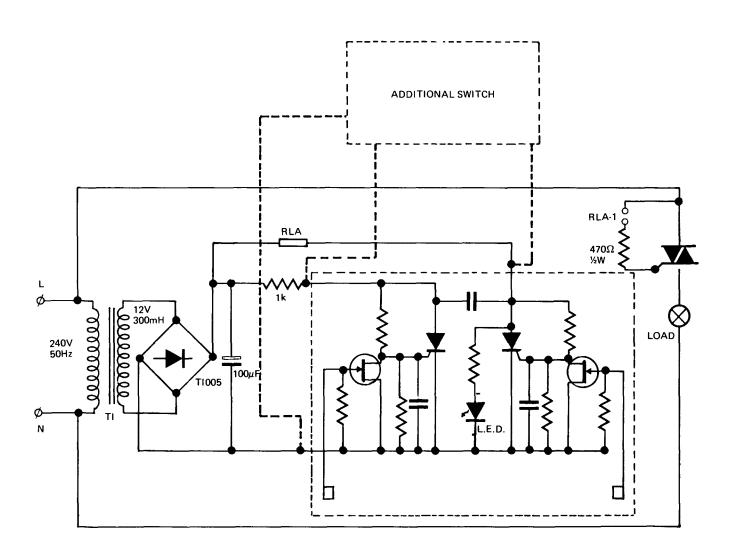

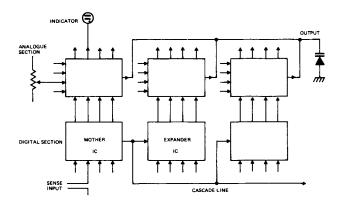

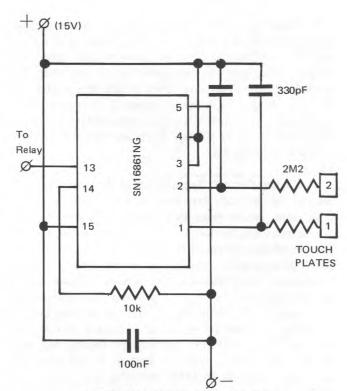

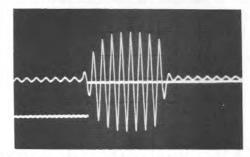

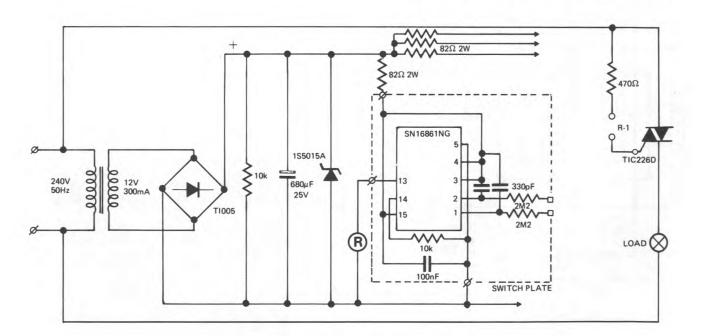

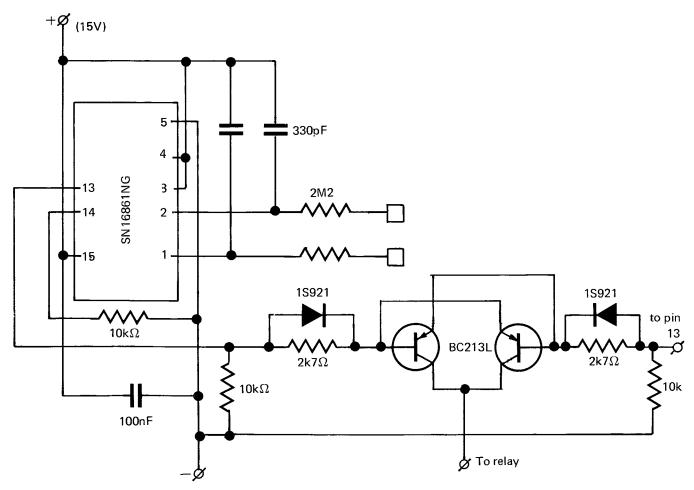

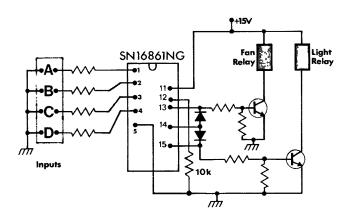

| Chapter VI  | TOUCH SWITCH POWER CONTROL                    | 79   |

| •           | Using Field Effect Transistors                | 79   |

|             | Using Integrated Circuits                     | 82   |

|             | References                                    | 90   |

|             | Acknowledgement                               | 90   |

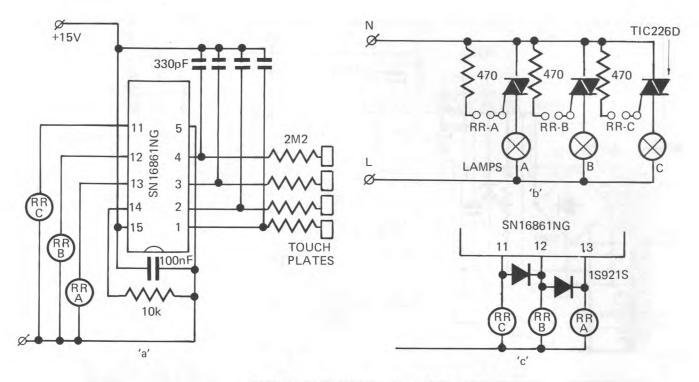

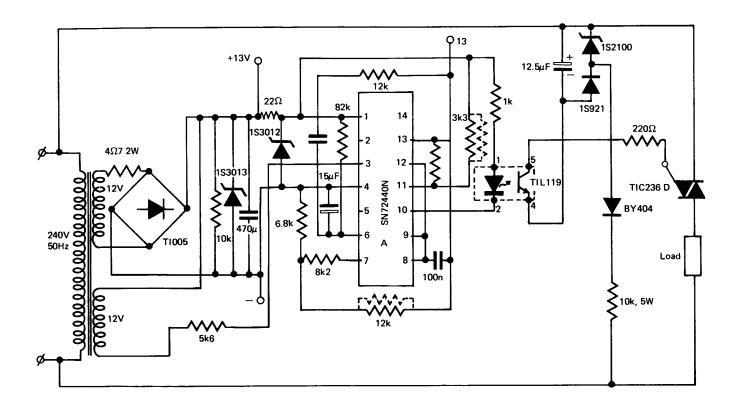

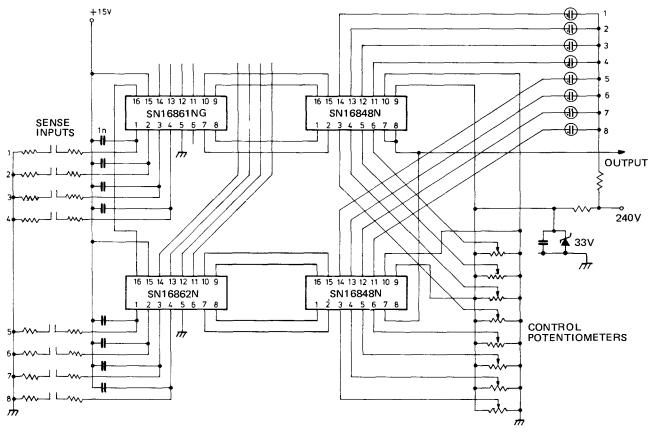

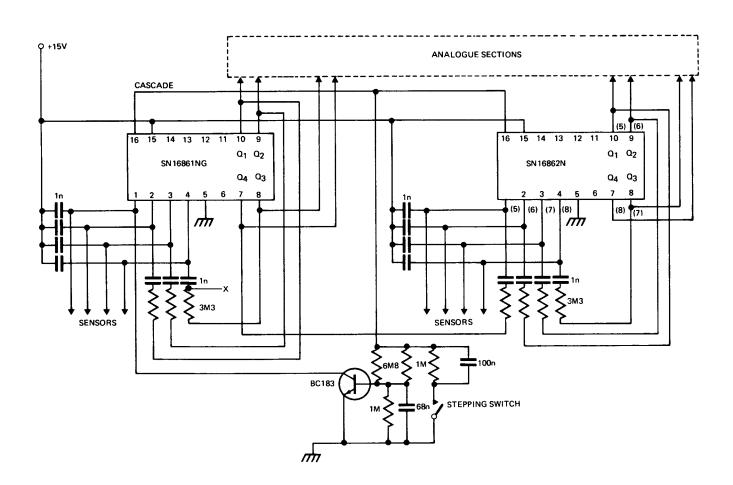

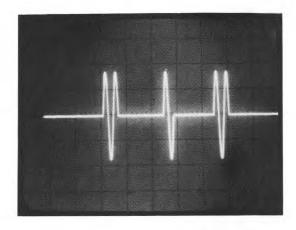

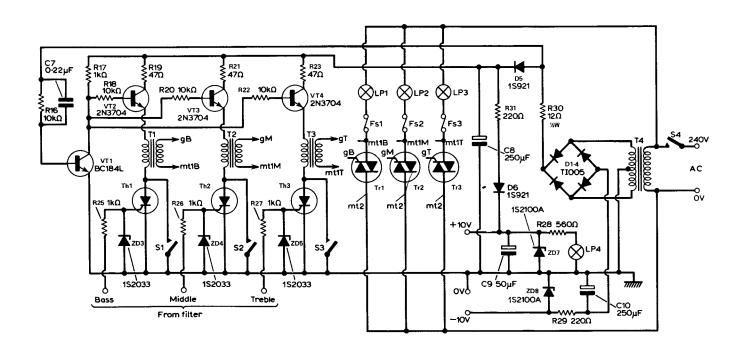

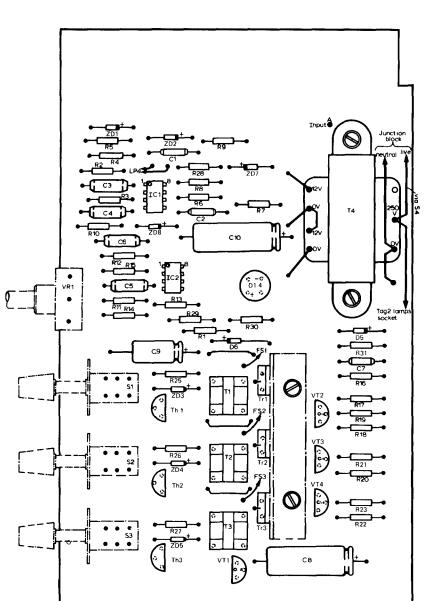

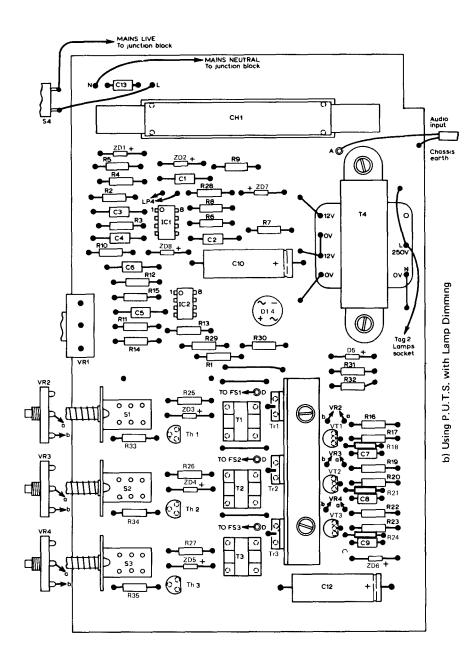

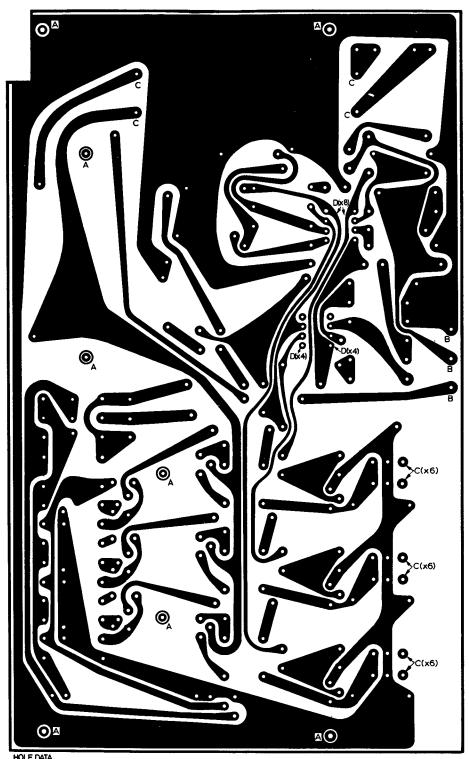

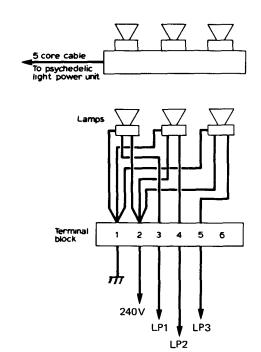

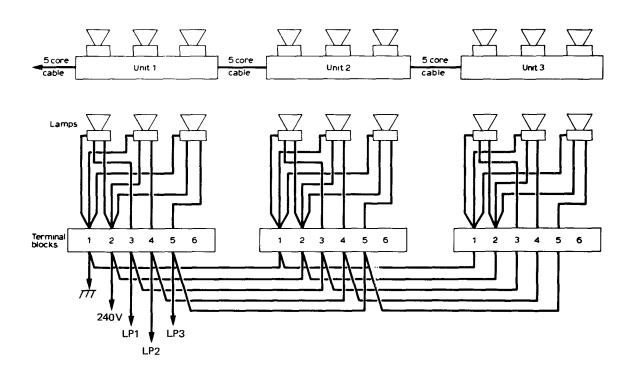

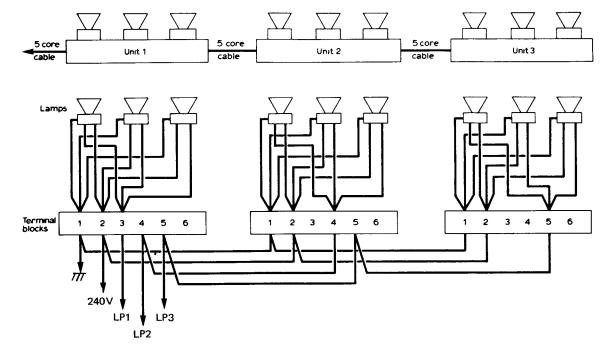

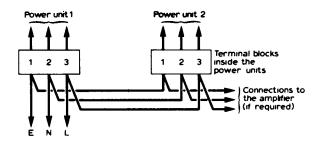

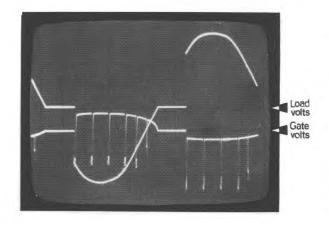

| Chapter VII | PSYCHEDELIC LIGHTS CONTROL                    | 91   |

|             | Circuit Description                           | 91   |

|             | Interconnection                               | 94   |

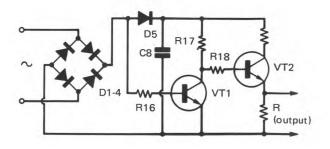

|             | Lamp Dimming                                  | 98   |

|             | References                                    | 100  |

# **SECTION 2. DIGITAL PROCESSING TECHNIQUES**

| Chapter VIII | MICROPROCES                          |             |         |       |        |       |       |       |         |       |     |

|--------------|--------------------------------------|-------------|---------|-------|--------|-------|-------|-------|---------|-------|-----|

|              | Micro-Computer                       |             |         |       |        |       |       |       |         |       |     |

|              | Micro-Processors                     |             |         |       |        |       |       |       |         |       |     |

|              | A 4-Bit Slice Mi                     |             | or Elem | nent  |        |       |       |       |         |       |     |

|              | One Chip Micro                       | computers   |         |       |        |       |       |       |         |       |     |

|              | References                           | • • • • •   |         |       | • •    |       |       |       |         |       |     |

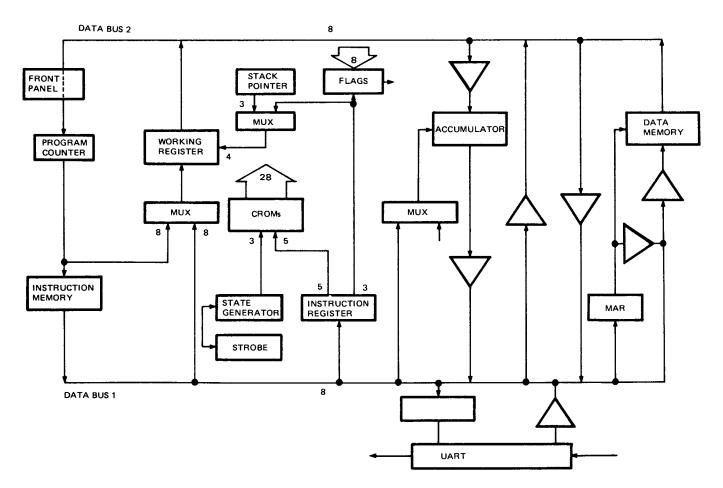

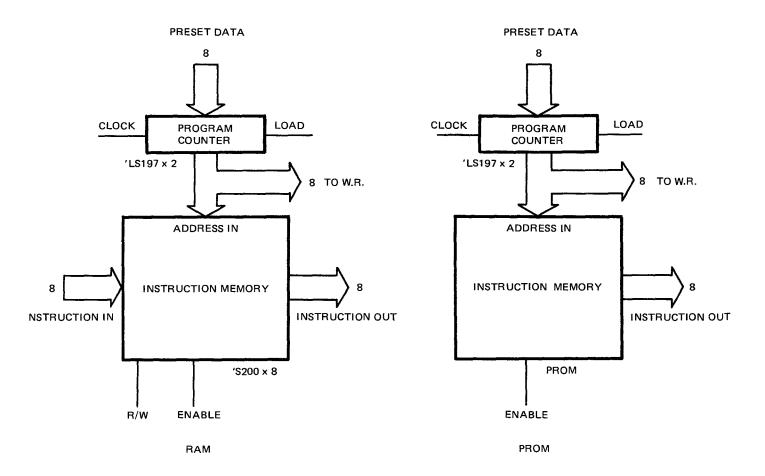

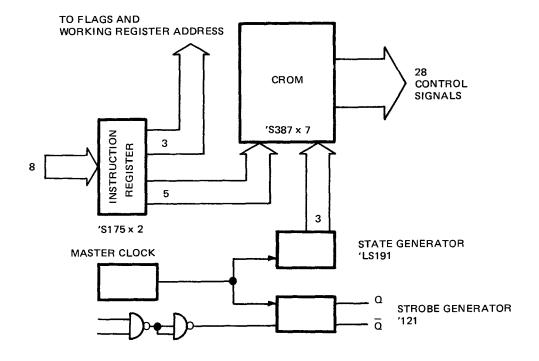

| Chapter IX   | A SCHOTTKY                           | Γ.T.L. MIC  | ROCO    | MPU7  | ΓER    |       |       |       |         |       |     |

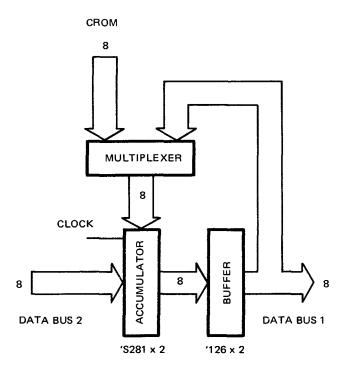

| -            | A Fast Microcor                      | nputer      |         |       |        |       |       |       |         |       |     |

|              | The SN74S281                         | 4-Bit Accus | mulato  | r     |        |       |       |       |         |       |     |

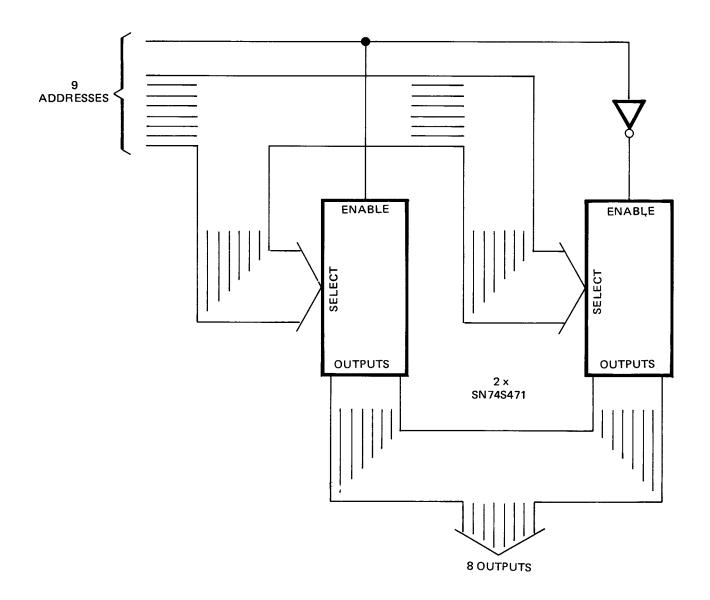

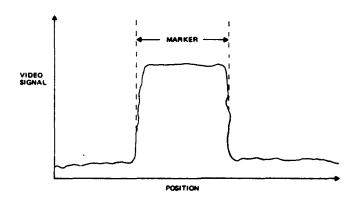

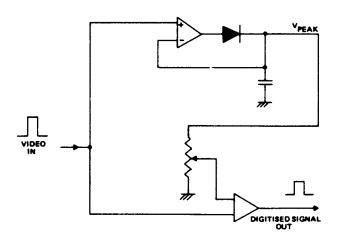

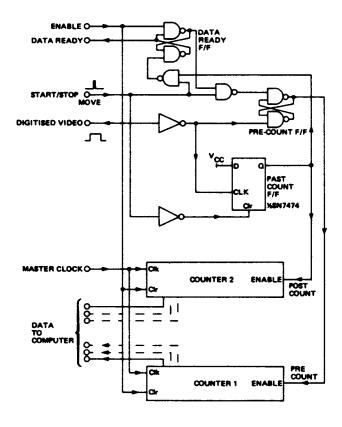

| Chapter X    | USE OF PROGI                         | RAMMARI     | E REA   | ים מ  | NI.Y M | IEMO  | RIES  |       |         |       |     |

| pov. 12      | System Timing (                      |             |         |       |        |       |       |       | • •     | • •   | • • |

|              | Information Che                      |             |         |       |        |       | • •   |       |         | • •   | • • |

|              | High Speed Char                      | ~           |         |       | • •    | • •   | • •   |       |         | • •   | • • |

|              | References                           |             |         |       |        |       | • •   |       |         |       |     |

| Chapter XI   | REFERENCE M                          | IADE CEN    | EDAT    |       | OD A   | (ITO) | A TEI | D EOI | прме    | NIT   |     |

| Chapter Ai   | Operation Operation                  |             | LICKAI  | OK I  | OK A   | OION  | IAIL  | D EQC | JIT MIL | 214 1 | • • |

|              | Circuits                             | ••          | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              | References                           | ••          | • •     | • •   | ••     | • •   | • •   | • •   | ••      | • •   | • • |

| ~            |                                      |             |         |       |        |       | ••    |       |         | ••    | • • |

| Chapter XII  | A UNIVERSAL                          | ASYNCHI     | RONO    | US RI | ECEIV  | ER T  | RANS  | MITT  | ER      | • •   | • • |

|              | Operation                            |             | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              | Supplementary                        | Circuits    | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              | Applications                         | • • • •     | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              | References                           |             | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              | Acknowledgeme                        | ents        | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

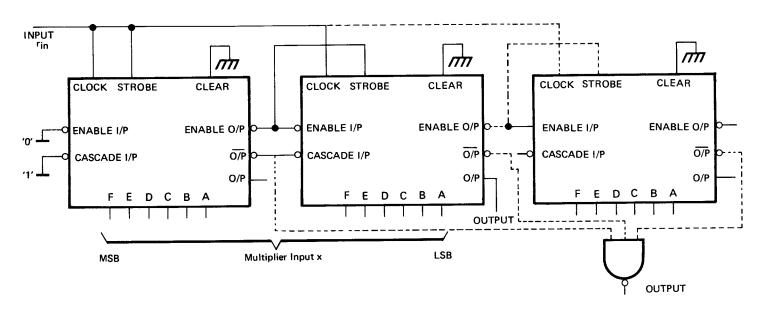

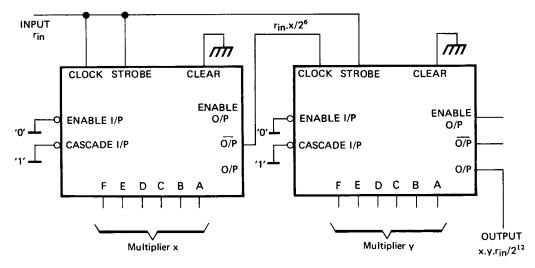

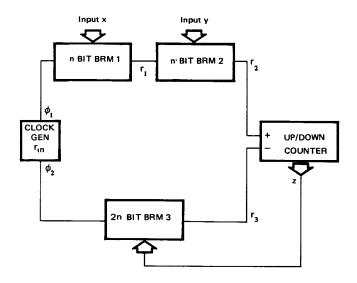

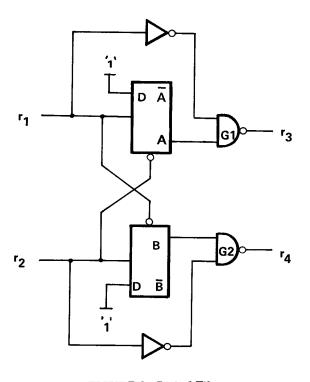

| Chapter XIII | BINARY AND D                         | ECIMAL I    | RATE    | MULT  | riplie | RS    |       |       |         |       |     |

|              | Description                          |             |         |       |        |       |       |       |         |       |     |

|              | Arithmetic Opera                     |             |         |       |        |       |       |       |         |       |     |

|              |                                      |             |         |       |        |       |       |       | • •     |       | - • |

|              | Mathematical On                      | erations    |         |       |        |       |       |       |         |       |     |

|              | Mathematical Op<br>Practical Conside |             | • •     | • •   | • •    | • •   | • •   | • •   | • •     | • •   | • • |

|              |                                      |             |         |       | ••     | • •   |       |       | ••      | ••    | ••  |

|              | Practical Conside                    |             |         | • •   | ••     | • •   |       | ••    | ••      |       | ••  |

|             |                    |          |        |        |         |       |      |     |     |       | Page    |

|-------------|--------------------|----------|--------|--------|---------|-------|------|-----|-----|-------|---------|

| Chapter XIV | PERIPHERAL C       | IRCU     | ITS    |        |         |       |      |     |     | <br>  | <br>183 |

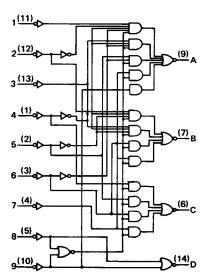

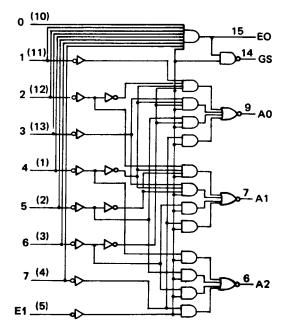

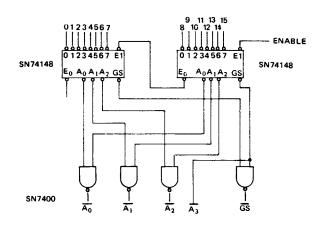

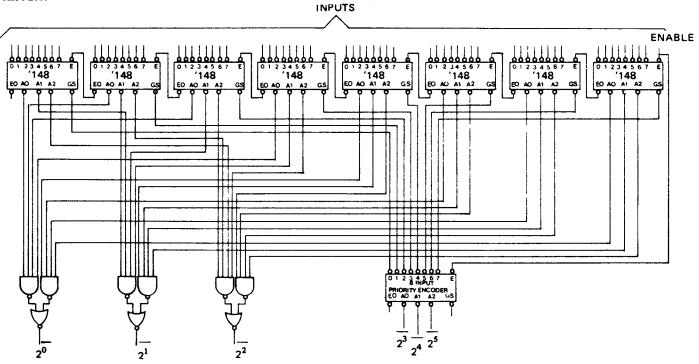

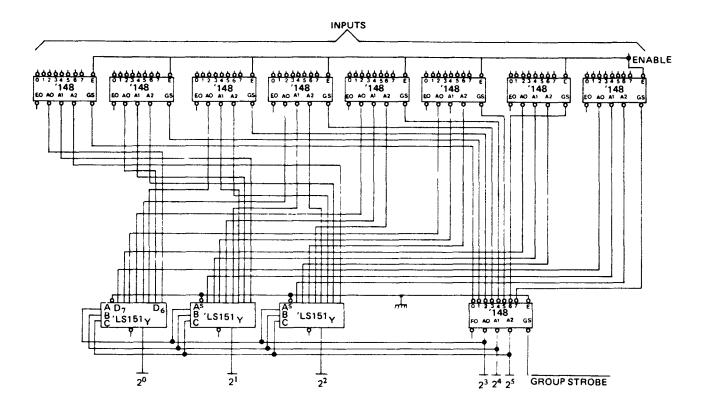

|             | Priority Encoder   | S        |        |        |         |       |      |     |     | <br>  | <br>183 |

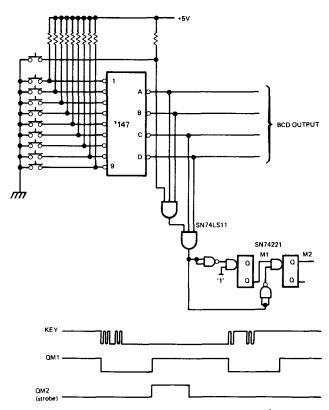

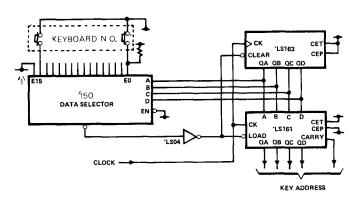

|             | Keyboard Encod     | ers      |        |        |         |       |      |     |     | <br>  | <br>185 |

|             | Digital to Analog  | gue Co   | nverte | ers    |         |       |      |     |     | <br>  | <br>186 |

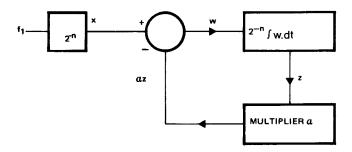

|             | Precision Triangu  | ılar Fı  | ınctio | n Gen  | erator  |       |      |     |     | <br>  | <br>188 |

|             | Reference          |          |        |        |         |       |      |     |     | <br>  | <br>189 |

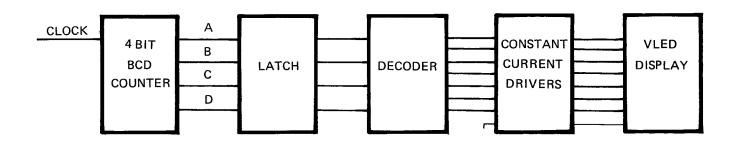

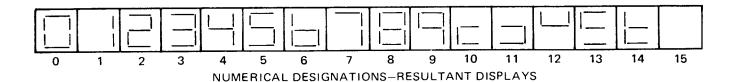

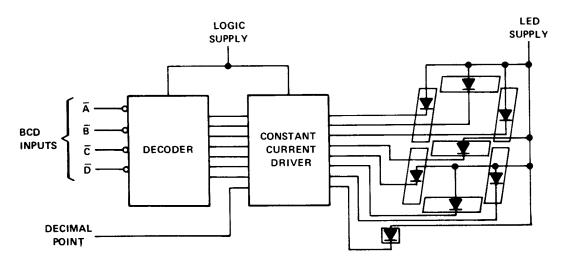

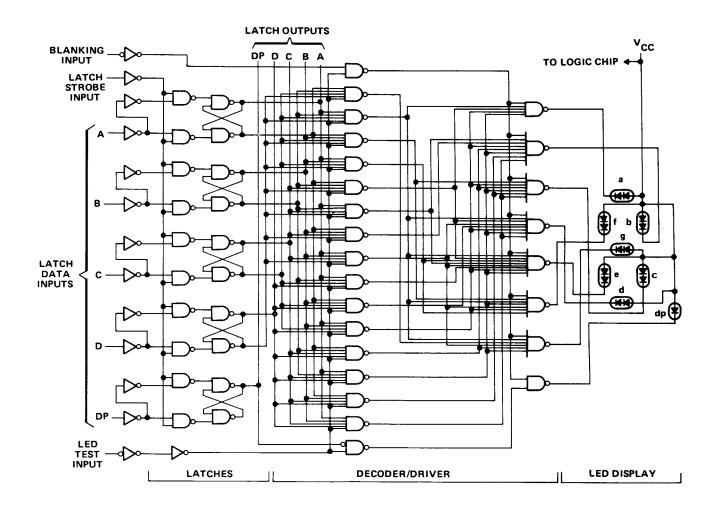

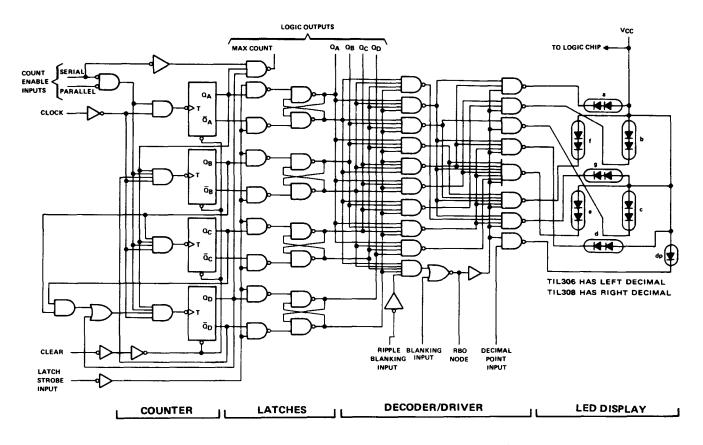

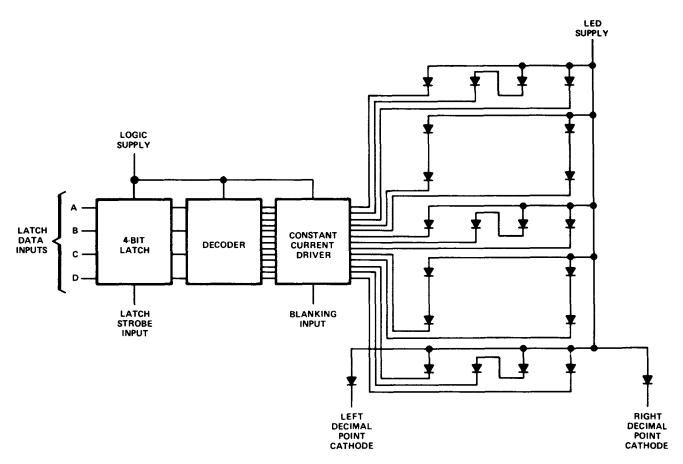

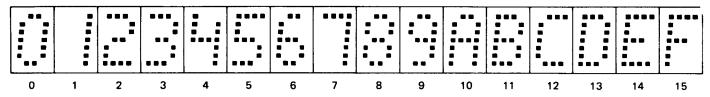

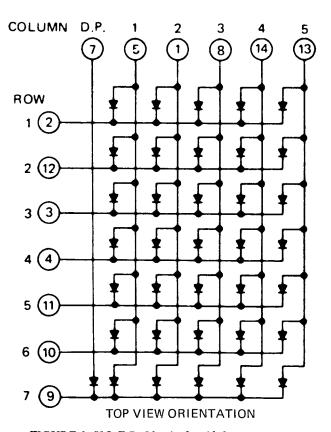

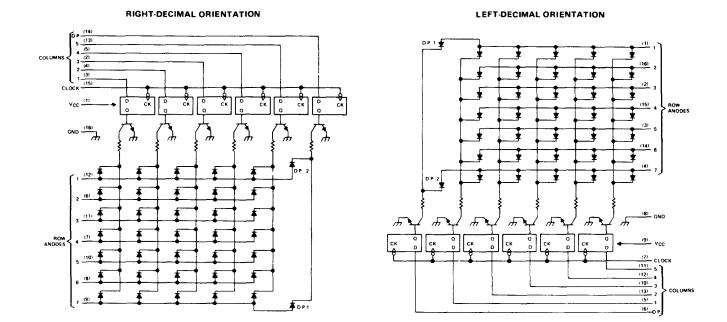

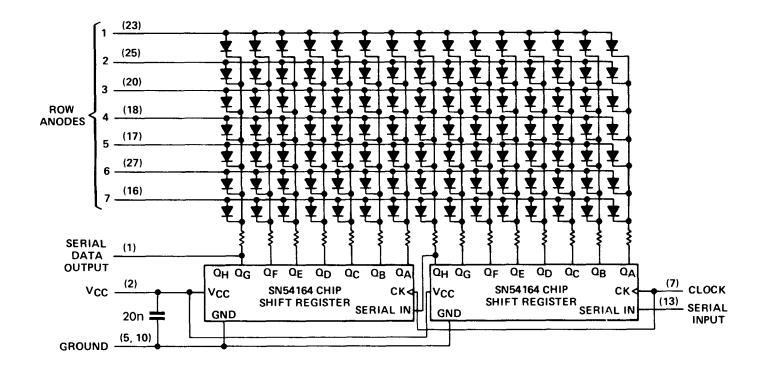

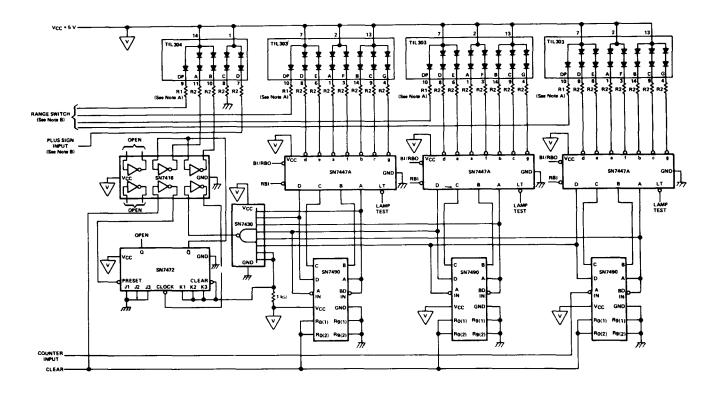

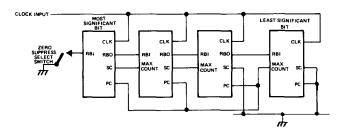

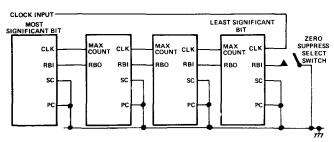

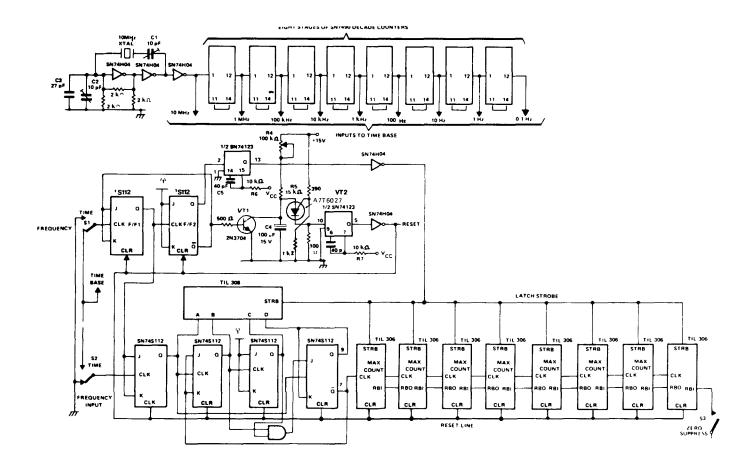

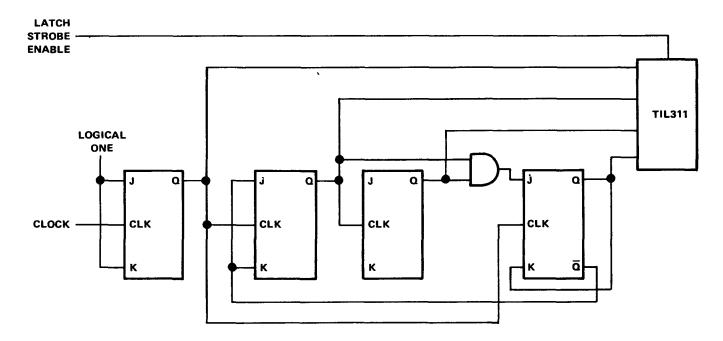

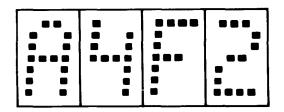

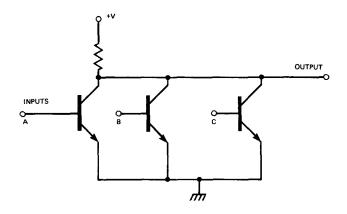

| Chapter XV  | DISPLAY AND        | COUN     | ITING  | CIRC   | CUITS   |       |      |     |     | <br>  | <br>191 |

| C           | Construction       |          |        |        |         |       |      |     |     | <br>  | <br>191 |

|             | Description        |          |        |        |         |       |      |     |     | <br>  | <br>191 |

|             | Applications       |          |        |        |         |       |      |     |     | <br>  | <br>196 |

|             | References         |          |        |        |         |       |      |     |     | <br>  | <br>204 |

|             | Acknowledgeme      | nt       |        |        |         |       |      |     |     | <br>  | <br>204 |

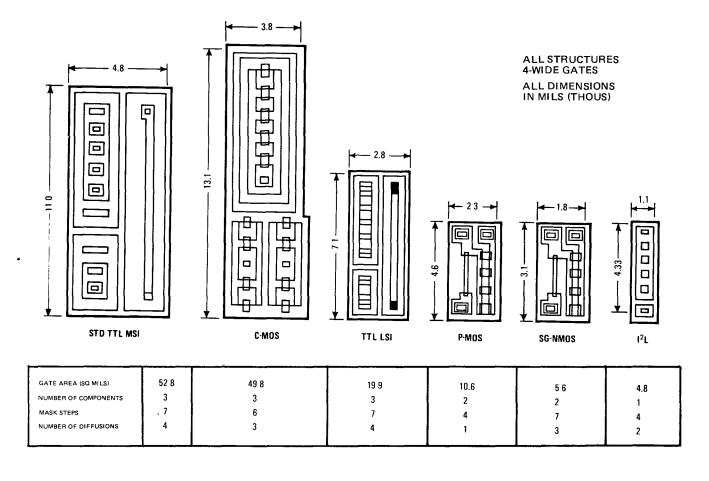

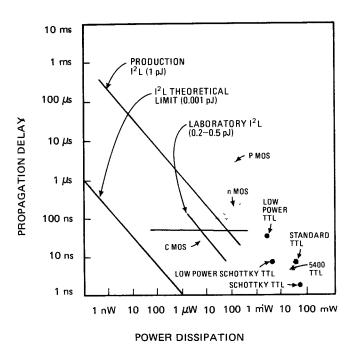

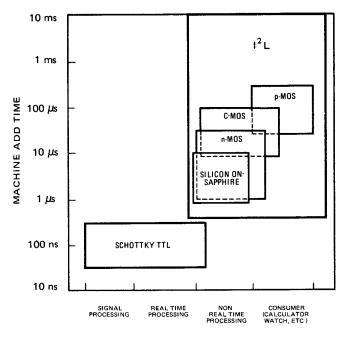

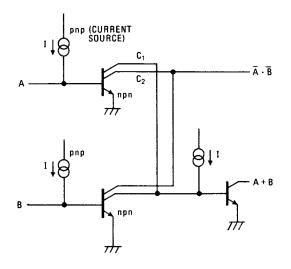

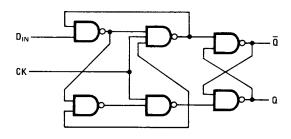

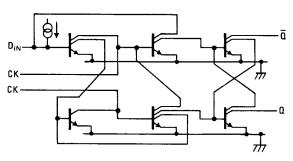

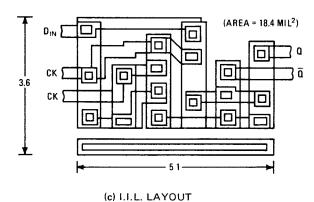

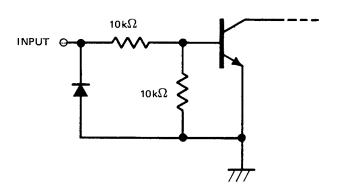

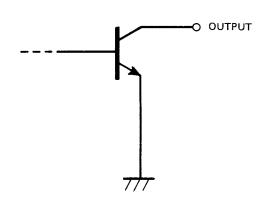

| Chapter XVI | INTEGRATED         |          | TION   | LOG    | IC      |       |      |     |     |       | <br>205 |

| Chapter Avi | Evolution of the   |          |        | LOG    | 10      |       | ••   | • • | • • | <br>• | <br>205 |

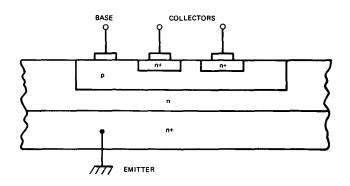

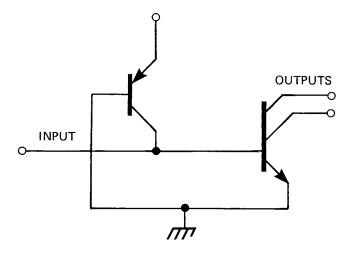

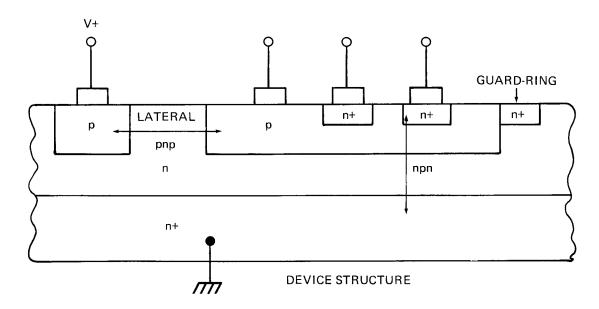

|             | Fabrication 51 the | 1.11.12. | Jutt   | • •    |         |       |      |     |     | <br>  | <br>206 |

|             | Design             |          |        |        |         |       |      |     |     |       | <br>208 |

|             | Power Supplies     |          |        |        |         |       |      |     |     |       | <br>210 |

|             | Applications       | • •      |        |        |         |       |      |     |     |       | <br>211 |

|             | References         |          |        |        |         |       |      |     |     | <br>  | <br>211 |

|             | 110101011000       |          | • •    | • •    | • •     | • •   | • •  |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             |                    |          |        |        |         |       |      |     |     |       |         |

|             | Index              |          |        |        |         |       |      |     |     | <br>  | <br>213 |

|             | Contents of Sem    | icond    | uctor  | Circui | it Desi | gn Vo | lume | Ι   |     | <br>  | <br>218 |

|             | Contents of Sem    |          |        |        |         |       |      |     |     | <br>  | <br>219 |

Contents of Semiconductor Circuit Design Volume III

220

**SECTION 1.**

**POWER CONTROL**

#### I USE OF RECTIFIERS

#### by Jurek Budek and Mick Maytum

Silicon rectifiers/diodes have uses in many electronic and electrical engineering applications. These include power supplies, inverters and converters, amplifiers, servo systems, modulators and demodulators, d.c. restoration, d.c. stabilization and arc suppression. The advantages of silicon devices are their small size and weight, their long-term reliability under adverse conditions of vibration and shock, a high efficiency and their independence of external excitation. A diode/rectifier may be regarded as a non-linear resistive device possessing low electrical resistance, ideally zero, in the forward direction and high resistance, ideally infinite, in the reverse direction. Overall silicon devices approach more closely to the ideal than any other rectifying device. <sup>1</sup>

In the basic half-wave circuit, consisting of a rectifier in series with a single-phase a.c. source and a resistive load, the rectifier functions as a synchronized switch. It allows current to flow each time the source has one particular polarity and interrupts current when the source polarity reverses, so that the load current flows in half-cycle pulses. This pulsating current is unsuitable for most purposes but can be 'smoothed', or made to flow more uniformly, by:

- (a) passing the current through a filter

- (b) increasing the number of phases

- (c) increasing the number of cycles of operation (i.e. half-wave to full-wave circuit).

For most low and medium power applications, where the source is a single phase a.c. supply, the rectified current is smoothed by a filter consisting of one or more reactive elements. The amount of ripple that can be tolerated governs the complexity of the filter which may be either:

- (a) a capacitor-input filter, which presents a shunt capacitance to the rectifier output, or

- (b) a choke-input filter, which presents a series inductance to the rectifier output.

In certain applications, such as lightweight power supply units for airborne equipment, three phase circuits are commonly used as the output requires very little filtering and the higher efficiency and good power factor of the three-phase circuit also reduce the weight of the unit.

For high power rectification, where large currents are involved, the filter components tend to be bulky and expensive and here also it is more convenient to increase the number of phases and dispense with the filter entirely, e.g. 24 phases for the power supplies of electro-chemical

equipment. The most common applications for large high voltage (h.v.) power supplies are radar, radio transmitters, travelling wave tubes, microwave, inductive and dielectric heating. The circuit most frequently used for these supplies is the three phase bridge. The design information given in the last part of this chapter, therefore, is for a three phase bridge, together with efficiency and power factor calculation.

#### SINGLE-PHASE RECTIFIER CIRCUITS

#### **Half-Wave Circuit**

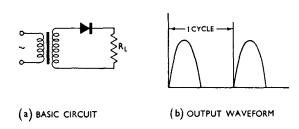

This circuit (Figure 1) is simple, uses only one rectifier and does not need an intermediate transformer for some applications. Its use is restricted to low output powers since its efficiency is low and the output voltage has a large low-frequency ripple, which makes smoothing more difficult. In addition, if a transformer is used, d.c. magnetization of the core occurs.

FIGURE 1. Half-Wave Circuit

#### **Full-Wave Circuits**

The two main types of full-wave circuits are:

- (a) the centre-tapped transformer circuit

- (b) the bridge circuit

A transformer with a centre-tapped secondary winding can be used with the bridge circuit when a three-wire d.c. supply is required. These circuits are used for the larger output powers since they are more efficient than the half-wave circuit, give a smaller ripple voltage at twice the supply frequency, and produce only negligible d.c. magnetization in the core of the transformer.

The Centre-Tap Transformer (Bi-Phase) Circuit: As shown in Figure 2 this consists of two half-wave circuits operating in push-pull on alternate half-cycles, the single-phase supply being effectively split into two phases.

FIGURE 2. Centre-Tap (Bi-Phase) Circuit

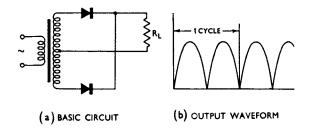

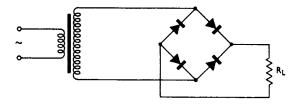

The Bridge Circuit: Where higher d.c. output voltages are required the bridge circuit (Figure 3) has several distinct advantages over the centre-tap circuit. For a device of a given inverse voltage rating the d.c. output voltage obtainable using the bridge circuit is twice that using the centre-tap circuit. The bridge circuit allows the use of transformers without the complication of a centre-tapped secondary winding. This is particularly advantageous at high voltages as the number of turns in the secondary of the bridge circuit transformer is half that of the centre-tapped secondary for a given output, or at high frequencies where the number of turns is very low or an odd number. The current flows continuously in the secondary of the bridge circuit transformer and only half the time in each half of the winding of the centre-tapped transformer. Hence the transformer for the bridge circuit has a higher utilization of the winding space. These factors lead to a simpler and smaller transformer for the bridge circuit and in certain cases one may not even be required.

FIGURE 3. Single-Phase Bridge Circuit

The Centre-Tapped Bridge Circuit: The use of a centre-tapped transformer secondary in the bridge circuit is a convenient means of splitting the output voltage for applications such as audio, operational, differential amplifiers, etc. In this case there is still no d.c. saturation of the transformer core, even when only one-half of the output is loaded. The output should not be followed by a single capacitor filter as the alternating current can flow through the unloaded input capacitor to the load and upset the balance when only half the output is loaded. Both 'half' voltage and full voltage contain the same percentage ripple at twice the supply frequency. The ripple in the halves of the output is in anti-phase and the effect is to cancel in the equipment it feeds, which may allow some reduction in smoothing components.

#### Voltage Multiplier Circuits<sup>2</sup>

These circuits utilize the principle of charging capacitors in parallel from the a.c. input and adding the voltages across them in series to obtain d.c. output voltages higher than the source voltage. With these circuits filtering must necessarily be of the capacitor-input type.

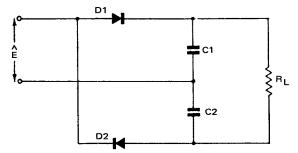

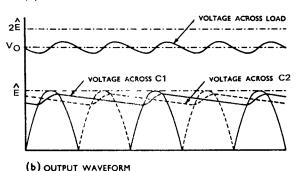

Voltage Doublers: Conventional and cascade circuits are considered together for ease of comparison. In the conventional circuit (Figure 4) the capacitors C1 and C2 are

(a) BASIC CIRCUIT

FIGURE 4. 'Conventional' Voltage Doubler

(a) BASIC CIRCUIT

(b) OUTPUT WAVEFORM

FIGURE 5. 'Cascade' Voltage Doubler

each charged, during alternate half-cycles, to the peak value of the alternating input voltage, thus giving an output of twice the a.c. peak voltage.

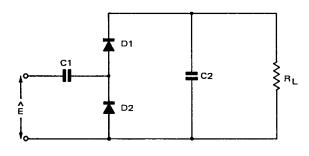

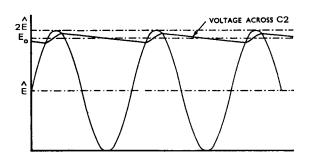

In the cascade circuit (Figure 5) capacitor C1 is charged to the peak value of the a.c. input voltage through diode D2 in one half-cycle and in the other half-cycle it discharges in series with the a.c. source through diode D1 to charge capacitor C2 to twice the a.c. peak voltage.

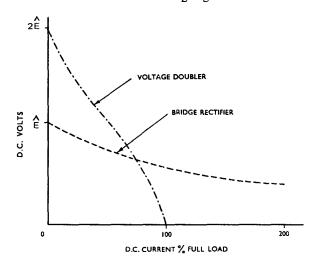

The 'conventional' circuit has the slightly better regulation and since the ripple frequency is twice the supply frequency filtering is easier, the percentage ripple being about the same in both cases. In addition, both capacitors are rated at the a.c. peak voltage, whereas capacitor C2 in the 'cascade' circuit has to be rated at twice this figure. With both circuits the peak inverse voltage across each device is twice the a.c. peak. The 'cascade' circuit, however, has the advantage of a common input and output terminal and, therefore, permits combination of units to give higher order voltage multiplications. The regulation of both circuits is poor so that only small load currents can be drawn. A typical output characteristic for the conventional circuit is given in Figure 6 and the same curve is approximately correct for a practical cascade circuit in which the value of  $\omega CR_L$  is greater than 10.

FIGURE 6. Output Characteristics of some Single-Phase Circuits

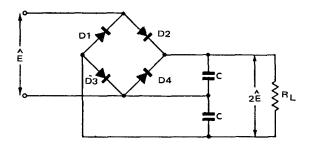

The Bridge Voltage Doubler circuit, as shown in Figure 7, is a combination of the conventional voltage doubler and the bridge rectifier circuit. Although often shown in literature, as the only function of the extra diodes, D3 and D4, is to prevent voltage reversal on the output capacitors due to, say, an output short circuit, this circuit is very little used in practice.

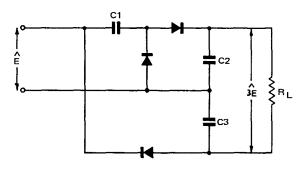

Voltage Triplers: The circuit, shown in Figure 8, adds the output of a cascade voltage doubler and a half-wave rectifier in series to give an output voltage three times the a.c. peak. Capacitors C1 and C3 are rated at the a.c. peak voltage and C2 at twice this figure, the peak inverse voltage (p.i.v.) across each rectifier being twice the a.c. peak.

In pulse circuits the a.c. waveform is unsymmetrical resulting, say, in the positive excursion of the waveform

FIGURE 7. Bridge Voltage Doubler

being orders of magnitude greater than the negative excursion. Thus there is very little difference between full voltage doubling and simple half-wave rectification of the positive peak. When applied to voltage multipliers this means that twice the number of stages is required to produce slightly more than three times the positive peak. This has resulted in the 'loose' terminology of the name 'voltage tripler' being applied to five or six stages of voltage multiplication, e.g. in colour television.

FIGURE 8. Voltage Tripler

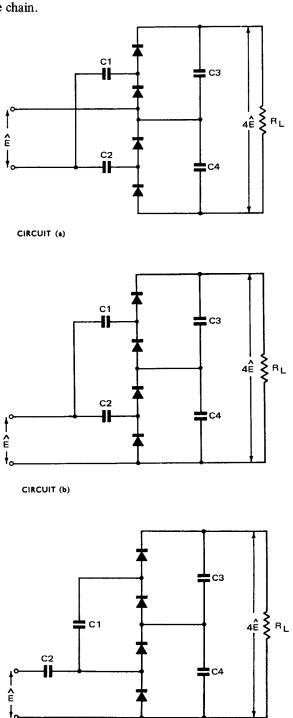

Voltage Quadruplers: Three alternative circuits are shown in Figure 9. Circuit (a) is a symmetrical arrangement with capacitors C3 and C4 rated at twice the a.c. peak voltage. Circuits (b) and (c) have a common input and output terminal and, therefore, can be extended for further voltage multiplication. In circuit (b) capacitor C1 is rated at three times the a.c. peak voltage and C3 and C4 at twice the a.c. peak, while capacitors C1, C3 and C4 are rated at twice the a.c. peak in circuit (c). However, the input capacitor C2 in the latter circuit has to have twice the capacitance of that in (b). The peak inverse voltage across each device in all these circuits is equal to twice the peak voltage.

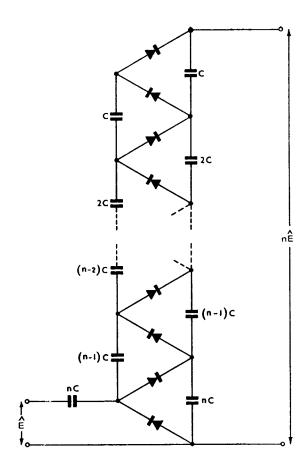

n-Stage Voltage Multiplication (Cockcroft-Walton Circuit): The voltage quadrupler circuit (c) can be further extended as shown in Figure 10 to obtain higher d.c. voltages. The voltage ratings of all 'ladder' capacitors and devices are twice the a.c. peak throughout but the capacitance values have to be graded as shown for an optimum design. However in practice the designer will usually opt for the same value of capacitor throughout to minimize the number of components required, stored, etc. The value of C will be the same as that for the cascade voltage doubler, which is the basic unit for this circuit. The

value of the load resistance for this basic unit should be taken as  $\frac{1}{n}$ th the value of the load resistance for the voltage multiplier chain, where 'n' is the number of cascade units in the chain.

FIGURE 9. Voltage Quadrupler Circuits

#### Capacitor-Input Filter<sup>3</sup>

CIRCUIT (c)

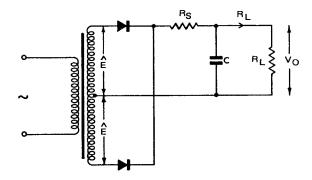

Circuit Configuration: To illustrate the behaviour of capacitor-input circuits the full wave centre-tap circuit is used with a reservoir capacitor C across the resistive load

FIGURE 10. n-Stage Voltage Multiplication Circuit

FIGURE 11. Capacitor-Input Filter with Centre-Tap Circuit

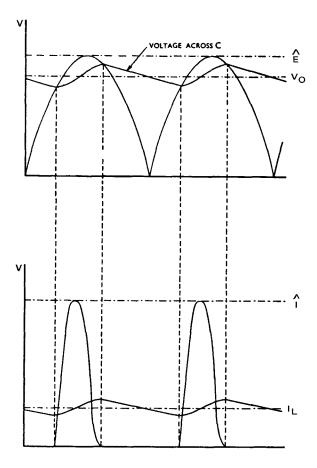

$R_L$ , as shown in Figure 11. The total source resistance through which the capactior charging current flows is represented by  $R_S$ ; this includes the resistance of one-half of the secondary winding, the reflected, primary resistance, the forward resistance of the devices and any series added resistance. The action of the circuit is demonstrated by the waveforms of Figure 12. The capacitor C acts as a reservoir. As the secondary voltage approaches peak value and exceeds the voltage across capacitor C one of the diodes conducts, charging the capacitor almost to the a.c. peak voltage. This charging period is only a small part of the cycle and during the rest of the cycle capacitor C discharges through load resistance  $R_L$ , the voltage across it falling

almost linearly. The values of the peak current through the rectifiers,  $\hat{I}$ , and the d.c. output voltage,  $V_O$ , depend in a complex manner on the following factors:

- (a) The load resistance R<sub>L</sub>

- (b) The filter capacitor C

- (c) The leakage reactance of the transformer.

- (d) The source resistance R<sub>S</sub>

FIGURE 12. Waveforms for Capacitor Input Filter Circuit

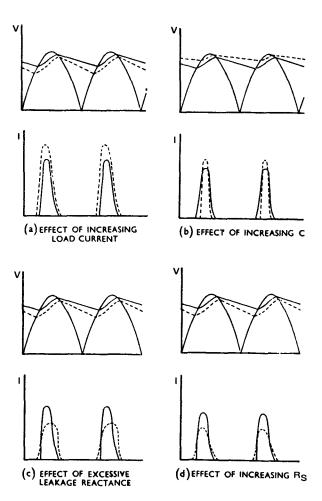

The effects of these on the charging current waveforms are illustrated in Figure 13.

In a particular power supply problem the d.c. output voltage, load current and ripple content conditions required are usually known. The circuit design meeting these requirements must also ensure that the rectifier units are not operated under conditions in excess of the ratings quoted by the manufacturer. The major ratings are:

- (i) Peak inverse voltage, p.i.v.

- (ii) Average rectified forward current, Io.

- (iii) Recurrent peak forward current, Î

- (iv) Surge current at switch-on, Is.

The worst forward current condition occurs at switch-on when a large initial charging current flows through the

FIGURE 13. Effect of Various Parameters on the Waveforms

device to the input capacitor. At the instant of switching on the a.c. supply the capacitor charging current is equal to the instantaneous secondary voltage divided by the total source resistance, Rs and therefore has a maximum possible value  $E/R_S$ . In the majority of circuits the time constant  $CR_S$  is small compared with the half-cycle period of the a.c. supply, so that the charging current falls very rapidly to a value much lower than that at switch-on. If the time constant is large compared with the half-cycle period the charging current alternately in each device will be approximately a half-sine wave pulse of peak value less than E/R<sub>S</sub>, and will be repeated in successive alternate half-cycles with exponentially decreasing amplitude. The surge current in the recurrent peak current may have to be limited by the addition of extra resistance in the charging path at the cost of efficiency and regulation. This is particularly relevant in the case of the modern switching mode inverter which operates directly from the bridge rectified supply by using high voltage transistors to provide a.c. mains regulation.

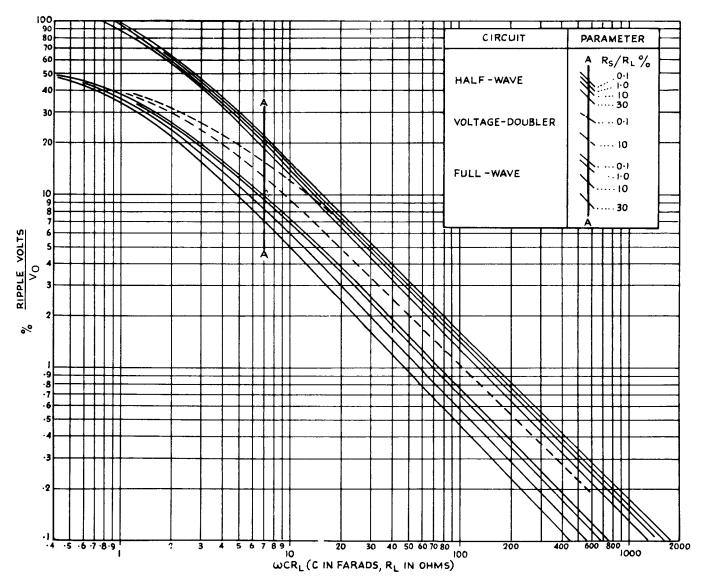

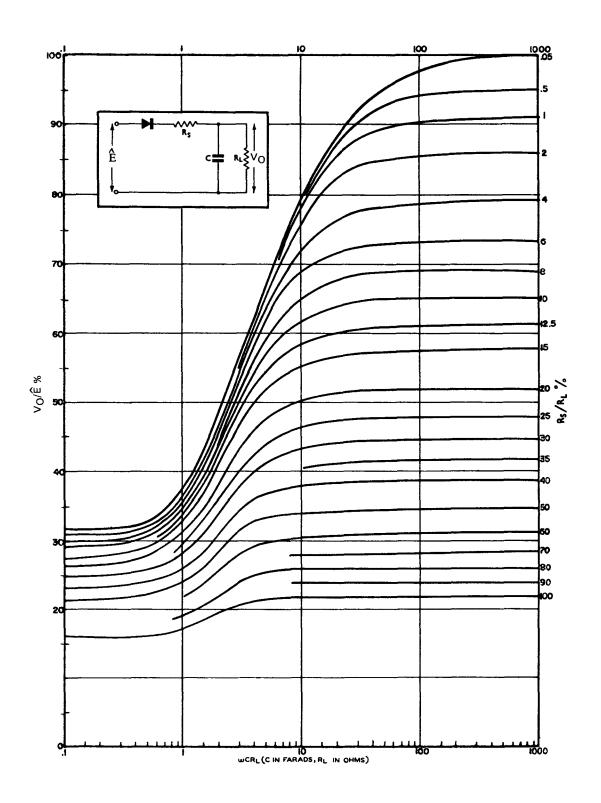

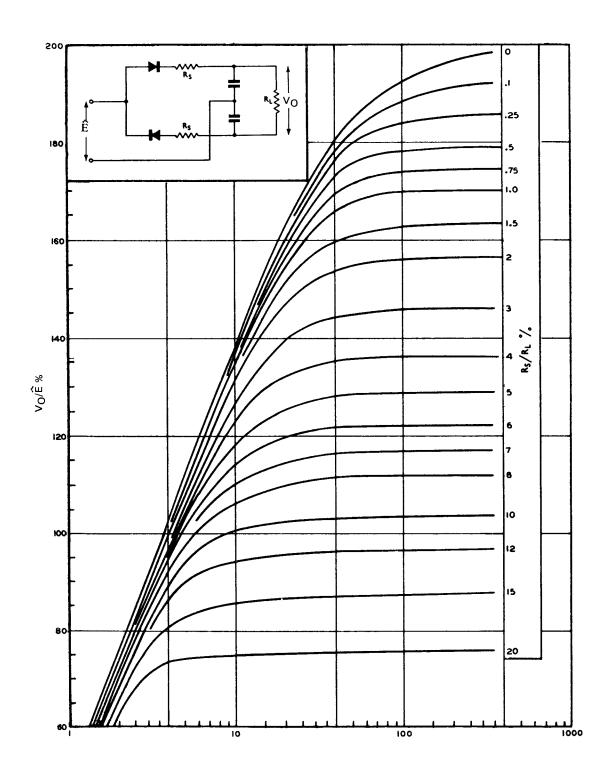

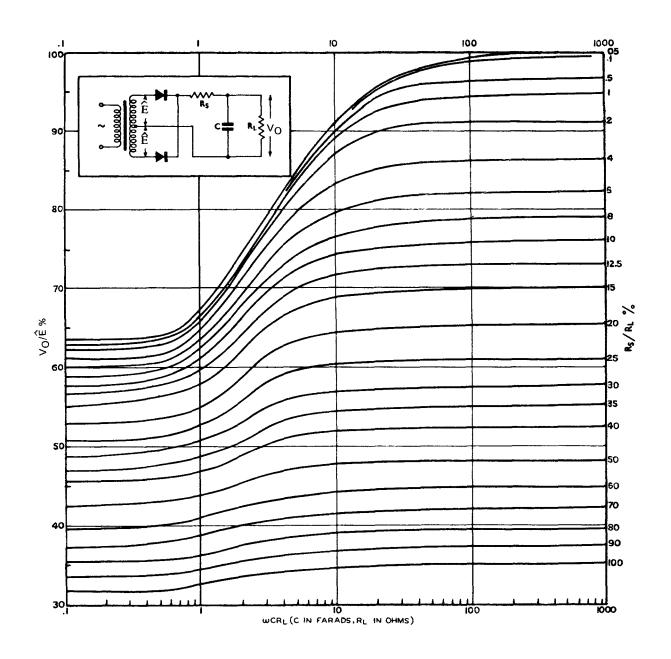

The calculations involved in the design are simplified by the series of curves derived by O. H. Schade<sup>4</sup> for the half-wave, full-wave and voltage doubler circuits. They define:

- (a) the percentage ripple content of the output voltage, as given in Figure 14.

N.B. This is expressed as an r.m.s. value of the waveform and the total peak to peak value is approximately √12 times this.

- (b) the ratio of d.c. output voltage to peak input voltage. Figure 15 is for half-wave, Figure 16 for full-wave and Figure 17 for voltage doubler circuits.

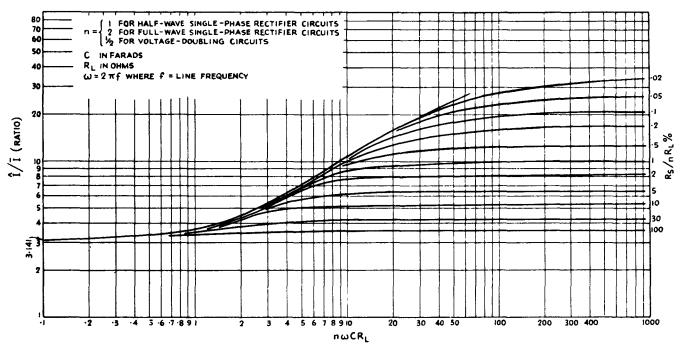

- (c) the ratio of peak to average current per rectifier, Figure 18.

They are drawn for a range of supply frequencies, capacitances, and load and source resistances.

It can be seen that  $R_S$  affects the performance of the circuit considerably. The forward resistance of silicon rectifiers is extremely small and, since it is normally a negligible part of the total source resistance, a value corresponding to the voltage drop at the mean forward current can be assumed. The total value of  $R_S$  must be sufficient to restrict peak rectifier resistance leads to loss of efficiency and poor regulation due to the voltage drop

across it. The minimum value of filter capacitance C is determined by the maximum ripple content and the load resistance. In addition, if good regulation is required the value of  $\omega CR_L$  should lie to the right of the upper bend of the curves in Figures 15 to 17. However, when a large capacitance is needed to achieve this, excessive peak currents are incurred, imposing an additional limit on the maximum current which can be drawn.

The effect of transformer leakage reactance is to decrease the peak currents through the rectifiers, as shown in Figure 13(c), and for low powers is small. However for large powers it must be taken into account as discussed later.

In a typical circuit  $R_S$  is of the order of 6% of  $R_L$  and the ripple voltage about 5% of the mean d.c. output. Under these conditions the relationships given in Table 1 are approximately correct for a sinusoidal input voltage. They give an indication of the performance of capacitor input circuits, but since peak current conditions are critical it is necessary in the design of particular circuits to adopt the detailed analysis illustrated by the examples. The

\* FIGURE 14. Root-Mean-Square Ripple Voltage for Capacitor-Input Circuits

\* (By permission from O. H. Schade, Proc. I.R.E., July 1943,)

\* FIGURE 15. Relation of Applied Alternating Peak Voltage to Direct Output Voltage in Half-Wave Capacitor-Input Circuits.

\* FIGURE 17. Relation of Applied Alternating Peak Voltage to Direct Output Voltage in Capacitor-Input Voltage Doubler Circuits.

current ratios  $I_L/I_O$  in the table indicate a typical derating to allow for the peak currents through the rectifiers,  $I_O$  being the maximum average forward current which each rectifier can pass into a resistive load. A further derating of

Table 1. Typical Voltage & Current Relationships

|                                  | Half-<br>wave | Centre-<br>Tap | Bridge | Voltage<br>Doubler |

|----------------------------------|---------------|----------------|--------|--------------------|

| V <sub>O</sub> /E <sub>rms</sub> | 1.2           | 1.2            | 1.2    | 2                  |

| P.i.v./E <sub>rms</sub>          | 2.8           | 2.8            | 1.4    | 2.8                |

| I <sub>L</sub> /I <sub>O</sub>   | 0.8           | 1.6            | 1.6    | 0.8                |

this value is required  $(l_{av})$  when capacitative smoothing is used, to account for the high peak currents.

**Practical Example:** Consider the mains power supply for the Stereo Texan Amplifier, of Figure 12, page 165 of Semiconductor Circuit Volume II. The required specification is:

No load output voltage,  $V_0$ , = ±32V (Determined by the output transistor voltage ratings)

Minimum output voltage,  $V = \pm 17V$ , when both channels driven at 16W into  $8\Omega$ .

Peak to peak ripple voltage under these conditions,  $E_{R}$ , = 5%.

\* FIGURE 16. Relation of Applied Alternating Peak Voltage to Direct Output Voltage in Full-Wave Capacitor-Input Circuits.

\* FIGURE 18. Relation of Peak Current to Average Current per Rectifier in Capacitor-Input Circuits.

The circuit chosen is a complex compromise between cost, bulk, efficiency and regulation. Under normal music conditions, over 20W are available on each channel. Continuous sinewave drive conditions represent a heavy current demand on the power supply and results in the supply rail falling to approximately 17V (although 16W is available from both channels under these conditions). This relatively poor regulation provides excellent short circuit protection for the amplifiers it feeds.

The circuit is analysed as two opposite polarity biphase rectifier circuits:

The peak no load transformer winding voltage, E, is given by

$$\hat{\mathbf{E}} = \hat{\mathbf{V}}_{O} + \check{\mathbf{V}}_{F}$$

where  $V_F$  is the diode forward drop at low currents ( $\simeq$ 0:6V).

Therefore

$$\hat{E} = 32 + 0.6 = 32.6V.$$

$E_{r.m.s.} = 32.6/2^{\frac{1}{2}} = 23V \text{ (No load)}$

The twin output power of 16W sinewave into  $8\Omega$  is equivalent to a single load of 32W into  $4\Omega$ . The average power supply current  $I_L$  for this is

$$I_L = (32/4)^{\frac{1}{2}} 2^{\frac{1}{2}}/\pi = 4/\pi$$

= 1.27A

The effective power supply load R<sub>L</sub> on each rail is

$$R_{L} = V_{o}/I_{L} = 17/1 \cdot 27$$

$$= 13 \cdot 4\Omega$$

As neither the effective rectifier source resistance,  $R_S$ , or the value of the reservoir capacitor C1 are known, some iteration is required. The large fall in output voltage with loading shows  $R_S/R_L\%$  to be high, say 40%. Using this value and recognising the 5% peak to peak ripple rating corresponds approximately to  $5/12^{\frac{1}{2}} = 1.5\%$  r.m.s. ripple, Figure 14 shows a  $\omega CR_L$  factor of 30 is required to achieve this.

Therefore C1 =  $30/2.\pi.100.\ 13.4 = 3.600\mu F.$

The average to peak to peak ratio is given by

$(\check{E}_O + \hat{V}_F)/(\hat{E}_O + \check{V}_F)$  where  $\hat{V}_F$  is the diode forward drop at high currents (-1V).

i.e.

$$(17 + 1)/(32 + 0.6) = 0.49$$

i.e.  $49\%$ .

This from Figure 16 with this ratio 49% and  $\omega CR_L$  = 30

$$R_S/R_L = 48\%.$$

Therefore

$$R_S = 13.2 \times 0.48$$

$$= 6.4$$

The average current Iav per diode will be

$$I_{\rm I}/2$$

or  $1.27/2 = 0.63$ A

Figure 18 shows an I/Iav value of 4, hence

$$I = 0.63 \times 4 = 2.5 A.$$

The maximum rectifier surge current, Is will be

$$E/R_S = 32.6/6.4 = 5A$$

and the working p.i.v. will be 2Ê or 65V.

These ratings can be adequately met by a 1N4002 diode.

Thus the specification arrived at is:

Diodes 1N4002 Reservoir Capacitors 3,500 $\mu$ F at 40V Effective Source Resistance  $R_S = 6.4\Omega$ .  $E_{r.m.s.}$  23V -0 - 23V No load.

If the power supply performance was of a highly critical nature the above working would be modified to account for component, loading and mains supply tolerances.

#### Check

The transformer specified for the amplifier is a Gardeners SL20 and a sample of one of these had the following characteristics. (Design values in brackets.)

$R_P = 147\Omega$   $R_S = 1.9\Omega/\text{winding}$  ( $R_S = 6.4\Omega$ ) No load rectified voltage 33V (32V) Maximum load rectified voltage = 18V (17V) Percentage ripple at maximum load = 1.45V peak or 8% (5%) Rectifier repetitive peak current = 3.2A (2.5A)

Practical and design performance figures differ mainly due to the rectifier source resistance being slightly lower than the design value at

$$2 \times \frac{142}{([33 + 0.63]/245 \times 2^{1/2})^2 + 1.9}$$

$$= 3.1 + 1.9$$

$$= 5\Omega$$

Note the effective referred primary resistance must be doubled to account for the currents of both the positive and negative rail rectifiers.

#### **Choke Input Filter**

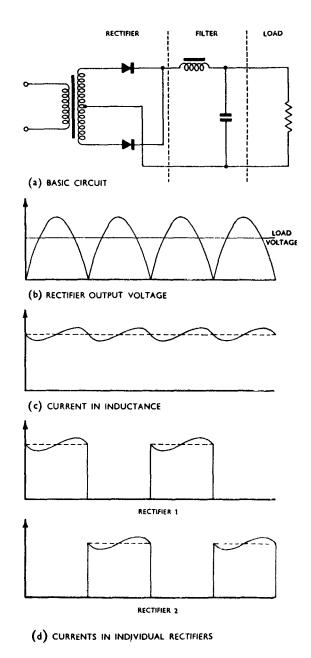

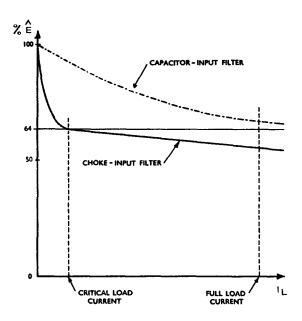

In smaller equipments choke input filters are nowadays too costly and bulky to be employed. Their main application is therefore in industrial systems where large amounts of power are involved.

Choke-input circuits are shown in Figures 19 and 20. In the ideal situation when the choke has infinite reactance and zero resistance the load current is constant and all the ripple voltage is developed across the choke. The current is transferred instantly from one rectifier to another each time the supply voltage passes through zero. In Figures 19 and 20, the broken waveforms refer to the case of infinite

inductance and the solid curves to finite inductance. The choke inductance must be above that value which just causes the pulsating current from the rectifiers to become continuous and consequently prevents the current in the filter from falling to zero in any part of the cycle. This value is known as the 'Critical Inductance'. When the inductance is less than the critical value the circuit behaves as a capacitor-input circuit. In practice an inductance double the critical value, known as the 'Optimum Inductance', is used. The effectiveness of the choke depends on the time constant L/R<sub>L</sub>, so that the value of critical inductance varies inversely as the load current. Hence as the minimum load current decreases the value of choke inductance required increases. In view of this a 'swinging choke' can be used to advantage. With this type of choke the inductance decreases with increase of d.c.

FIGURE 19. Choke-Input Filter with Centre-Tap Circuit

current, due to saturation of the core. Its value at low currents can be much larger than that of a constant inductance choke (such as is required in additional filter sections) of the same dimensions. The decrease of choke inductance as load current increases is not inconvenient since the critical inductance also decreases at high load currents. Usually the choke is designed to have the optimum inductance at minimum load current, so that filtering is effective over the entire current range. If the load current is decreased below the normal minimum it eventually reaches a value at which the critical inductance becomes equal to that of the choke used. This value is known as the critical load current, I<sub>C</sub>, for the choke (see Figure 21) At load currents less than this the circuit behaves as a capacitor-input filter circuit. When such small

FIGURE 20. Choke-Input Filter with Three-Phase Half-Wave Circuit

load currents are required the deterioration in regulation can be avoided by connecting a 'bleeder' resistance permanently across the load to prevent the current through the choke from falling below the critical value.

The ratio of peak current per rectifier to load current depends on the type of circuit and the choke inductance. In the ideal case each rectifier passes the entire load current for part of each cycle, except in the three-phase double star circuit where each carries only half the load current. For a critical inductance choke the peak current is twice the load current.

The waveforms of Figures 19 and 20 neglect the effect of transformer leakage reactance which prevents instantaneous transfer of current from one rectifier to another. In practice the waveforms are modified as described later in the three-phase bridge design.

#### **Additional Filter Sections**

When the ripple voltage must be reduced to an extremely low value which cannot be achieved with a single section, it used to be the practice to use further CR or LC filter sections. Nowadays this function has been replaced by switching mode regulators unless very large power is involved. In addition switching mode regulators can accommodate very large ripple percentages which permit economies in the size of the reservoir capacitor and the transformer.

FIGURE 21. Output Characteristics of Input-Filters

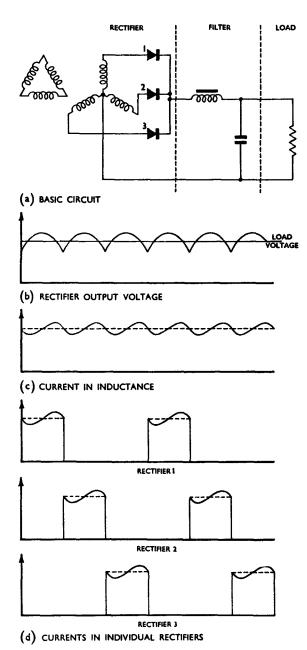

#### THREE-PHASE RECTIFIER CIRCUITS

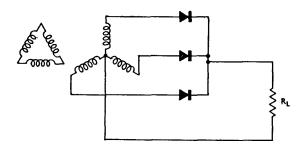

#### Half-Wave Circuit

This is the simplest of the three-phase circuits (Figure 22) using the minimum number of devices. It consists essentially of three single-phase half-wave circuits, each device carrying the current for one-third of the cycle. The obvious advantages of using a three-phase a.c. supply are higher efficiency and lower ripple content, which is at three times the supply frequency. In addition, if the transformer windings for all three phases are suitably arranged, i.e. in 'zig-zag' connection, on the same core no d.c. magnetization of the core will be produced. This circuit is used for comparatively low power outputs at voltages less than half the rated p.i.v. of the devices.

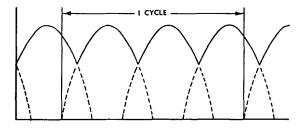

#### Centre-Tap Circuit

This circuit, known as a 'diametric' connection and shown in Figure 23, may be regarded as two three-phase half-wave circuits displaced in phase by 60° and operating in parallel. The current in each rectifier flows for one-sixth of a cycle, giving a smoother output with a ripple frequency six times that of the supply. The efficiency is higher than that of the three-phase half-wave circuit and this circuit is used for larger powers at voltages less than half the rated p.i.v. of the devices. As all the devices have a common connection the 'packaging' of the power supply unit is simplified.

#### **Double Star Circuit**

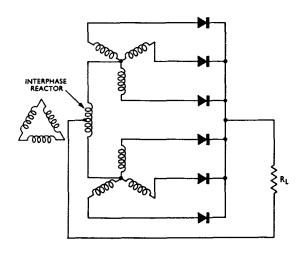

This circuit (Figure 24) differs from the previous one by the introduction of an interphase reactor between the two half-wave circuits. This reactor enables the two circuits to operate independently so that each rectifier conducts for

(a) BASIC CIRCUIT

(b) OUTPUT WAVEFORM

FIGURE 22. Three-Phase Half-Wave Circuit

one-third of the cycle instead of one-sixth. The peak current through each rectifier is reduced to half that in the previous case because at any instant there are two rectifiers carrying current. This reduces the current rating required for each rectifier but the p.i.v. across them is twice the peak phase voltage. The circuit has applications similar to the previous one where the reduction in the cost of the rectifiers due to their lower current ratings would more than offset the cost of the interphase reactor. For the lower voltage, heavy current circuit this arrangement is the most efficient as the rectifier losses' consist of the single rectifier loss and not two in series as in the following bridge circuit.

(a) BASIC CIRCUIT

(b) OUTPUT WAVEFORM

FIGURE 23. Three-Phase Centre-Tap Circuit

FIGURE 24. Three-Phase Double Star Circuit

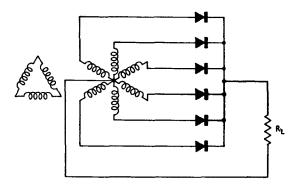

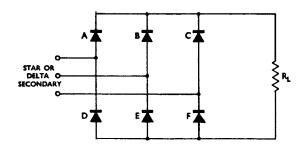

#### **Bridge Circuit**

In this circuit (Figure 25) full-wave rectification is obtained from each phase. At any instant, excluding a short circuit condition, two rectifiers conduct simultaneously and in series in the sequence AF-FB-BD-DC-CE-EA giving six peaks per cycle in the output. This is one of the circuits most frequently used with semiconductor devices. It has the high efficiency and low ripple content of the previous circuits but requires a smaller transformer and no interphase reactor. The transformer secondary may be either star or delta wound as no neutral point is required. It is used for higher output voltages, as the p.i.v. across each rectifier is half that in the centre-tap circuit and the a.c. voltage required for a given d.c. output is the lowest of any circuit discussed.

#### Centre-Tapped Bridge Circuit

When a three-wire d.c. output is required, a three-phase bridge circuit can be used with a centre-tap on a star-connected transformer secondary winding. When

FIGURE 25. Three-Phase Bridge Circuit

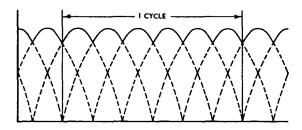

FIGURE 26. Three-Phase Voltage Doubler

FIGURE 27. Three-Phase Bridge Doubler

current is drawn from only one-half of the output the circuit operates as a three-phase half-wave circuit. The ripple content is then higher than when both halves are in use and it is at three times the supply frequency.

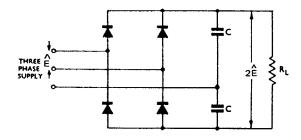

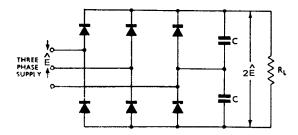

#### **Voltage Doublers**

Figure 26 shows the three-phase version of the conventional single-phase voltage doubler. It can be used for larger output powers than the single-phase circuit and has a regulation similar to that of the single-phase bridge doubler.

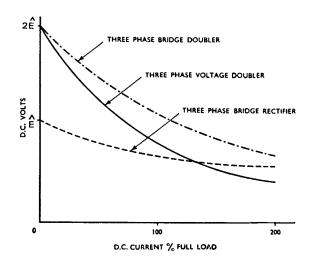

The three-phase bridge voltage doubler (Figure 27) has improved regulation characteristics and can be used to provide much larger currents. The output voltage, even on overload, never falls below that of the three-phase bridge rectifier as the comparative regulation curves of Figure 28 show. The percentage voltage ripple of these circuits is much smaller than that of the single-phase circuits.

FIGURE 28. Output Characteristics of Some Three-Phase Circuits

#### THREE-PHASE POWER SYSTEM

The introduction of silicon rectifiers gave rise to new ideas in designing high voltage, h.v., power equipments. H.v. silicon rectifier stacks offer the advantages of long life, small size, reliability and low operating costs when compared with thermionic valves. Furthermore, there is no need for the warming up period and heating transformer associated with thermionic valves. The silicon devices used in h.v. assemblies incorporate their own inherent reverse voltage limiting protection. They are of a non-destructive avalanche breakdown type, so that additional protection against excessive voltage transients is not required in the majority of cases. The stacks may be encapsulated in epoxy resin thus giving a rigid construction suitable for mounting either on insulation or metal plates or brackets. For larger powers the stacks can be connected in series or parallel.

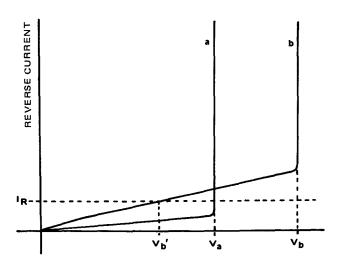

#### Series Operation of Avalanche Rectifiers

When connected in series controlled avalanche rectifiers require no shunting resistors to ensure an equal reverse voltage distribution across each element because of their ability to work satisfactorily in the avalanche region. Figure 29 shows two rectifiers connected in series. For a given reverse voltage supply equal to  $V_a + V_b$  the voltage swing across devices a and b will be as shown in Figure 29. Any increase in reverse voltage will cause an increase in the reverse current and  $V_b$  will increase until the avalanche voltage  $V_b$  is reached. Providing that the total voltage applied to both diodes in series is less than the sum of the two avalanche voltages, i.e.  $(V_a + V_b)$  the value of reverse current  $I_R$  will remain low well within the rating of the devices.

Conventional rectifiers need shunting resistors for steady stage voltage sharing and also capacitors for transient voltage sharing. As avalanche rectifiers have an inherent capability of absorbing reverse power, there is no need for shunting capacitors. In a normal design there will be sufficient reverse power capability existing in diodes connected in series to cope with any transients generated by switching 'on' and 'off' of most of their equipment transformers.

Manufacturers' data sheets provide information on the reverse power rating. The voltage transient energy can be evaluated from the magnetic energy stored in the transformer core. A simple comparison of these quantities will allow the suitability of the devices to be checked.

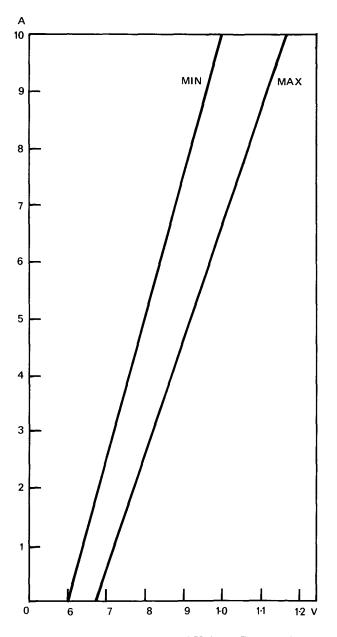

#### Parallel Operation of High Voltage Stacks

When running h.v. stacks in parallel two points must be considered: load sharing at the nominal load and load sharing during fault conditions. Typical forward voltage characteristics are shown in Figure 30. The slopes of the minimum and maximum curves are approximate only. (In fact, they curve slightly so that an increase of current does increase the forward voltage drop.) If two diodes are connected in parallel, one having a maximum and the other a minimum forward voltage drop, V<sub>F</sub>, Figure 30 shows that at 1.0V forward drop, one diode will take 10A and the other only 6.5A. This unbalance will increase at lower currents, i.e. at 0.8V across two diodes connected in parallel, one diode will take 5A, but the other only 2.5A. Paralleling up strings of diodes will lessen the unbalance; the greater the number of diodes in series, the less inequality.

Several tests were carried out on three strings of devices connected in series. Each string consisted of 20 avalanche diodes, type 1AS029. Table 2 gives a summary of the results. The current measured is the peak current of a 50Hz half sine wave. 'Percentage above mean' figures were obtained from the formula:

$$(B - M)100/M$$

%

where B is the highest current of a string, and M is the total current divided by 3, i.e. ideally shared current per string.

FIGURE 29. Waveforms Across Two Rectifiers in Series

FIGURE 30. Typical Forward Voltage Characteristics

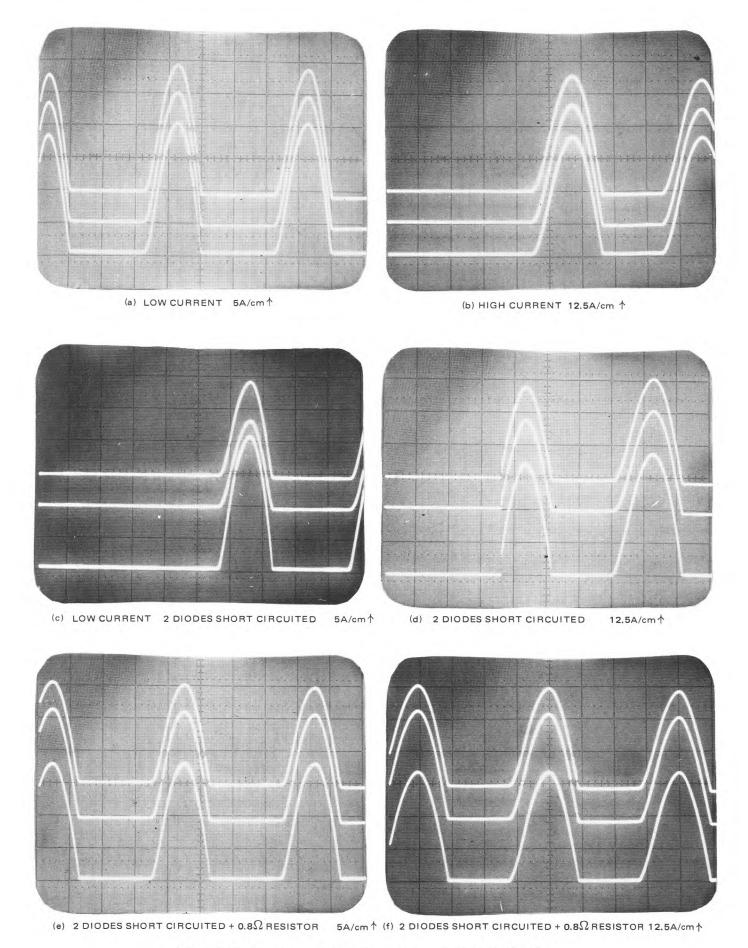

The experienced designer should allow for the possibility of diode failure. To assess the effects of this situation, Table 2 shows, therefore, load sharing between strings with one string having one or two diodes short circuited, i.e. 5% or 10% loss of diodes in one string. Some sort of external forced load sharing must be then introduced to prevent unbalance between strings becoming unacceptable, i.e. exceeding the device rating. An  $0.8\Omega$  series resistor, connected with each string gives a satisfactory result for this particular example. As guidance, a series resistor, Rs. which will dissipate 10% of the diode losses, should be used with each string of diodes. For example, a 1AS029 diode is rated at 1.5A average with a typical forward voltage drop 0.87V. Total power dissipation in a 20 diode string will be  $20 \times 0.87 \times 1.5 = 26W$ . The series resistor then will be  $R_S = 2.6/1.5^2 = 1.15\Omega$ ; Resistor  $R_S$  compensates for the unbalance caused by the loss of 10% of diodes in one string. For less than 10 diodes in series, the value of the series resistor should be increased. To illustrate an unbalance between various strings some current traces were recorded and are shown in Figure 31. The effect of an  $0.8\Omega$  series resistor is quite noticeable.

Table 2

| Total    | 'a' 'b' | ,,,  | 'h'  | ʻc'        | Percentage            | Remarks |

|----------|---------|------|------|------------|-----------------------|---------|

| Total    |         | ا ت  | ٠    | above mean | i iciiiai ka          |         |

| <b></b>  | +       |      |      |            |                       |         |

|          | 5       | 4.5  | 5    | 2.1        |                       |         |

| 36.5 12  | 2.5     | 11.5 | 12.5 | 2.9        |                       |         |

| 69.5 23  | 3.5     | 22.5 | 23.5 | 1.7        |                       |         |

| 83.9 28  | 8.7     | 27.6 | 27.6 | 3.1        |                       |         |

| 124.2 4  | 1.4     | 41.4 | 41.4 | 0          |                       |         |

| 142.5 4  | 7.5     | 47.5 | 47.5 | 0          |                       |         |

| 162 54   | 4       | 54   | 54   | 0          |                       |         |

| 21 8     | 8.5     | 6.0  | 6.5  | 21.5       | One diode is          |         |

| 59.5 2   | 2.5     | 18.0 | 19.0 | 12.5       | short circuited       |         |

| 89.7 3   | 2.5     | 28.6 | 28.6 | 8.3        | in string 'a'         |         |

| 123.7 43 | 3.7     | 40   | 40   | 6.1        |                       |         |

| 135.0 50 | 0       | 47.5 | 47.5 | 3.6        |                       |         |

| 18.5     | 6.5     | 6.0  | 6.0  | 4.8        | One diode is          |         |

| 39 1     | 3.5     | 12.5 | 13.0 | 3.8        | short circuited       |         |

| 63.5 2   | 21.5    | 21.0 | 21.0 | 2,4        | in string 'a' and     |         |

| 86 30    | 80      | 28.5 | 27.5 | 4.3        | $0.8\Omega$ resistors |         |

| 107 3    | 86      | 36   | 35   | 1.4        | are added to          |         |

| 145 4    | 8.8     | 48.7 | 47.5 | 1.1        | each string           |         |

| 22 10    | 0.5     | 5.5  | 6.0  | 44         | Two diodes are        |         |

| 55 2     | 2.5     | 16.0 | 16.5 | 20.3       | short circuited       |         |

| 77 3     | 31.0    | 22.5 | 23.5 | 20.0       | in string 'a'         |         |

| 107 4    | 1.0     | 32.5 | 33.5 | 15.4,      |                       |         |

| 141 5    | 2.4     | 43.6 | 45   | 11.6       |                       |         |

| 16       | 6.5     | 4.5  | 5    | 21.4       | Two diodes are        |         |

| 39.5     | 4.0     | 12.5 | 13.0 | 6.6        | short circuited       |         |

| 62 2     | 21.5    | 20.5 | 20   | 4.1        | in string 'a' and     |         |

| 74.5 2   | 26.0    | 25.0 | 23.5 | 5.3        | 0.8Ω resistors        |         |

| 119.5 4  | 11.0    | 40.0 | 38.5 | 3.1        | are added to          |         |

| 147.5 5  | 50      | 50   | 47.5 | 1.8        | each string           |         |

#### Three Phase Bridge Design

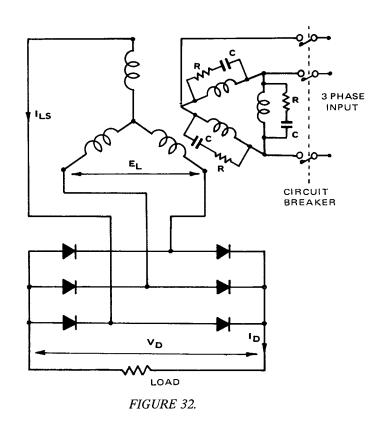

Theory: 5 One of the most common connections for h.v. power conversion is a three phase bridge (see Figure 32) where the transformer and silicon rectifiers capabilities are fully utilised. The following design information is based on what is known as the. Infinite Reactance Theory'. It assumes that each pulse of current is rectangular in form as though a reactance of infinite value is in the d.c. output circuit. It shows good correlation with practical results in polyphase rectifier circuits, but is less accurate in single phase circuits because of an increasing departure from the assumed idealised waveform.

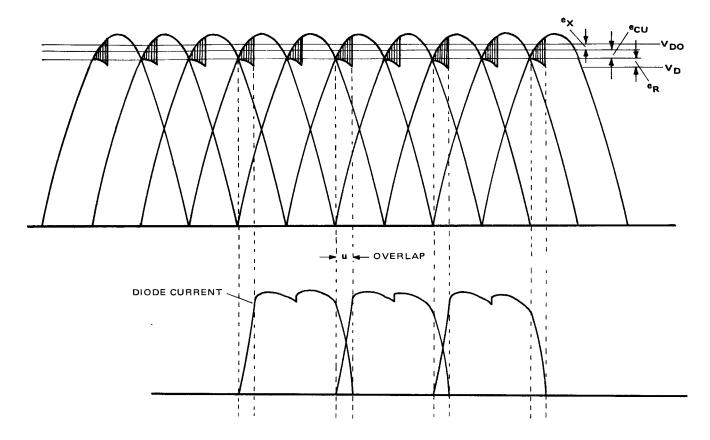

High power circuits, employing semiconductors, invariably use a certain amount of reactance to provide fault current limitation. In most cases the reactance values vary between 5% and 10%. The voltage drop, caused by the reactance, cannot be ignored and must be taken into account for accurate circuit design. As the current waveforms in rectifier circuits are not therefore sinusoidal it would be rather difficult to establish the correct voltage loss due to the presence of reactance. Infinite Reactance Theory' offers a solution to this problem. An overlap angle present in rectifier circuits and proportional to the a.c. reactance causes a reduction in d.c. voltage output which can be calculated, see Figure 33. The voltage drop occurs only during the period of overlap and it is this feature which is the main difference between this method and the orthodox design calculations. In the latter the a.c. reactance is neglected as it is considered to be too small to make any appreciable difference, or calculated as an a.c. input drop.

FIGURE 31. Waveforms of Fault Current Through 20 Diode H.V. Stacks

FIGURE 33. Current and Voltage Waveforms

The following equation must be satisfied:

$$V_{DO} = V_D + e_X + e_R + e_{CU}$$

(1)

where

$V_{DO}$  = Theoretical no load d.c. voltage

V<sub>D</sub> = Full load d.c. voltage

eX = D.c. reactive voltage drop (during commutation) due to the presence of transformer leakage reactance and supply reactance.

e<sub>R</sub> = D.c. voltage drop (total) in the rectifiers.

eCU = D.c. voltage drop due to the presence of resistance in the circuit, including copper loss

Now

$$e_X = (X_T + X_S). V_{DO}/200 . . . . . . (2)$$

where  $X_T$  = percentage transformer reactance referred to the primary kVA

$$e_{CU}$$

= total circuit power loss due to

resistance/ $I_D$  . . . . . . . . . . . . . . . . (3)

where  $I_D$  = D.c. current in amps at full load.

From equation (1) and (2)  $V_{DO}$  can be determined.

$$V_{DO} = (V_D + e_R + e_{CU})/[1 - (X_T + X_S)/200]$$

(4)

$$E_{LO} = V_{DO}/1.35$$

. . . . . . . . . (5)

where  $E_{LO}$  = Secondary r.m.s. voltage between lines at no load.

where  $I_{LS}$  = rectifier transformer secondary r.m.s. line current

Primary transformer rating = secondary transformer rating =

$$1.05 \times I_D \times V_{DO}/1000 \text{ kVA}$$

. . . . . . . . . . . . (7)

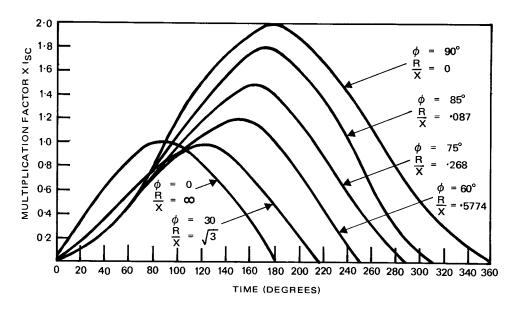

The Fault Current: This has been assumed to be limited only by the leakage reactance of the transformer and supply. When switching on to a fault condition, it can be observed that the first pulse of the current is larger than that of the steady state short circuit. This is due to the asymmetry (asymmetrical pulse) caused by the presence of a reactance. The amplitude of the asymmetrical pulse depends on the ratio R/X of the system and can be established from Figure 34. It can also be seen from Figure 34 that the maximum asymmetrical pulse can be double the peak value of steady state short circuit current for an a.c. infinite reactance system. For practical purposes, account must be taken of an asymmetrical pulse when dealing with

FIGURE 34. First Pulse Current Waveform

up to, for instance, only 3 or 4 pulses. In longer periods the steady state pulses will swamp the effect of the asymmetrical pulse.

$$I_{SC} = I_D \times 200/3\frac{1}{2}(X_T + X_S)$$

. (8)

where ISC is short circuit peak current

Efficiency: The accepted way of calculating efficiency in larger equipments is by a summation of losses.

Efficiency =

$$\eta$$

=  $[1 - losses/(power output + losses)] 100% (9)$

In calculating the efficiency the losses of the transformer, rectifier and auxiliaries should be included. The losses in the rectifier diodes will depend upon the overall load current and will be equal to:

$$P_R = I_D \times 2 \times V_F \times n$$

. . . . . . . (10)

where

P<sub>R</sub> = total rectifier losses in the three phase bridge

$V_F$  = forward voltage drop across one diode at current,  $I_D$

n = number of diodes connected in series

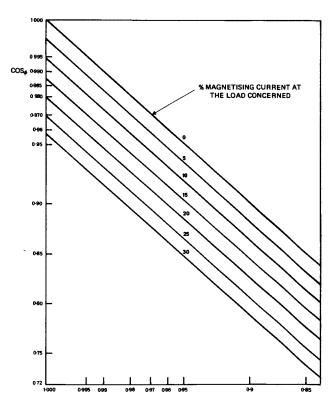

**Power Factor:** For practical purposes the only important value of the power factor of the current drawn from the supply is the power factor of the fundamental or  $\cos \phi$ , where  $\phi$  is the angle by which the fundamental component of current lags the supply voltage. It is this value that will be measured by instruments. The total power factor is the product of the displacement factor (due to the fundamental) and of the distortion factor (due to the harmonics), the latter being of theoretical interest only.

The evaluation of the power factor depends upon the following relationship:

$$\cos u = 1 - 2e_X/V_{DO}$$

. . . . . . . . (11)

$$\tan \phi_1 = (u - \sin u \cdot \cos u)/\sin^2 u$$

. . . (12)

where u is the angle of overlap (see Figure 33). From the value of  $\tan \phi_1$ ,  $\cos \phi_1$  can be obtained and by applying this to the curves of Figure 35 for varying amounts of percentage magnetising current, the power factor of the

FIGURE 35. Effect of Magnetising Current on Cos  $\phi$

fundamental  $\cos \phi$  can be established. The magnetising current taken represents a percentage of the full load primary current. If, therefore, the power factor is to be calculated for any other load current, it must be remembered that the magnetising current percentage must now be based on the new primary current. For example, if the full load magnetising current is taken as 5%, the magnetising current percentage at half the primary current would become 10%. In the case of  $e_X$ , the d.c. reactive volt drop, this will be directly proportional to  $I_D$ , the output current.

Protection: To ensure the satisfactory operation of equipment using semiconductor devices the problem of protection against possible excessive voltage transients and excessive currents must be solved. Earlier, the capabilities of avalanche diodes to absorb large powers in the reverse direction was discussed. Therefore, for normal applications of h.v. stacks, there is no need for further steps to be taken. However, in some cases, when frequent switching is taking place, e.g. induction or dielectric heating, a simple CR network, connected across the primary windings of the transformer will help to suppress excessive voltage transients. Recommended values for voltage transients suppression are shown below and connections are given in Figure 32.

$$C = 350 I_M/E_P$$

$\mu F$  . . . . . . . . . (13)

$R = 100/C$   $\Omega$  . . . . . . . . . (14)

assuming a 50Hz supply where  $I_M$  is the magnetizing current in amps. and  $E_P$  is the primary supply line voltage.

Surge currents are easier to evaluate than voltage transients and they can be controlled by a circuit design as described in the fault current paragraph. By choosing the correct value of transformer leakage reactance, the peak fault current can be kept below a safe value for the devices. Circuit breakers, contactors and fuses are normally used to protect semiconductor equipments against overloads and short circuits. Contactors, not having fault breaking capabilities, are normally backed up by fuses. Circuit breakers, however, do not require fuses. In order to withstand an inrush current to a transformer, the fuses in the input side of the transformer are usually rated at twice or three times the nominal current. Therefore, protection against the d.c. faults becomes more difficult. On the other hand, the fuses on the secondary side of the transformer may be rated very near to the full load current. This is not always convenient, especially for h.v. equipments, as the fuses become rather expensive. When fuses or breakers are adapted for the protection of silicon devices, correct discrimination can be achieved by keeping below the rectifier overload curve at every point by either fuse or breaker characteristics. A knowledge of i2.t (let through energy) values is very useful in cases when a fault current is expected to be interrupted within ten milliseconds. In this time interval, the i2t can be assumed to be approximately constant. A simple comparison of the rectifiers i2t with total fuse i2t will give the rating of the fuse needed.

#### **Practical Example**

Rectifier Transformer Requirements: Rectifier power equipments to deliver 10A at 12kV, i.e. 120kW for an induction heating load.

$$I_D = 10A$$

$$V_D = 12kV$$

Let us assume  $X_T = 7\%$  and  $X_S = 1\%$ .

From equation (8)  $I_{SC} = 10 \times 200/3^{1/2} \times 8 = 145 \text{A}$

Assuming the copper loss = 2%, i.e.  $2 \times 120/100 = 2.4$ kW

The ratio of the percentage of equivalent resistance due to the copper losses to the total percentage reactance (i.e. 2/8 = 0.25) gives the multification factor for obtaining peak asymmetrical current from Figure 34 which here is 1.5. Therefore, the peak asymmetrical current is  $145 \times 1.5 = 218A$ .

Connecting 3 x 1·5A H.V. stacks in parallel will give, including a 10% unbalance,  $218 \times 1 \cdot 1/3 = 80$ A per stack, which is well within the surge rating of a 1AS029 avalanche rectifier.

It is now necessary to find the theoretical no load d.c. voltage,  $V_{DO}$ . Considering a stack consisting of 20 avalanche diodes connected in series with, say, 1.0V drop per diode,

$$e_R = 2 \times 20 \times 1 = 40V$$

$$e_{CU} = 2400/10$$

from equation (3)

= 240V

$$V_{DO} = (12,000 + 40 + 240)/[1 - (7+1)/200]$$

from equation (4)

$$= 12800V$$

Check:

$$e_X = (7 + 1) \times 12800/200$$

from equation (2)

= 512V

$$\therefore$$

V<sub>DO</sub> = 12000 + 512 + 40 + 240 from equation (1)

= 12792, i.e. 12800

Note that the d.c. reactive voltage drop  $e_X = 512V$  which cannot be ignored when designing rectifier equipments.

Now other transformer details can be found.

$$E_{LO} = 12,800/1.35 = 9,500V$$

From equation (5)

$$I_{LS} = 10 \times 2^{1/2}/3^{1/2} = 8.2A$$

From equation (6)

Rating of the transformer =

$$1.05 \times 10 \times 12,800/1000$$

=  $134.4$ kVA From equation (7)

Rating of the transformer is also =  $3\frac{1}{2} \times E_{LO} \times I_{LS}/1000 \text{kVA}$ =  $3\frac{1}{2} \times 9,5000 \times 8.2/1000$ = 1.35kVA

= 135kVA The specification for the transformer can now be written

delta/star

Primary supply 440V, 3 phase, 50Hz

Secondary open circuit

Connections:

Line voltage 9500V

Secondary full load current 8.2A rms

Leakage reactance 7%

Assumed copper losses 2.4kW

Ambient temperature 30°C

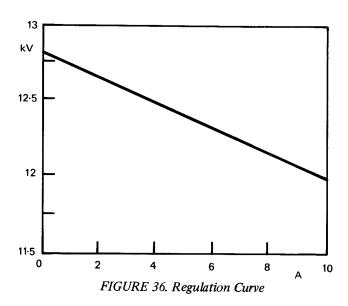

Figure 36 shows the d.c. voltage regulation of the equipment.

H.V. Stacks: There are two points for consideration in selecting rectifiers, i.e. the voltage and current ratings. The maximum peak voltage expected from the transformer is  $9500 \times 2^{\frac{1}{2}} \times 1.1 = 14800V$ , assuming a 10% rise in supply voltage. Allowing 35% above this figure for safety, stacks capable of withstanding 20kV will be needed. Twenty avalanche rectifiers, type 1AS029, rated at 1000V each and connected in series are well suited for this application. The current rating of 1AS029 devices has been partly discussed. First, the asymmetrical peak current expected during a fault is 80A and the nominal current per stack is  $10 \times 1 \cdot 1/3 \times 3 = 1 \cdot 22A$  mean both inside the rating of 1AS029 devices. Normally, equipments of this power would have a circuit breaker in the input to the transformer to cope with any overloads or fault currents. The speed of operation of an a.c. circuit breaker is about 60ms, i.e. 3 cycles in a 50Hz system. Taking into account the safety factor, the stacks should be capable of withstanding the fault current for at least 5 cycles, i.e. 100ms. In the example the value of the steady state fault current is  $145 \times 1 \cdot 1/3 = 54A$ . allowing 10% for unbalance. This value is again within the rating of the devices. As discussed, a loss of devices will necessitate an additional series resistor connected to each stack. The value of this resistor can be evaluated from:

$$R_S = 20 \times 0.875/10 \times 1.5 = 1.17\Omega \text{ say } 1.2\Omega$$

#### Summing up:

Three h.v. stacks will be connected in each arm of a three phase bridge giving a total of 18 stacks.

A  $1.2\Omega$  series resistor is added to each stack.

Each stack will consist of 10 1AS029 avalanche rectifiers.

Efficiency: From equation 10 -

$P_R = 10 \times 2 \times 1.0 \times 20 = 0.4kW$

As the copper losses are = 2.4kW

The total losses = 2.8kW

: From equation (9)  $\eta = [1 - 2.8/122.8]100\%$

= 97.7% at full load

Total losses at half load = (0.4/2) + (2.4/4) = 0.8kW

Approximately d.c. voltage at half load = 12000 + 800/2 = 12400V

See Figure 36.

The output power at half load =  $12400 \times 5/1000 = 62 \text{kW}$

:. Efficiency = [1 - 0.8/62.8] 100% = 98.7% at half load.

Power Factor: From equation 11 -

cos u = 1 − 2 x 512/12800 = 0.916

∴ u = 23° 36 = 0.413 rad

From equation (12)

tan

$$\phi_1$$

= (0.413 − 0.4 x

0.916)/0.16 = 0.3

∴  $\phi_1$  = 17°

cos  $\phi_1$  = cos 17° = 0.956

Assuming the magnetising current = 2.5%, from Figure 35,  $\cos \phi$ , the displacement factor, is 0.95 at full load.

#### At half load:

$$\cos u = 1 - 2 \times 256/12800 = 0.959$$

$u = 16^{\circ}24' = 0.286 \text{ rad}$

$$\tan \phi_1 = (0.286 - 0.282 \times 0.050)/0.282 = 0.2$$

$$\phi_1 = 11^{\circ}24', \cos \phi_1 = 0.98$$

and from Figure 35 cos  $\phi$  = 0,97 (the magnetising current for half load is 5%)

**Protection:** As the equipment is supplying an inductive heating load an R.C. network connected in the primary winding of the transformer has been added.

The primary current

$$I_P$$

= 134·4 x 1000/3½ x 440 = 176A

$I_M$  = 2·5 x 176/100 = 4·4A

C = 350 x 4·4/440 = 3·5 $\mu$ F From equation (13)

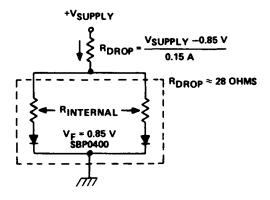

and the series resistor

R =

$$100/3.5 \approx 28.5\Omega$$

From equation (14)

As discussed, the stacks selected for the equipment are within their capabilities for the first symmetrical pulse, as well as for the steady state short circuit current for the time of 100ms. The circuit breaker selected must be able to open at up to 60ms to give a sufficient safety margin for satisfactory generation.

#### REFERENCES

- Blundell, A. J., Kinman, T. H., Hibberd, R. G. and Williams, J., 'Silicon Power Rectifiers' *Proc. I.E.E.* Part A, Vol 108, No. 40, 1961.

- 2. Weidelich, D. L.: 'Voltage Multiplying Circuits', Electronics, 1941, Vol. 14, No. 5.

- Weidelich, D. L.: 'Analysis of Full-Wave Rectifier and Capacitive-Input Circuits', *Electronics*, 1947, Vol. 20, No. 9.

- Schade, O. H.: 'Analysis of Rectifier Operation', Proc. I.R.E., 1943, Vol. 31, No. 7.

- Read, J. C.: 'The Calculations of Rectifier and Inverter Performance Characteristics', I.E.E. Proceedings, 1945.

- Budek, J. A. and Marchant, A. H.: 'Protective Methods for Silicon Rectifier Equipment', *Direct Current*, Nov. 1964.

#### II USE OF HIGH-VOLTAGE SWITCHING TRANSISTORS

#### by Ken Salmon and Mick Maytum

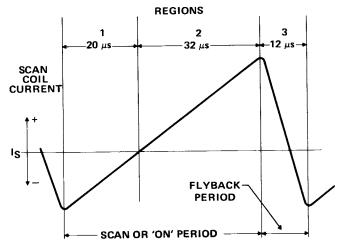

The use of high-voltage power transistors in switching applications is practical and well established, the most common usage being in the horizontal sweep circuit of television receivers and inverters. The transistors are designed to withstand the large transient dissipation inherent in high-current, high-voltage switching circuits and will give effective and reliable operation in properly designed circuits.

The transistor structure differs in several ways from that of low-voltage power transistors and the resultant changes in the switching characteristics require new circuit techniques to ensure reliable operation. In order to understand the effects that this structure has on the transistor switching performance and circuit arrangement, the basic construction of high-voltage transistor is first explained and then an indication given of how their parameters and drive requirements are affected.

The horizontal line output circuit of a television receiver is used as an example of a switching circuit to show the method of using the transistor as, although the control of switching is important in all applications, the requirements of the line output circuit present one of the most difficult applications. The transistor switches scan coil current and generates the e.h.t. supply at a repetition frequency of approximately 15 kHz with a transistor case temperature which may rise to 80°C. This and the other applications of the device require careful control of the switching waveforms and information is given to enable the circuit designer to achieve this control in any switching circuit.

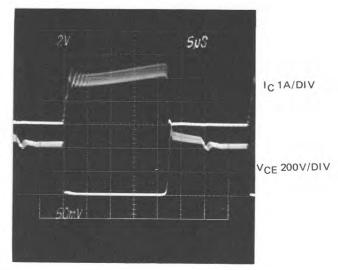

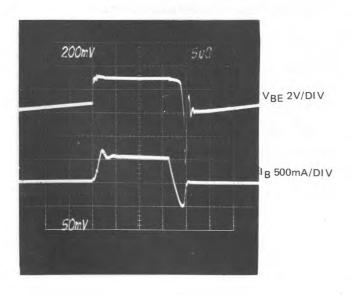

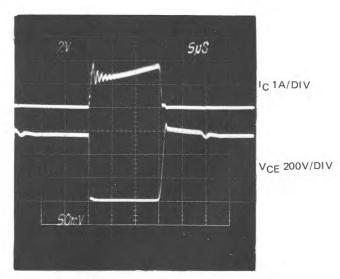

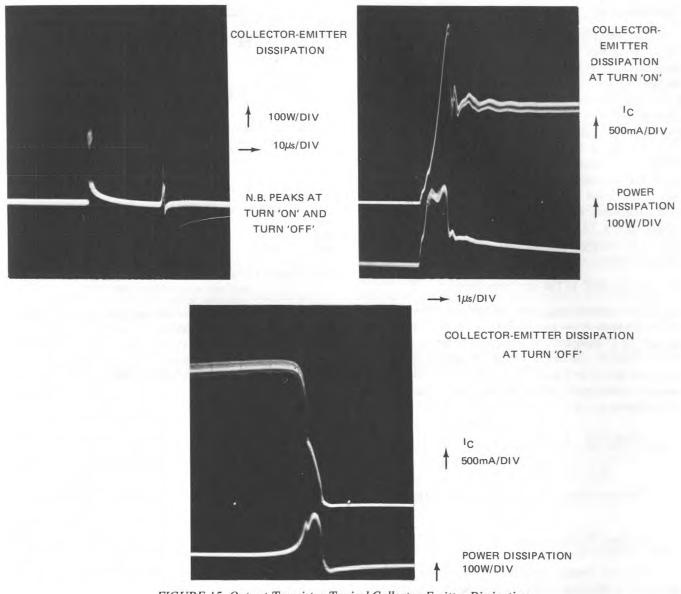

The circuit requirements, the transistor ratings, and the methods of use and measurement are described to enable the circuit designer to select the appropriate device and components for his application. Photographs of actual switching waveforms are included to clarify the difference between good and bad circuits.

#### CONSTRUCTION

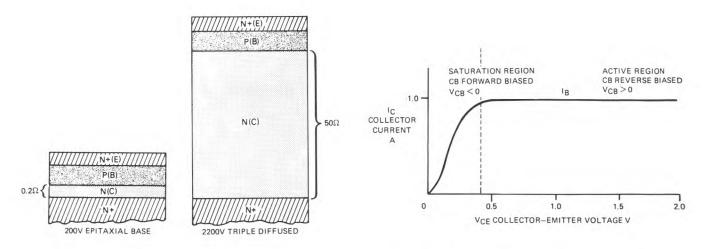

An understanding of the structure limitation of high voltage transistors substantially enhances the performance which can be derived by the designer. Figure 1 shows the relative region widths for two power transistors. The low voltage epitaxial base transistor is typified by a shallow collector n region whose bulk resistance is negligible. As voltage requirements increase, the voltage sustaining collector increases dramatically both in depth and resistivity, so that for the 2200V transistor illustrated in Figure 1, there is an increase in collector depth of 15 times that of the 200V device and a bulk resistance of  $50\Omega$ .

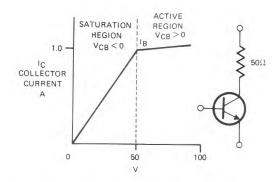

The common emitter characteristics for a 200V transistor are shown in Figure 2, which demonstrates that any resistive components are negligible compared with the junction voltage, both in the saturation region where the collector base is forward-biased and in the active region where that junction is reverse-biased.

The effect of the  $50\Omega$  bulk collector resistance might be expected to produce the characteristic shown in Figure 3.

FIGURE 1. Typical Transistor Cross Sections

FIGURE 2. Common Emitter Characteristic of 200V Transistor

FIGURE 3. Composite Characteristic with External  $50\Omega$  Resistor

FIGURE 4. Common Emitter Characteristic for 2200V, 2A Transistor

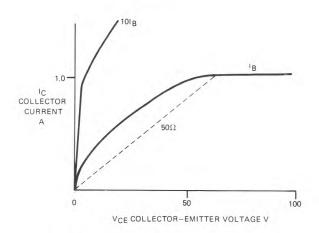

The practical characteristics in Figure 4 show that indeed the line of  $50\Omega$  plus  $V_{BE}$  would provide a locus of points for VCB = 0, however, in the saturation region, i.e., VCB < 0, much lower voltages are obtained. The accepted explanation is that in saturation, the forward bias on the collector base junction produces a condition of 'high level injection' into the high resistivity collector which, within the constraints of space charge neutrality, result in a severe conductivity modulation of the region. Varying levels of saturation produce varying degrees of conductivity modulation so that when the device is just out of saturation the full effect of the high bulk resistance is apparent. For the 2200V transistor illustrated, this point would be when VCE = 50V (approx.) with a collector current of 1A. Thus, when the transistor is driven very hard into saturation, the collector resistance can be reduced to a negligible level which is obviously the requirement when the device is used as a switch. The resulting large quantities of stored charge accumulated in the collector region restrict device switching performance, and although this may be controlled by the base drive, the principles applied must comprehend that the collector region predominates in high voltage transistors.

#### **EFFECT ON PARAMETERS**

In a number of applications it is 'turn off' which is of prime interest since the collector current is at a maximum

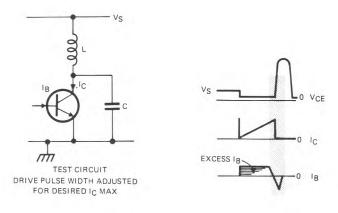

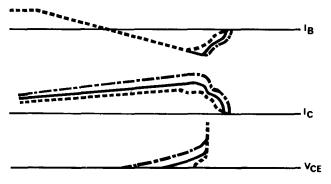

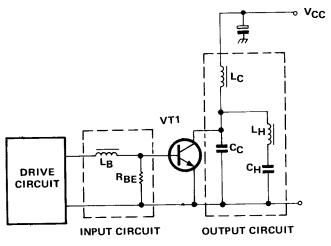

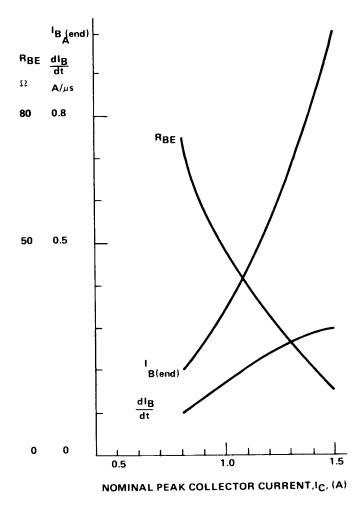

FIGURE 5. Switching

Circuits

FIGURE 6. General Waveforms