# Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This pdf document was generated by me Colin Hinson from a Crown copyright document held at R.A.F. Henlow Signals Museum. It is presented here (for free) under the Open Government Licence (O.G.L.) and this pdf version of the document is my copyright (along with the Crown Copyright) in much the same way as a photograph would be.

The document should have been downloaded from my website <u>https://blunham.com/Radar</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Radar</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you personally – I know that I would have liked to have found some of these files years ago – they would have saved me a lot of time !

Colin Hinson In the village of Blunham, Bedfordshire.

AP 116E-0755-6A2

July 1980

# UK/FRR-627 REMOTELY-CONTROLLED HF RECEIVER (Racal Type RA. 1784)

BY COMMAND OF THE DEFENCE COUNCIL

Ministry of Defence

Sponsored for use in the

ROYAL AIR FORCE by D. Sigs (Air)

Prepared by Racal Communications Systems Ltd., Bracknell, Berks.

Publications authority : ATP/MOD (PE)

Service users should send their comments through the channel prescribed for the purpose in : AP 100B-01 Order 0504

# LETHAL WARNING

### TAKE CARE!

VOLTAGES IN EXCESS OF 30 V (RMS) OR 50 V dc CAN BE LETHAL

#### MODIFICATION RECORD

A list of the modifications embodied in this publication is given in Topic-6A1, pages (vii) and (viii).

Page (vii)/(viii)

# Maintenance manual (Parts 3 to 7)

# **RA**. 1784 Serial Controlled HF Receiver

Racal Communications Limited Western Road, Bracknell, RG121RG England Tel: Bracknell (0344) 3244 Telex: 848166 Grams: Racal Bracknell. The Electronics Group Prepared by Central Handbooks Department, Racal Group Services Limited. Printed in England Ref. WOH 6247

### **LETHAL WARNING**

Voltages within this equipment are sufficiently high to endanger life.

Covers are NOT to be removed except by persons qualified and authorised to do so and these persons should always take extreme care once the covers have been removed.

Resuscitation instructions are given overleaf.

# FIRST AID

# in case of Electric Shock

1.

- Lay victim on his back.

- 2. Clear victim's mouth and throat.

- 3. Tilt victim's head back as far a possible and raise his head.

Have someone else send for a Doctor Keep patient warm and loosen his clothing

- 4. Pinch victim's nostrils.

- 5. Take a deep breath.

- Cover the victim's mouth with your and blow, watching his chest rise Note: Blow forcefully into adults, bu gently into children.

- 7. Move your face away to allow victin to breathe out, watching his chest fall

- Repeat first five to ten breaths at rapid rate; thereafter, take one breat every three to five seconds.

- 9. Keep victim's head back as far a possible all the time.

DO NOT Give liquids until patient is conscious PART 3

CHAPTER 2

RF UNIT

#### CONTENTS

|                                       | Para. |

|---------------------------------------|-------|

| INTRODUCTION                          | 1     |

| RE-RADIATION FILTER<br>RF BOARD PS514 | 2     |

| Wideband Protection Stage             | 3     |

| In-band Protection Stage              | 6     |

| Attenuator Control Circuit            | 8     |

| Diode Protection Circuit              | 12    |

| RF Amplifier                          | 13    |

| HALF-OCTAVE FILTER BOARD PS549        | 14    |

#### ILLUSTRATIONS

|                                                 | Fig.No. |

|-------------------------------------------------|---------|

| Circuit and Layout: Re-radiation Filter         | 2.1     |

| Circuit Diagram: RF Board PS514                 | 2.2     |

| Layout: RF Board PS514                          | 2.3     |

| Circuit Diagram: Half-Octave Filter Board PS549 | 2.4     |

| Layout: Half-Octave Filter Board PS549          | 2.5     |

| 1                                               |         |

# <u>CHAPIER\_1</u>

### FUNCTIONAL DESCRIPTION

### CONTENTS

|                    | Para. |

|--------------------|-------|

| INTRODUCTION       | 1     |

| RF BOARD           | 2     |

| FIRST MIXER BOARD  | 8     |

| SECOND MIXER BOARD | 10    |

| IF FILTER BOARD    | 12    |

| IF BOARD           | 14    |

| AF BOARD           | 17    |

### ILLUSTRATIONS

Fig. No.

1.1

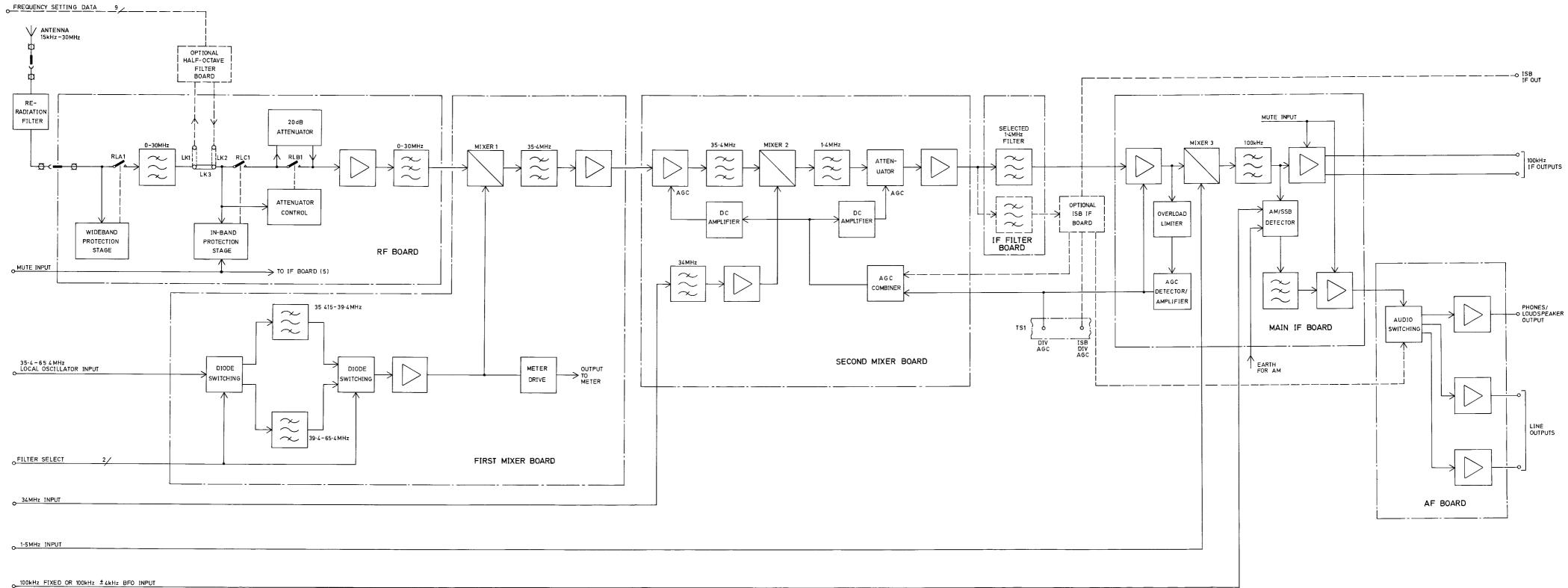

Block Diagram: RA.1784 RF, IF & AF Section

Part 3 Chap.1 Contents

### <u>CHAPIER 1</u>

### FUNCTIONAL DESCRIPTION

### INTRODUCTION

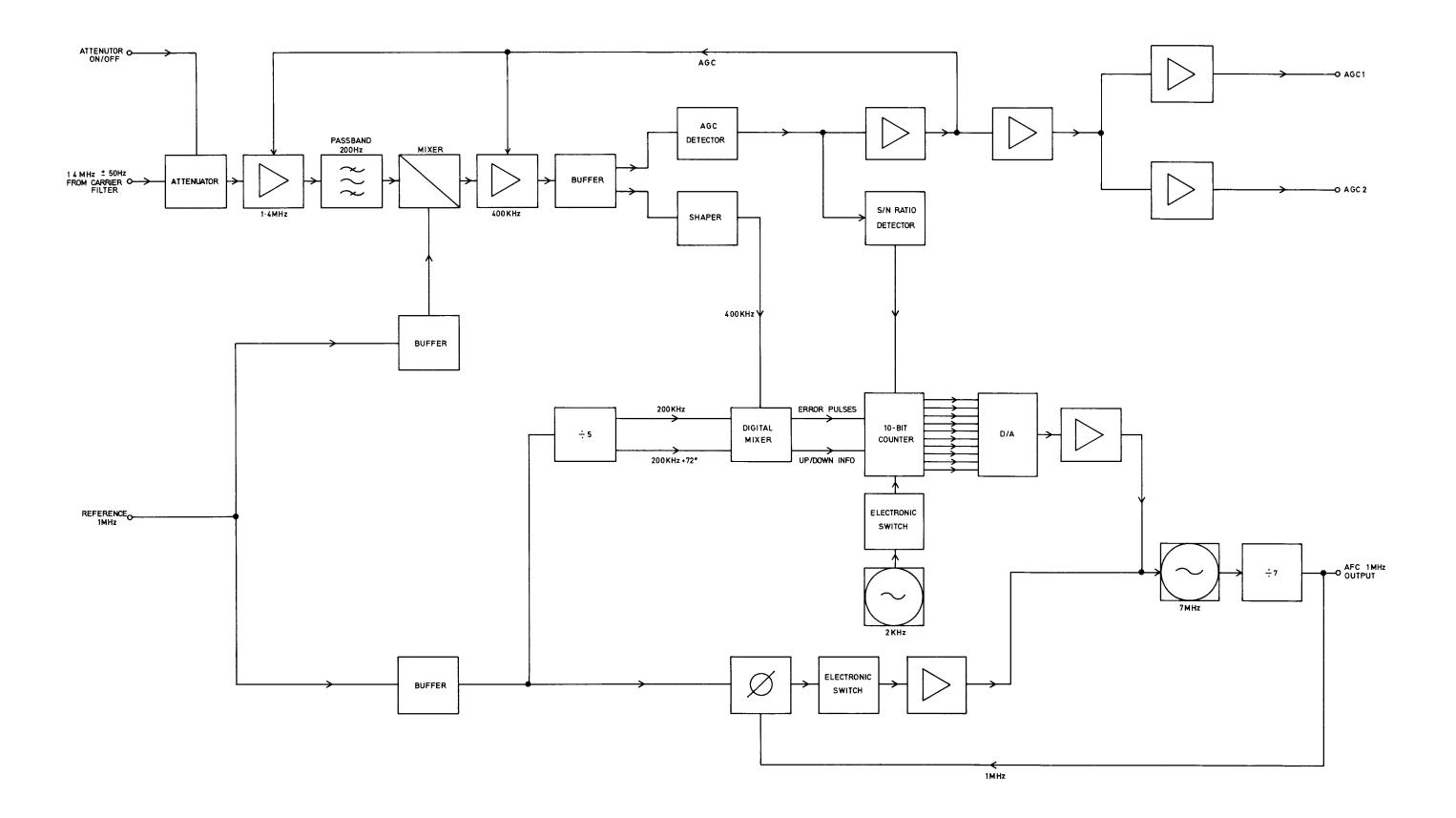

This chapter briefly describes the operation of the RF, IF and AF section of the receiver, and should be read in conjunction with the block diagram given in fig. 1.1. This diagram includes the optional half-octave filter board and the optional ISB IF board, which is the same as the main IF board.

### RF BOARD

- 2. The received signal at the antenna, in the frequency range 15 kHz to 30 MHz, is applied to the RF board via the re-radiation filter. This unit also contains a 500 mA antenna surge protection fuse and a spark gap.

- 3. The output signal from the re-radiation filter is applied to a wideband protection stage which controls a normally-energized relay, RLA/1, such that when the r.m.s. level of the received signal at the antenna exceeds approximately 10V emf, the relay contact is opened and the RF path is broken.

From relay contact RLA1, the received signal is applied to a 0 to 30 MHz bandpass filter and thence via LK3, or the optional half-octave filter board and links LK1, LK2, to an in-band protection stage. The half-octave filter board contains eleven bandpass filters, one of which is automatically selected by the applied frequency setting data; each filter provides an additional 20 dB attenuation half an octave removed from the appropriate band edge.

5. The in-band protection stage opens relay contact RLC1 when signal levels in the passband of the selected half-octave filter exceed r.m.s. levels of 3V emf at the antenna socket. The relay contact is also opened when a 0V signal is applied to the MUTE terminal on the receiver rear panel (either directly or via the serial data and the interface unit).

6. The received signal at LK3 (or LK2) is also applied to an attenuator control circuit which controls relay RLB. When the r.m.s. level of the received signal at the antenna exceeds approximately 300 mV emf relay contact RLB1 opens and the received signal is applied via a 20 dB attenuator to the RF amplifier. The relay contact closes when the received signal level subsequently falls to approximately 100 mV emf. The attenuator control circuit may be inhibited if not required by the setting of a link on the RF board.

7. The RF amplifier has a wideband characteristic and provides a gain, from board input to board output, of approximately three times. The amplified output signal is applied via a 0 to 30 MHz low pass filter to the first mixer board.

### FIRST MIXER BOARD

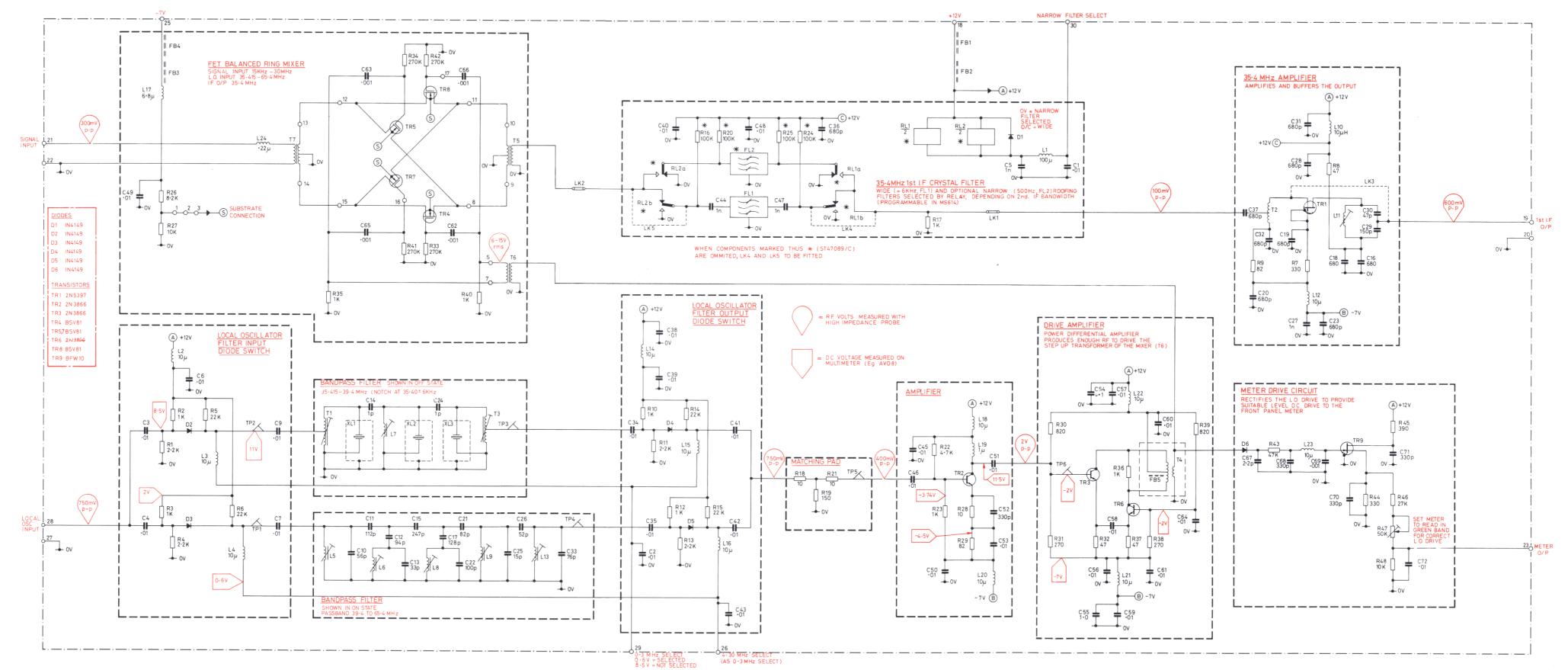

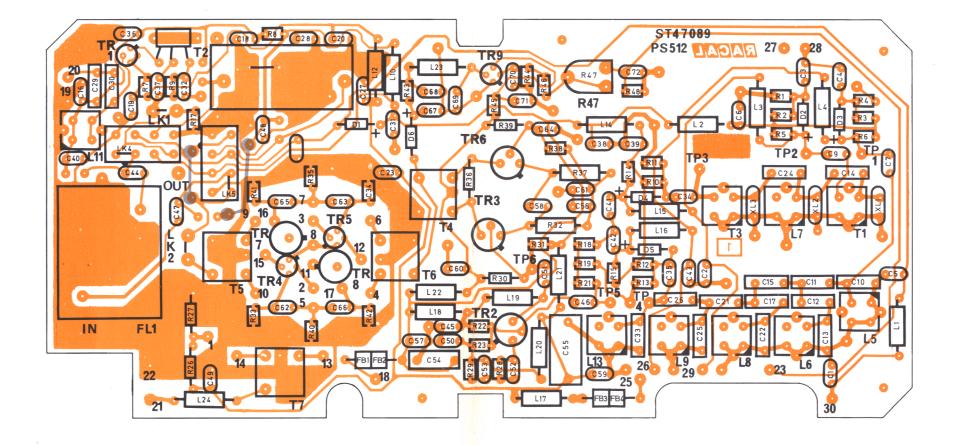

8. Mixer 1 combines the output signal from the RF board with the 35.415 to 65.4 MHz local oscillator signal from the synthesizer to produce the first intermediate frequency output at 35.4 MHz. The local oscillator signal is applied to the mixer stage via a drive amplifier and one of two bandpass filters; for receiver operating frequencies up to 3.99999 MHz the diode switching circuits route the signal via a 35.415 to 39.4 MHz bandpass filter, whilst for frequencies of 4 MHz and above the signal is routed via a 39.4 to 65.4 MHz bandpass filter. The output signal from the drive amplifier is also applied to a meter drive circuit, the output from which is applied to the receiver front panel meter via the interface unit (Part 4).

9. The output signal from the mixer is applied to a 35.4 MHz bandpass crystal filter and thence via a tuned 35.4 MHz buffer amplifier to the second mixer board.

### SECOND MIXER BOARD

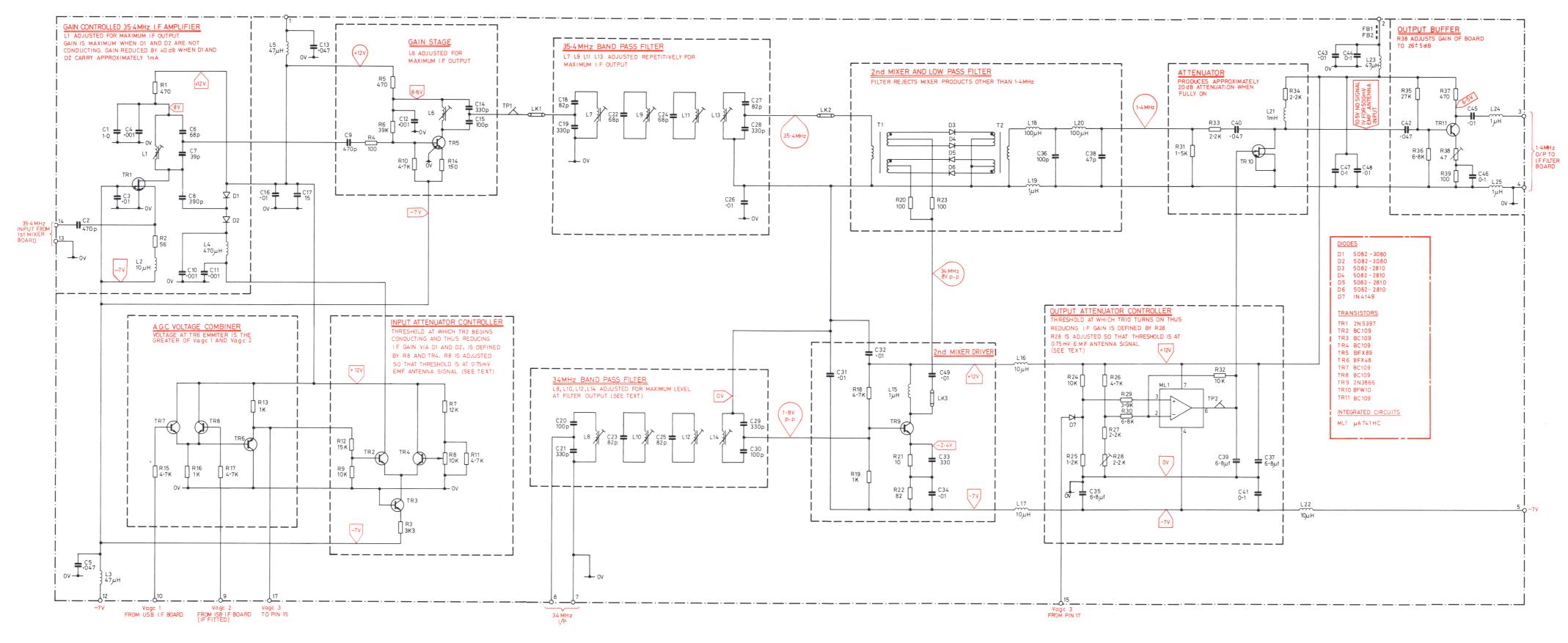

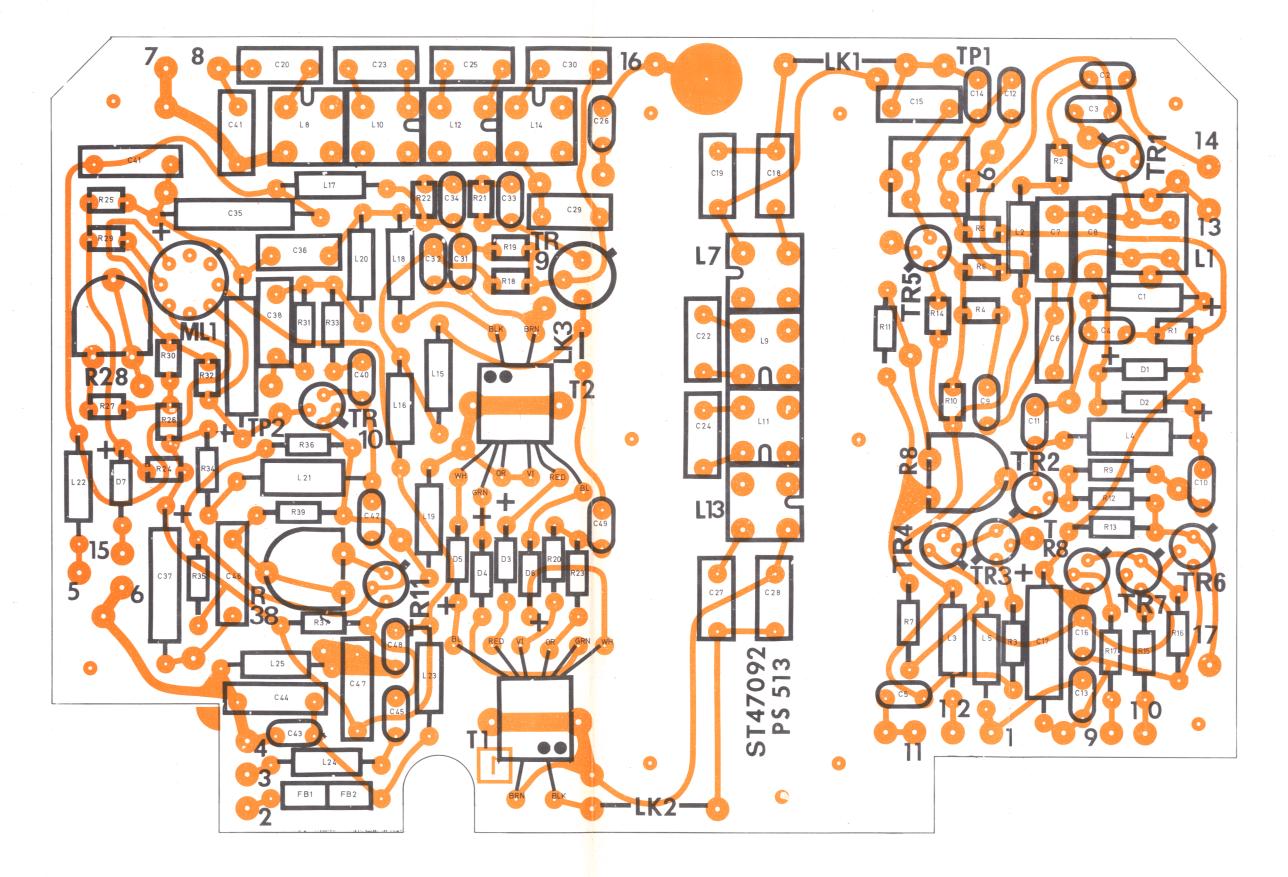

10. The 35.4 MHz first IF signal from the first mixer board is applied via a gain-controlled amplifier and bandpass filter to mixer 2 where it is mixed with the filtered and amplified 34 MHz signal from the synthesizer. The output signal from the mixer is applied via a 1.4 MHz low-pass filter to a variable attenuator (maximum attenuation approximately 20 dB). The gain of the buffer output amplifier is preset to obtain a voltage gain from board input to board output, of approximately 26 dB.

11. The stage gain of the input amplifier, and the attenuation level of the variable attenuator, are controlled by the d.c. output signal from the AGC combiner; this stage combines the AGC output signals from the main IF and (where fitted) the ISB IF boards, and produces a d.c. output voltage, the level of which is equal to the higher of the two input voltage levels.

### IF FILTER BOARD

12. A total of six 1.4 MHz crystal filters may be fitted to the IF filter board. In standard production receivers two filter positions are occupied by the mode-selected SSB or ISB filters which allows up to four symmetrical filters to be fitted. If, however, a standard receiver is equipped with the AFC facility, a carrier filter is fitted which limits the number of symmetrical filters to three. If the receiver is equipped say, for USB only, then space is available for the fitting of five symmetrical filters.

13. Filter switching is accomplished using transmission gates which are controlled by logic '0' signals from the interface unit. Due to inversion within the receiver, the filter selected for USB operation has LSB characteristics and that selected for LSB operation has USB characteristics. In SSB receivers the 1.4 MHz output signal from the selected filter is applied to the main IF board; in ISB versions (when ISB is selected) a second output signal is applied to the ISB IF board.

### IF BOARD

14. The optionally fitted ISB IF board is identical to the main IF board. The 1.4 MHz output signal from the IF filter board is applied to a gain controlled IF amplifier and then to mixer 3 where it is mixed with the 1.5 MHz signal from the synthesizer. The difference frequency output from the mixer is applied via a 100 kHz bandpass filter to the AM and SSB detectors, and also via a further amplifier to the 100 kHz output sockets on the receiver rear panel. For SSB/ISB modes a product detector is used which receives a fixed 100 kHz input signal from the synthesizer; for the CW mode, a variable 100 kHz signal (plus or minus up to 4 kHz in 10 Hz steps) is used. When the AM mode is selected, the 100 kHz output signal from the synthesizer is switched off, and an envelope detector is selected by the application of a 0V signal from the interface unit. The output signal from the detector is applied via a low-pass filter and an audio pre-amplifier stage to the AF board.

15. An output signal from the gain controlled input amplifier is applied via an overload limiter stage to the AGC detector and amplifier stages. These include the AGC time constant circuits, and the d.c. output voltage, the level of which is proportional to the level of the IF input signal, is applied to the input amplifier and also to the AGC combiner on the second mixer board.

16. The mute input signal to the 100 kHz output amplifier and the audio pre-amplifier is routed from the rear panel MUTE terminal. When an earth is applied to this terminal (either directly at the rear panel or via the serial data and the interface unit), the 100 kHz and audio output signals are switched off.

### AF BOARD

17. The AF board contains three gain-controlled audio amplifiers; one provides the audic output to the phones and loudspeaker, whilst the remaining two provide audio line outputs. The audio input switching is controlled by the interface unit in accordance with the control settings at the control panel. Note that for SSB receivers, or ISB receivers set for SSB operation, the two audio line amplifiers are fed from a common input. The preset gain-adjustment potentiometers for the three amplifiers are mounted on the receiver front panel (which forms part of the interface unit – Part 4).

# <u>CHAPIER\_2</u>

# <u>RF\_UNIT</u>

### CONTENTS

|                                                   | Para. |

|---------------------------------------------------|-------|

| INTRODUCTION                                      | 1     |

| RE-RADIATION FILTER                               | 2     |

| RF BOARD PS514                                    |       |

| Wideband Protection Stage                         | 3     |

| In-band Protection Stage                          | 6     |

| Attenuator Control Circuit                        | 8     |

| Diode Protection Circuit                          | 12    |

| RF Amplifier                                      | 13    |

| HALF-OCTAVE FILTER BOARD PS549<br>COMPONENTS LIST | 14    |

#### ILLUSTRATIONS

| Circuit and Layout: Re-radiation Filter         | 2.1 |

|-------------------------------------------------|-----|

| Circuit Diagram: RF Board PS514                 | 2.2 |

| Layout: RF Board PS514                          | 2.3 |

| Circuit Diagram: Half-Octave Filter Board PS549 | 2.4 |

| Layout: Half-Octave Filter Board PS549          | 2.5 |

Fig. No.

### <u>CHAPIER\_2</u>

### <u>RF\_UNIT</u>

### INTRODUCTION

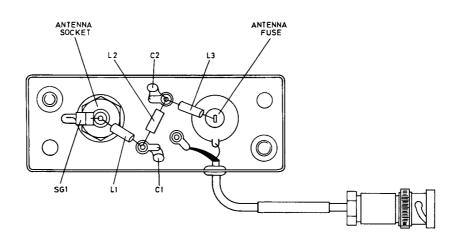

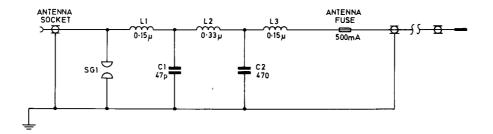

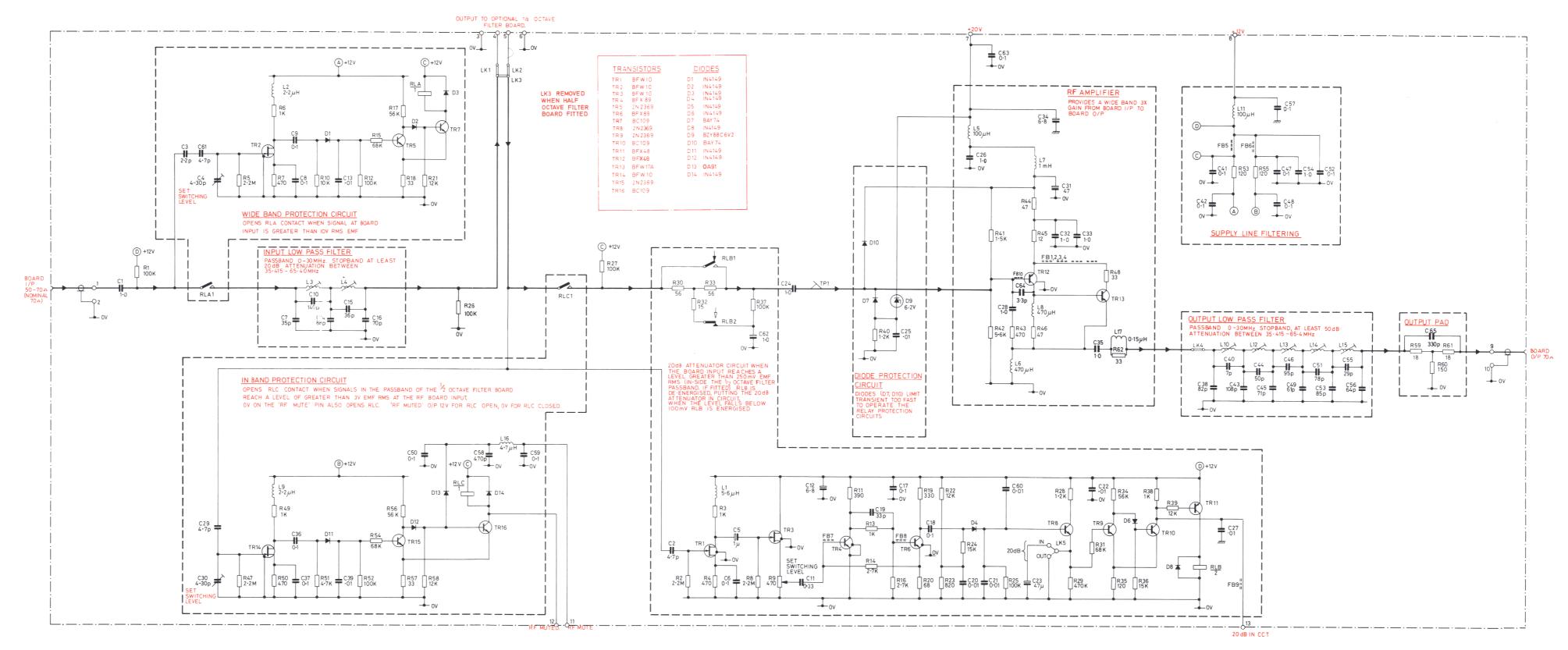

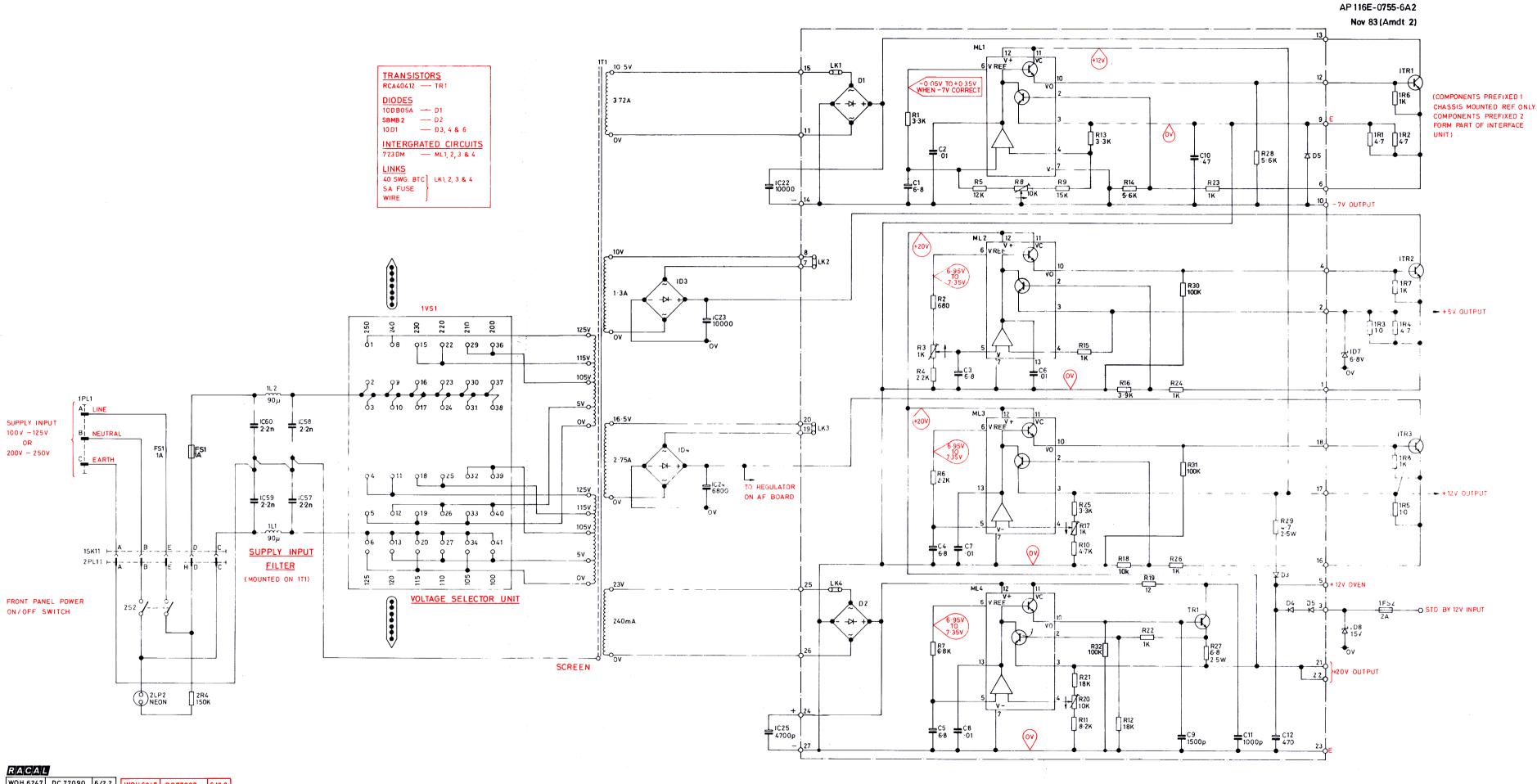

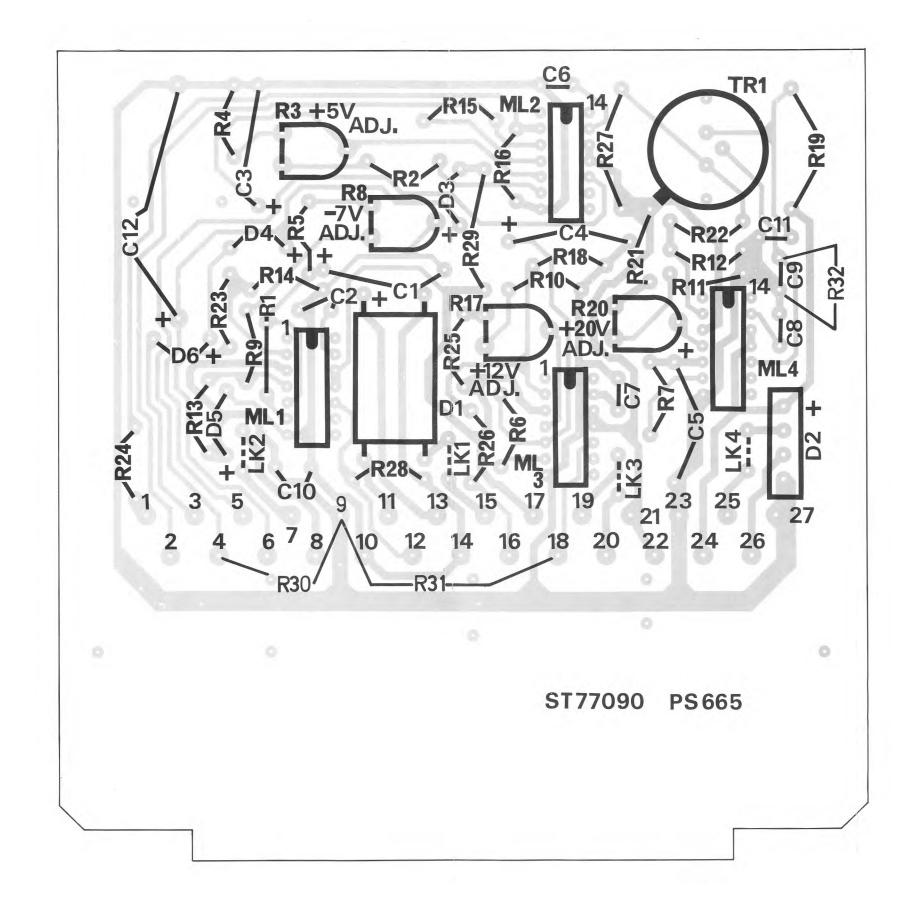

1. This chapter describes the re-radiation filter, RF board and the optional half-octave filter board, which are mounted in the RF unit. The circuit diagram of the re-radiation filter is given in fig. 2.1, the circuit of the RF board is given in fig. 2.2, and the circuit diagram of the half-octave filter board is given in fig. 2.4.

### **RE-RADIATION FILTER**

The re-radiation filter is housed in a small metal box which is mounted on the rear face of the RF unit. It carries the antenna socket, together with a protection fuse and a spark gap. The RF connection to the RF board is made via a flying lead terminated in a BNC connector. Re-radiation with the antenna input terminated into 50 ohms is less than 10 microvolts.

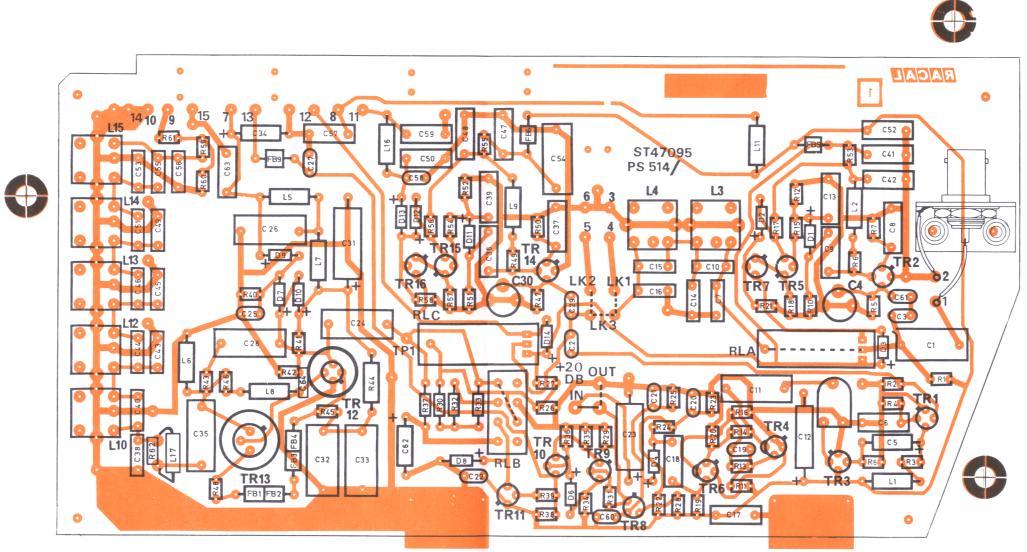

### RF BOARD PS514

### Wideband Protection Stage

3. The received signal from the re-radiation filter is applied to the wideband protection stage via board pin 1 and C1. Under normal reception conditions, TR5 is cut off; this allow TR7 to conduct, RLA/1 is energised and contact RLA1 is closed.

4. Should the amplitude of the received signal at the antenna socket exceed a pre-determined threshold level (set by C4), the detected output from TR2 causes TR5 to conduct; TR7 is thus turned off, RLA/1 is de-energised, and contact RLA1 opens to break the path of the RF signal. The threshold is set by C4 such that RLA/1 becomes de-energised for signals which exceed approximately 10V r.m.s. emf at the antenna socket.

5. From relay contact RLA1, the received signal is applied to a 0 to 30 MHz low-pass filter; the stop-band characteristic of this filter is designed to introduce at least 20 dB attenuation between 35.415 and 65.4 MHz (the range of the local oscillator signal from the synthesizer). The filtered output is routed by LK3, or LK1, the half-octave filter board and LK2 (para. 14) to the in-band protection stage (para. 6) and the attenuator control circuit (para. 8).

### In-band Protection Stage

6. The in-band protection stage, which is similar to the wideband protection stage, is only operational in receivers equipped with the optional half-octave filter board (para. 14). Under normal reception conditions TR15 is cut off, TR16 is turned on and relay RLC/1 is energised; contact RLC1 is closed and the path of the RF signal is completed.

Part 3 2–1 Should the amplitude of the received signals at the antenna socket, which are within the passband of the selected half-octave filter, exceed a pre-determined threshold level (set by C30), the detected output from TR14 causes TR15 to conduct; TR16 is turned off, RLC/1 is de-energised, and contact RCL1 opens to break the path of the RF signal.

7. The threshold is set by C30 such that RLC/1 becomes de-energised for in-band signals which exceed approximately 3V rm.m.s. emf at the antenna socket.

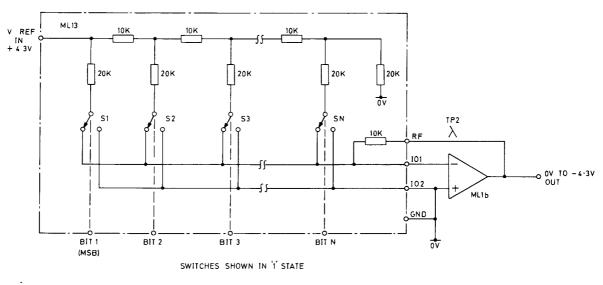

### Attenuator Control Circuit

From relay contact RLC1, the received signal is applied to the diode protection circuit, either via relay contact RLB1 and C24 or via a 20 dB attenuator, R30, R32, R33, and C24. Relay RLB/2 is controlled by the attenuator control circuit such that when the signal level at the board input exceeds approximately 250 mV r.m.s. emf (within the passband of the half-octave filter, if fitted), the relay is de-energised; RLB1 is opened, RLB2 is closed, and the attenuator is brought into circuit. The 20 dB attenuator may be linked out if not required by the setting of link LK5.

9. The attenuator control circuit comprises a high impedance FET input amplifier TR1, TR3, a 0 to 30 MHz wideband amplifier TR4, TR6, detector diode D4, buffer stage TR8, a Schmitt trigger TR9, TR10, and the relay driver stage TR11. Under normal reception conditions, TR9 is cut off, TR10 is turned on, and thus the conduction of TR11 energises relay RLB/2. Should the level of the input signal at the antenna socket exceed a pre-determined threshold level (set by R9), the detected output levels from TR6 causes increased conduction of TR8 which turns on TR9; TR10 is turned off and this turns off TR11 to de-energise RLB/2.

10. The fast rise/slow decay time constant presented by C23 and R29 provides a delay of approximately five seconds; this stops the switching action of the Schmitt trigger for transients which exceed the threshold level.

11. When the 20 dB attenuator is in circuit, the voltage level at the collector of TR10 (approximately +12V) is applied to board pin 10; this is routed to the interface unit and a signal is sent to the control panel via the revertive data to indicate that 20 dB must be added to the signal strength meter reading.

### **Diode Protection Circuit**

12. This circuit uses two fast-action switching diodes D7, D10, and a 6.2V zener diode D9. Under normal reception conditions the d.c. voltage at TP1 is approximately +16V, the voltage at the anode of D7 is approximately +12V and the voltage at the cathode of D10 is approximately +19V; thus both D7 and D10 are reverse biased. Should a high voltage transient signal be induced into the antenna (lightning, etc) which is too fast to operate the relay protection circuits, then the respective diode will conduct, i.e. D7 for negative and D10 for positive transients, to protect the RF amplifier stage.

### **RF** Amplifier

13. The RF amplifier stage TR12, TR13, has a wideband characteristic over the frequency range 15 kHz to 30 MHz, and provides a gain, from board input to board output, of approximately three times. The amplified output signal is coupled via C35, LK4, a 0 to 30 MHz low-pass filter, a 70 ohms impedance pad and board pin 7, to the first mixer board.

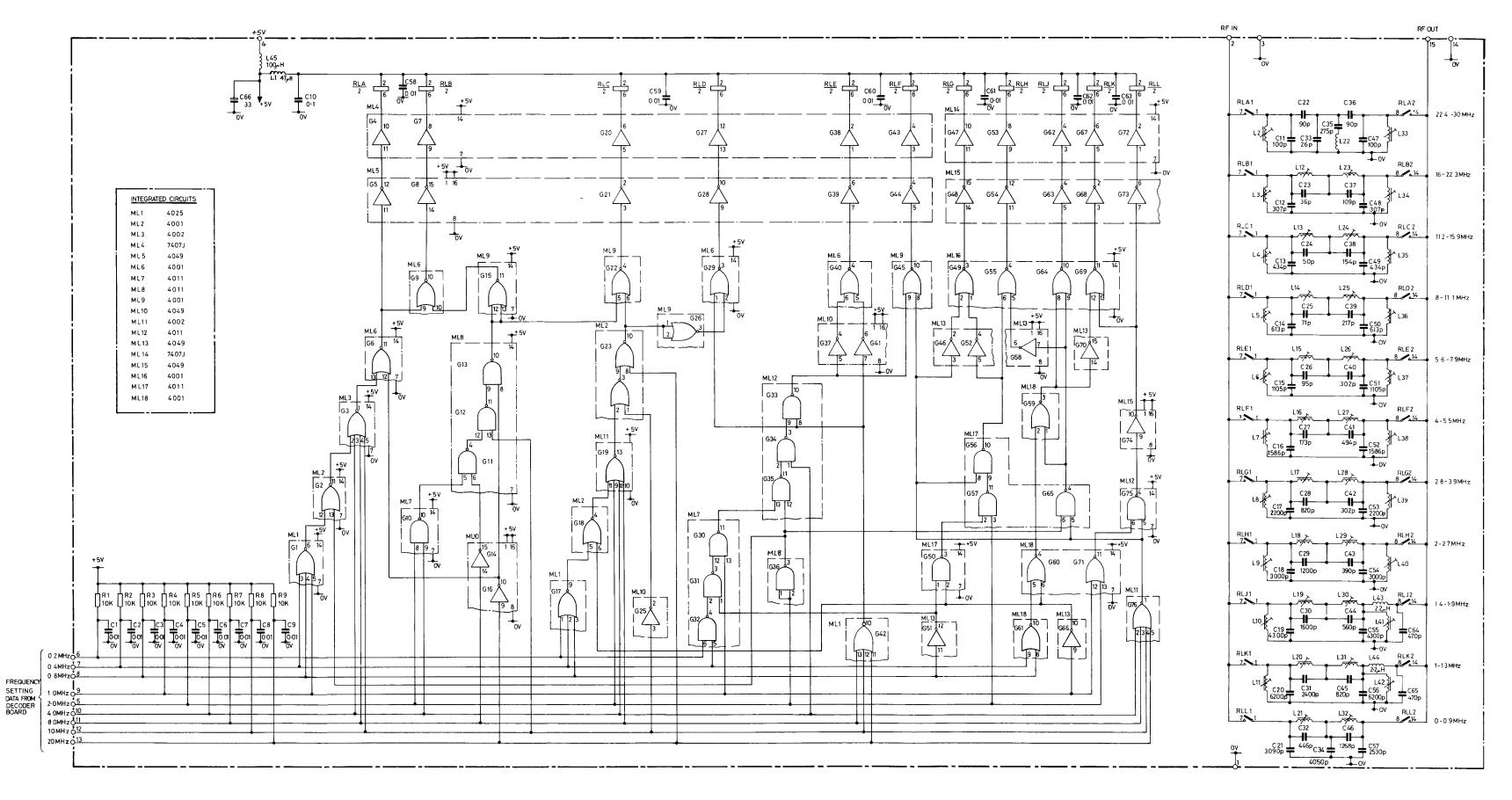

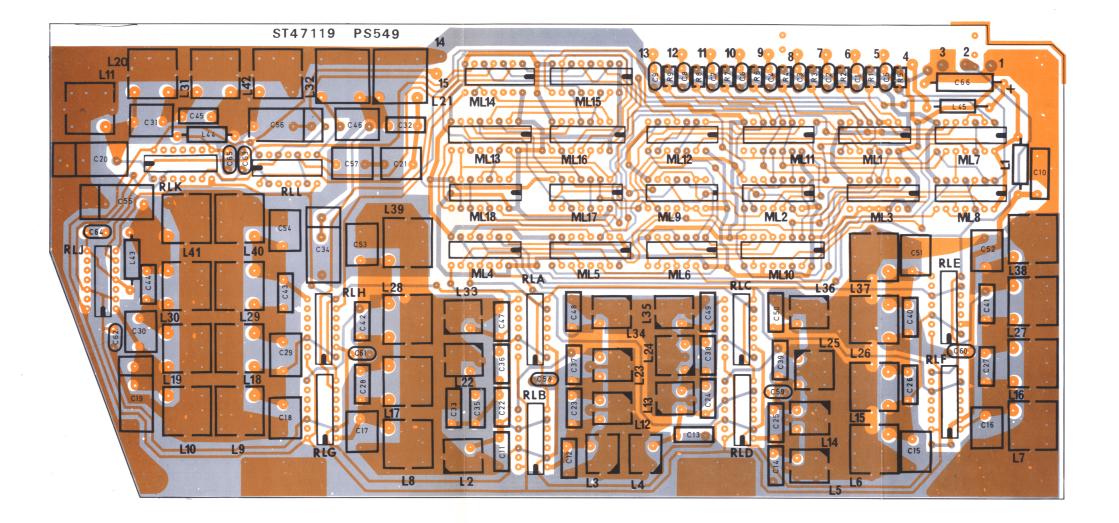

### HALF-OCTAVE FILTER BOARD PS549

14. The optional half-octave filter board (fig. 2.4) contains ten bandpass filters, covering the frequency range 1 to 30 MHz, and a low-pass filter for frequencies below 1 MHz. Filter selection is achieved by the use of relays; the BCD frequency setting information from the decoder board, at board pins 5 to 13, is applied to a network of NOR gates, NAND gates and inverting buffers, and the appropriate relay is energised via an open-collector buffer/driver (ML4 or ML14).

Circuit & Layout : Re-radiation Filter

Part 3 Fig. 2·1

Circuit : RF Board PS514

Part 3 Fig.2·2

i f

REFER TO MOD No A9599

| racal       |            |     |

|-------------|------------|-----|

| WOH 6247    | DA 47094/4 | 2.3 |

| 1           |            | 1/2 |

| WOH 6 2 4 7 | DA 47054/4 | 2.3 |

| 1           |            | 2/2 |

AP116E-0755-6A2 Aug 85(Amdt 3)

# Layout: R F Board

Part 3 Fig 2.3

Circuit Part 3 Half Octave Filter Board PS549 Fig. 2·4

| RACAL       |              |     |

|-------------|--------------|-----|

| WOH 6247    | DA 47118/4   | 2.5 |

| 1           |              | 1/3 |

| WOH 6247    | DA 47118 / 4 | 2.5 |

| 1           |              | 2/3 |

| WOH 6-2 4 7 | DA 57118/3   | 2.5 |

| 1           |              | 3/3 |

# Layout: Half Octave Filter Board

Part 3 Fig. 2·5

Fig.No.

# CHAPTER 3

# FIRST MIXER BOARD PS512

#### CONTENTS

|                                   | Para. |

|-----------------------------------|-------|

| INTRODUCTION                      | 1     |

| LOCAL OSCILLATOR FILTER SWITCHING | 3     |

| DRIVE AMPLIFIER                   | 5     |

| METER DRIVE CIRCUIT               | 6     |

| FIRST MIXER                       | 7     |

| 35.4 MHz BUFFER AMPLIFIER         | 10    |

|                                   |       |

#### ILLUSTRATIONS

| Circuit Diagram: First Mixer Board PS512 | 3.1 |

|------------------------------------------|-----|

| Layout: First Mixer Board PS512          | 3.2 |

.

### <u>CHAPIER\_3</u>

### FIRST\_MIXER\_BOARD\_P\$512

### INTRODUCTION

The received RF signal from the RF board, in the frequency range 15 kHz to 30 MHz, is applied to the first mixer board where it is mixed with the filtered and amplified 35.415 to 65.4 MHz local oscillator signal from the synthesizer. The difference frequency output, at 35.4 MHz, is applied to a crystal bandpass filter and is then amplified before application to the second mixer board. A second output from the local oscillator drive amplifier is rectified to produce a d.c. output voltage which is proportional to the drive level; this voltage is applied to the front panel meter via the interface unit.

2. The circuit diagram of the first mixer board is given in fig. 3.1.

### LOCAL OSCILLATOR FILTER SWITCHING

3. The local oscillator signal, at board pin 28, is applied to one of two bandpass filters, dependent on the receiver frequency range. For receiver frequencies in the range 15 kHz to 3.9 MHz, an earth is applied (via a diode) to board pin 29; this is routed to D2 via L3 and also to D4 via L15. Diode D2 is forward biased and opens a path for the local oscillator signal to a crystal notch filter (passband 35.415 to 39.4 MHz, with a notch frequency of 35.400 MHz) via C3, D2 and C9. Diode D4 is also forward biased and routes the output signal from the crystal filter to the drive amplifier via C34, D4, C41 and the impedance matching pad. Diodes D3 and D5 are reverse biased and thus isolate the LC bandpass filter.

For receiver frequencies in the range 4 to 30 MHz, an earth is applied (via a diode) to board pin 26; diodes D3 and D5 are forward biased, D2 and D4 are reverse biased, and the local oscillator signal is routed via C4, D3 and C7 to the LC bandpass filter. The output from this filter (passband 39.4 to 65.4 MHz) is then routed to the drive amplifier via C35, C42 and the impedance matching pad.

### DRIVE AMPLIFIER

5. The mixer drive amplifier comprises a common-emitter pre-amplifier stage TR2, followed by an emitter-coupled differential power amplifier stage TR3, TR6. The balanced output signal is coupled by transformer T4 to the first mixer circuit (via T6) and also to the meter drive circuit (para. 6).

### METER DRIVE CIRCUIT

6. The local oscillator drive signal output from transformer T4 is rectified by D6, smoothed, and then applied to a source follower TR9. R47 is adjusted for a front panel meter indication within the green band for a correct local oscillator drive level to the first mixer.

Part 3

### FIRST MIXER

7. The mixer is of the switching balanced-ring type and uses four N-channel insulated gate field effect transistors TR4, TR5, TR7 and TR8. The local oscillator signal is capacity coupled from T6 to the gate of each transistor whilst the RF input signal is coupled via T7 to the source of each transistor.

8. The transistors are switched in pairs, dependent on the direction of the applied local oscillator waveform (positive-going or negative-going); when the local oscillator signal at pin 5 is positive with respect to pin 7, transistors TR4 and TR8 are switched on whilst TR5 and TR7 are switched off. The RF input signal at T7 is then routed via TR4 and TR8 to the output transformer T5. Conversely, when pin 7 is positive with respect to pin 5, TR5 and TR7 are switched on, TR4 and TR8 are switched off, and the RF path is via TR5 and TR7.

9. The difference frequency output from the mixer, at 35.4 MHz, is coupled by T5 and LK2 to a 35.4 MHz crystal bandpass filter. In standard production receivers this filter (FL1) has a nominal bandwidth of ±6 kHz. An optional narrow filter, nominal bandwidth ±500 Hz (FL2), may also be fitted; this is selected on command from the interface unit which energises the relays.

### 35.4 MHz BUFFER AMPLIFIER

10. The filtered 35.4 MHz output signal from the mixer is coupled by LK1 and C3 to the tuned buffer amplifier stage TR1 (LK3 is not fitted). Inductor L11 is tuned for a maximum output at 35.4 MHz which is applied to the second mixer board via board pin 19.

### NOTE: BALANCED RING MIXER TRANSISTORS

The balanced ring mixer transistors TR4, TR5, TR7 and TR8 (type BSV81) are fitted as a matched quad, Racal part number 927897 (Manufacturer General Instruments). These transistors are colour coded (in accordance with the onresistance with Vgs at 6V) and a failed transistor should be replaced with a similarly coded device. In an emergency situation, or where a degraded specification in respect of the response to external suprious signals is acceptable, then a mixture of devices with two only adjacent colours may be fitted.

| COLOUR | ON-RESISTANCE (ohms) |

|--------|----------------------|

| BLACK  | 25 to 30             |

| ORANGE | 30 to 35             |

| RED    | 35 to 40             |

| GREY   | 40 to 45             |

| YELLOW | 45 to 50             |

| GREEN  | 50 to 55             |

| BLUE   | 55 to 60             |

| VIOLET | 60 to 65             |

Circuit First Mixer Board PS512

Part 3 Fig. 3·1

| RAC |      | DA | 47088/2 | 3·2<br>2/3 |

|-----|------|----|---------|------------|

| WOH | 6247 | DA | 47088/4 | 3.2        |

| 1   |      |    |         | 1/3        |

| ₩ОН | 6247 | DA | 47088/3 | 3.2        |

| 1   |      |    |         | 3/3        |

Layout : First Mixer Board

Part 3 Fig. 3-2

Fig.No.

# CHAPTER 4

# SECOND MIXER BOARD PS513

#### CONTENTS

|                               | Para. |

|-------------------------------|-------|

| INTRODUCTION                  | 1     |

| 35.4 MHz IF AMPLIFIER         | 2     |

| INPUT ATTENUATOR CONTROLLER   | 3     |

| SECOND MIXER DRIVE CONTROLLER | 5     |

| SECOND MIXER                  | 6     |

| OUTPUT ATTENUATOR CONTROLLER  | 7     |

| OUTPUT BUFFER AMPLIFIER       | 9     |

| ILLUSTRATIONS                 |       |

| Circuit Diagram: Second Mixer Board PS513 | 4.1 |

|-------------------------------------------|-----|

| Olicato Diagram. Decona mixer Dourd 10919 |     |

| Layout: Second Mixer Board PS513          | 4.2 |

►

### <u>CHAPIER\_4</u>

### SECOND MIXER BOARD PS513

### INTRODUCTION

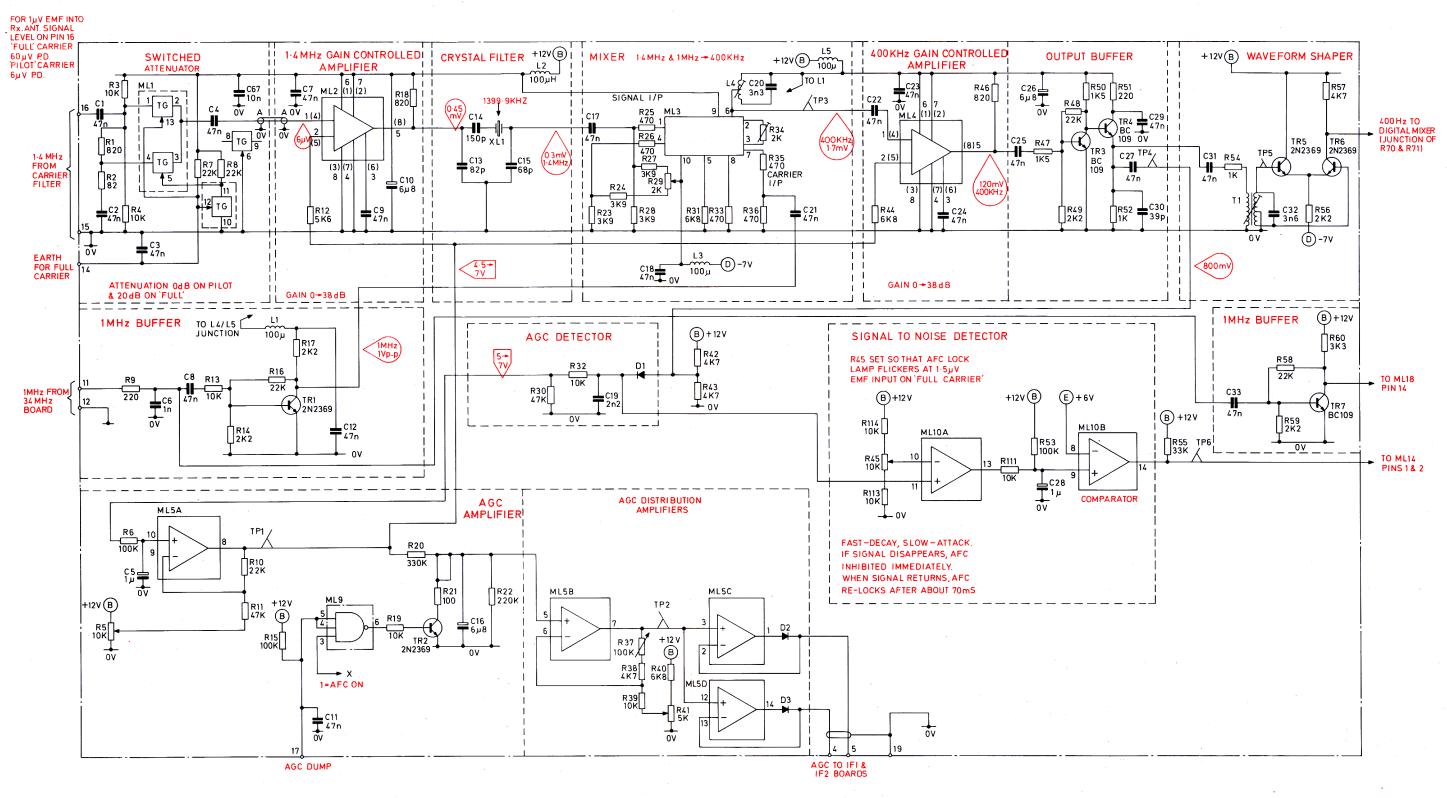

The 35.4 MHz IF output signal from the first mixer board is amplified and filtered before application to the second mixer; here it is mixed with the filtered and amplified 34 MHz signal from the synthesizer and the resultant 1.4 MHz output signal is applied via a voltage-controlled attenuator to a buffer amplifier stage. The board also contains an AGC voltage combiner; this stage combines the AGC voltages from the main IF and (where fitted) the ISB IF boards. The output is used to control the gain of the 35.4 MHz IF amplifier and the 1.4 MHz buffer amplifier. The circuit diagram of the board is given in fig. 4.1.

### 35.4 MHz IF AMPLIFIER

2. The 35.4 MHz IF input at board pin 14 is coupled by C2 to a gain-controlled amplifier stage TR1. The output signal from the tuned circuit L1, C6, C7 is coupled via C9 to a further amplifier stage TR5, and via C8 to a pair of PIN diodes D1, D2. The impedance of these diodes (which are parallel-connected for RF and appear across L1) is a function of the forward direct current flowing through the diodes; when no current is flowing the impedance is extremely high and this impedance is progressively reduced as the forward current rises. The current flowing through the diodes is set by the input attenuator controller, which in turn is controlled by the level of the AGC voltage from the AGC combiner. The amplified output signal is applied to the second mixer via LK1 and a 35.4 MHz bandpass filter.

### INPUT ATTENUATOR CONTROLLER

The AGC voltage output from emitter follower TR6 (the level of which is the greater of the two inputs V agc 1 and V agc 2) is applied to a differential amplifier TR2, TR4. The threshold level at which TR2 begins to conduct is defined by R8 and TR4; R8 is adjusted so that when the signal level at the antenna socket reaches 0.75 mV emf, the level of the AGC voltage output from the emitter of TR6 is just sufficient to cause TR2 to conduct. TR3 is a current source for TR2 and TR4, and thus limits the maximum current flow through the PIN diodes.

4. Since the conduction of TR2 controls the current flow through the two PIN diodes, an increase in the applied AGC voltage increases the current flow through the diodes and the output level from TR1 is maintained.

### SECOND MIXER DRIVE AMPLIFIER

5. The 34 MHz signal from the synthesizer, at board pin 8, is applied via a 34 MHa bandpass filter to a drive amplifier stage TR9. The amplified output, at approximately 8V peak-to-peak, is applied as the switching input to the second mixer.

Part 3

### SECOND MIXER

6. This is a balanced switching diode mixer comprising two transformers T1, T2, and four diodes D3 to D6. The 35.4 MHz signal is applied via LK2 to the primary winding of T1, and the 34 MHz switching input is applied to the centre-tapped secondary windings of T1 via R20 and R23. The output signal from T2 is applied via a 1.4 MHz low-pass filter and a voltage-controlled attenuator to the output buffer amplifier.

### OUTPUT ATTENUATOR CONTROLLER

7. The voltage controlled attenuator comprises R31, R33, C40 and TR10. The sourceto-drain impedance of TR10 is controlled by the level of the voltage applied to the gate; when fully on the attenuator produces approximately 20 dB attenuation.

8. The output from the AGC voltage combiner (V agc 3) is applied via board pin 15, D7 and R9 to the positive input terminal of an operational amplifier ML1. The voltage applied to the negative input terminal of ML1 is set by R28; this is adjusted so that when the signal level at the antenna socket reaches 0.75 mV emf, the level of the output voltage from ML1 is just sufficient to cause TR10 to conduct. An increase in the level of the applied AGC voltage increases the output voltage from ML1; this increases the conduction of TR10 and the level of the 1.4 MHz signal applied to the output buffer stage is reduced.

### OUTPUT BUFFER AMPLIFIER

9. The 1.4 MHz output signal from the voltage controlled attenuator is coupled by C42 to the output buffer amplifier stage TR11. R38 is adjusted for a gain, from board input to board output, of 26 dB ±5 dB. The 1.4 MHz IF output is applied via board pin 3 to the IF filter board.

| RACAL    |          |       |   |          |          |       |

|----------|----------|-------|---|----------|----------|-------|

| WOH 6247 | DC 47092 | 3/4.1 | V | VOH 6247 | DC 47092 | 3/4.1 |

| 12       |          | 1/2   | 1 |          |          | 2/2   |

Circuit: Second Mixer Board PS 513

Part 3 Fig 4.1

Layout: Second Mixer Board Fig.4.2

# CHAPTER 5

IF FILTER BOARD PS663

#### CONTENTS

|                                  | Para.   |

|----------------------------------|---------|

| INTRODUCTION<br>FILTER SELECTION | 1<br>5  |

| FILLER SELECTION                 | 2       |

| ILLUSTRATIONS                    |         |

|                                  | Fig.No. |

| Circuit Diagram: IF Filter Board PS663 | 5.1 |

|----------------------------------------|-----|

| Layout: IF Filter Board PS663          | 5.2 |

# <u>CHAPIER\_5</u>

# <u>IE\_FILTER\_BOARD\_PS663</u>

### INTRODUCTION

1. The filter board contains the 1.4 MHz sideband and/or symmetrical crystal filters; up to six filters may be fitted and these are dependent on the various options available.

For SSB receivers (fitted for both upper and lower sideband operation) and ISB receivers, FL1 is the LSB channel filter whilst FL2 is the USB channel filter. If 6 kHz sideband filters are fitted at positions FL1 and FL2, the increased physical size of these filters precludes the fitting of a filter at position FL4.

- NOTE: Due to the inversion within the receiver the USB channel filter has LSB characteristics and the LSB channel filter has USB characteristics.

- 3. In receivers equipped with the optional AFC facility a narrow-band carrier filter is fitted at position FL3, links LK2 and LK4 are broken, and links LK1 and LK3 are made.

4. The remaining filter positions may be occupied by symmetrical filters, one of which may be selected for AM or CW modes. If the receiver is equipped for AM and CW only, then all six filter positions may be fitted with symmetrical filters; these may be selected from the following (the widest bandwidth filter is fitted at position FL6):

0.3 kHz, 1 kHz, 3 kHz, 6 kHz, 8 kHz, 13 kHz.

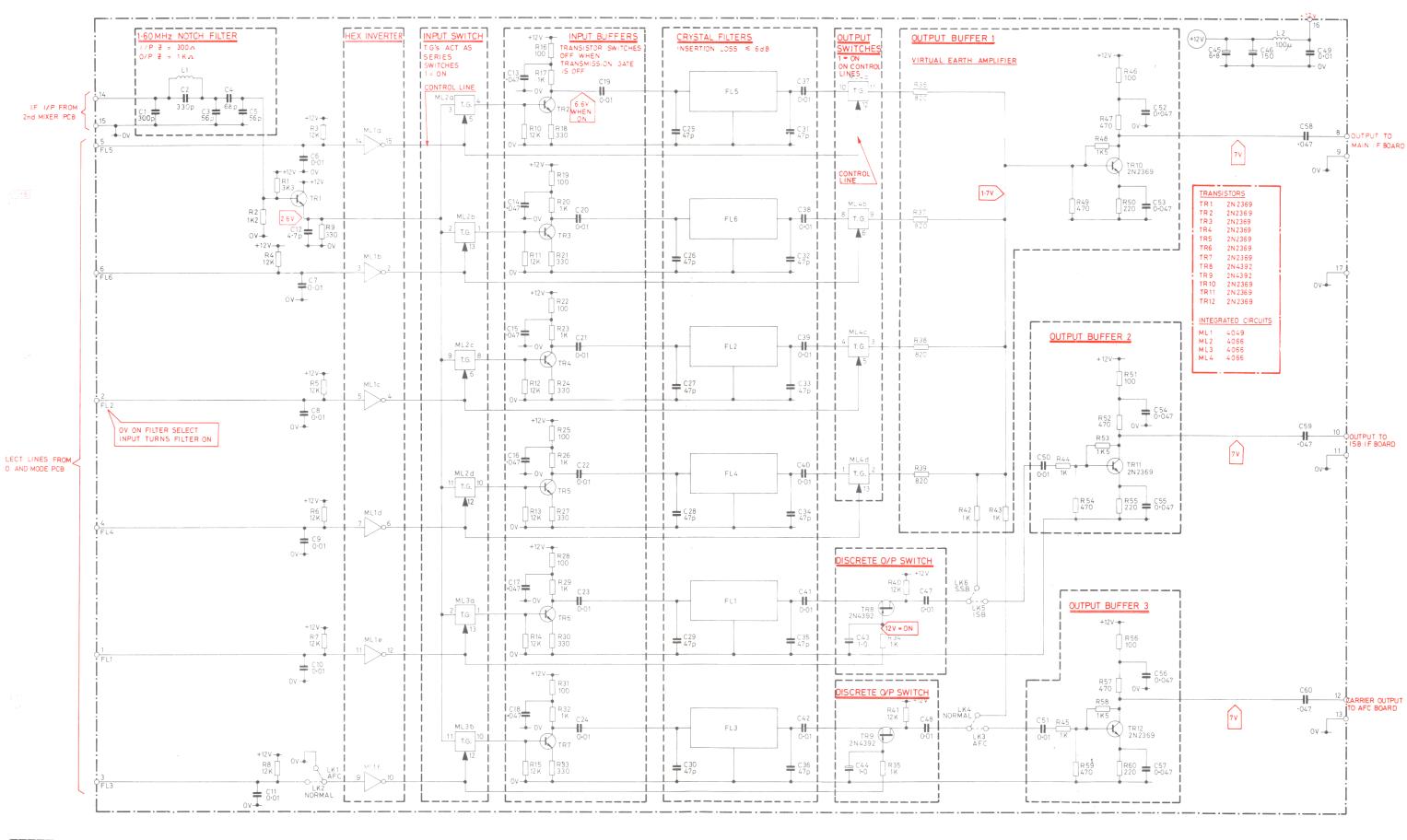

### FILTER SELECTION (fig. 5.1)

5. The 1.4 MHz IF input signal from the second mixer board, at board pin 14, is applied to a 1.60 MHz notch filter (in earlier versions - serial numbers 120 to 264 - a

1.575 MHz notch filter was fitted. See components list for values of capacitors C1 to C5). From the notch filter the signal is applied to emitter follower stage TR1, and then in parallel to a bank of six transmission gates.

- 6. Since the selection circuitry is the same for each filter, only one example is given, that for filter FL5.

- 7. To select FL5 an earth is applied to board pin 5; this is inverted by ML1a and a

logic '1' is applied to the control inputs of transmission gates ML2a and ML4a. The gates are opened and the 1.4 MHz signal from TR1 is applied via ML2a and the input buffer stage TR2 to filter FL5. The filtered output is routed via C37 and ML4a to a virtualearth buffer-amplifier stage TR10; this stage has a gain of approximately two times (ratio of input resistor R36 to feedback resistor R48) and the output signal is routed to the main IF board via C58 and board pin 8.

> Part 3 5–1

8. The output buffer stage TR11 is only used for ISB versions of the receiver (link LK6 broken, LK5 made); output buffer stage TR12 is only used for receivers equipped with the AFC facility (links LK2 and LK4 broken, LK1 and LK3 made).

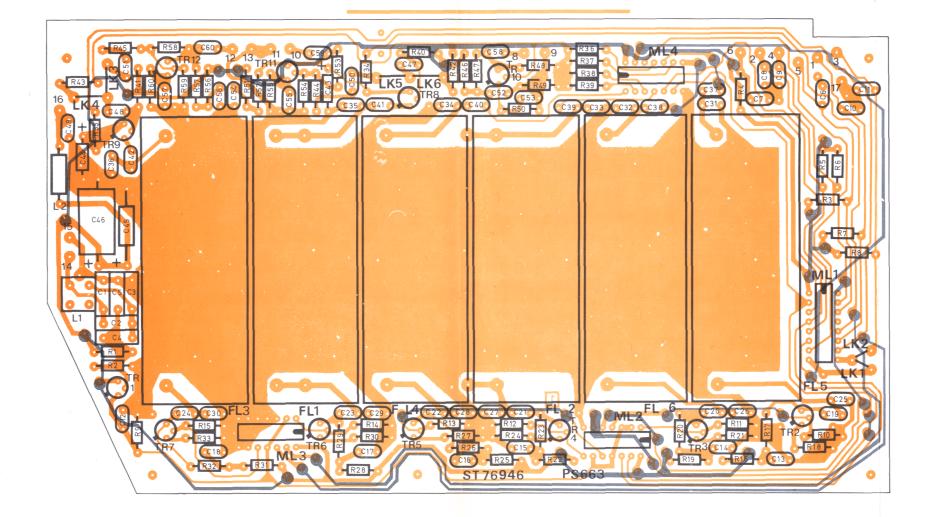

## Circuit : IF Filter Board PS663

Part 3 Fig. 5.1

Layout: IF Filter Board

Part 3 Fig.5·2

# CHAPTER 6

IF BOARD PS661

#### CONTENTS

|                              | Para. |

|------------------------------|-------|

| INTRODUCTION                 | 1     |

| GAIN CONTROLLED IF AMPLIFIER | 3     |

| THIRD MIXER                  | 4     |

| 100 kHz IF AMPLIFIER         | 6     |

| IF MUTE                      | 7     |

| AM AND PRODUCT DETECTOR      | 8     |

| AUDIO PRE-AMPLIFIER          | 11    |

| AF MUTE                      | 12    |

| AGC DETECTOR                 | 13    |

| AGC AMPLIFIER                | 14    |

| AGC Dump                     | 15    |

| AGC Hang                     | 18    |

#### ILLUSTRATIONS

#### Timing Diagram: AGC Hang Detector Circuit Diagram: IF Board PS661 Layout: IF Board PS661

Fig.No.

6.1 6.2

6.3

## <u>CHAPIER\_6</u>

### IF BOARD PS661

#### INTRODUCTION

1. This board contains a high-gain 1.4 MHz IF amplifier, the AGC detector and amplifier stages, the third mixer, the 100 kHz IF amplifier, the AM/SSB detectors and an audio pre-amplifier stage.

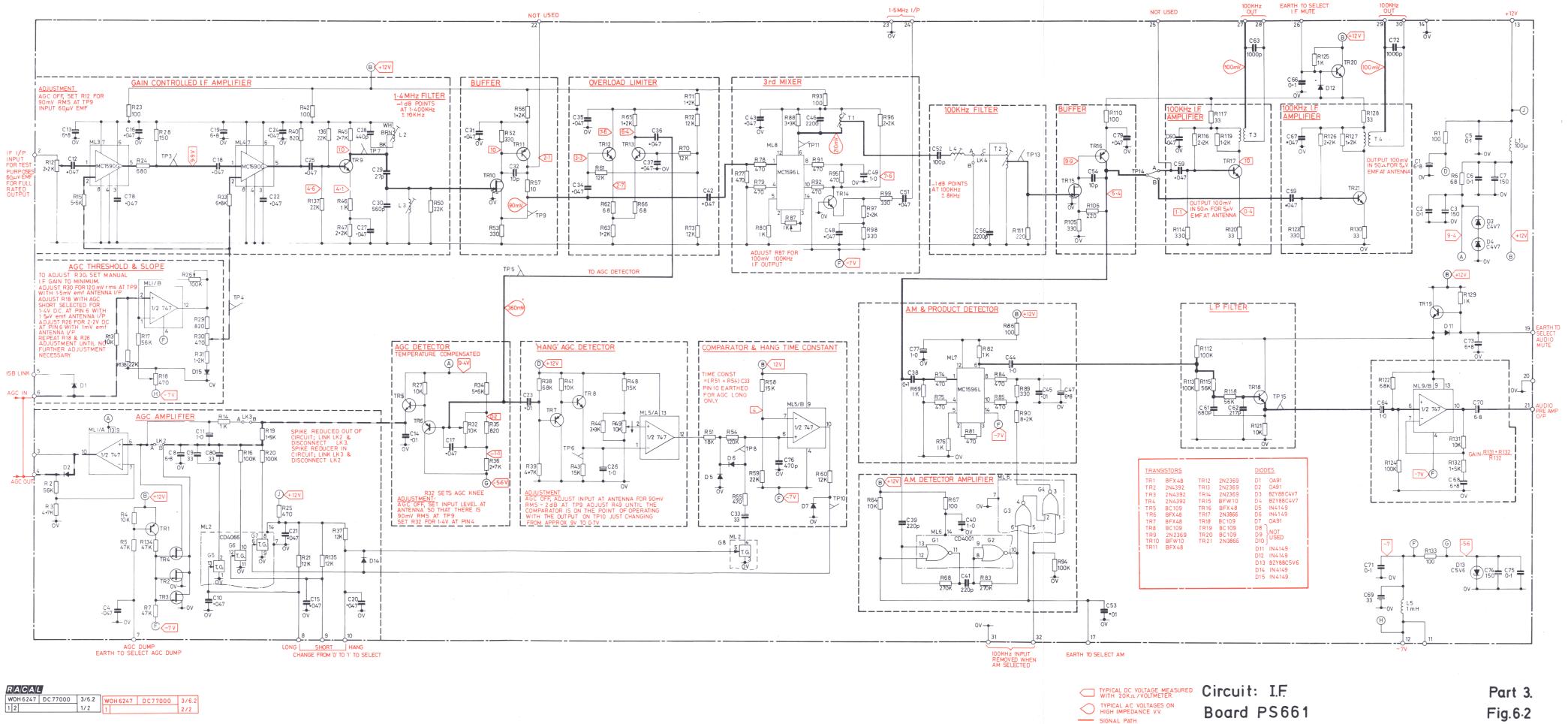

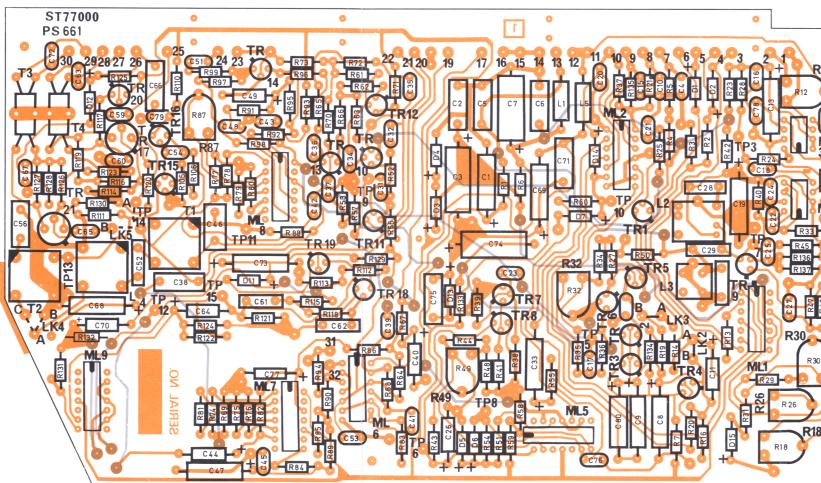

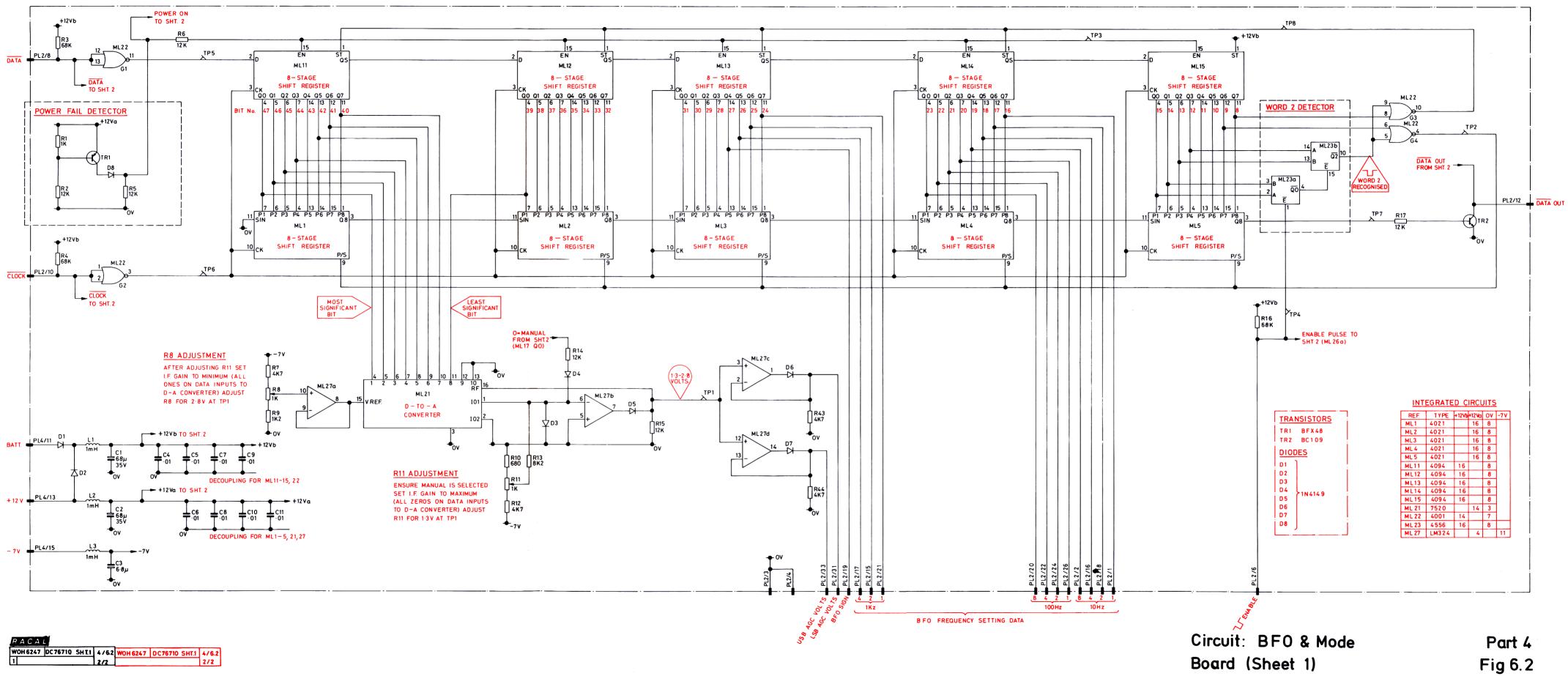

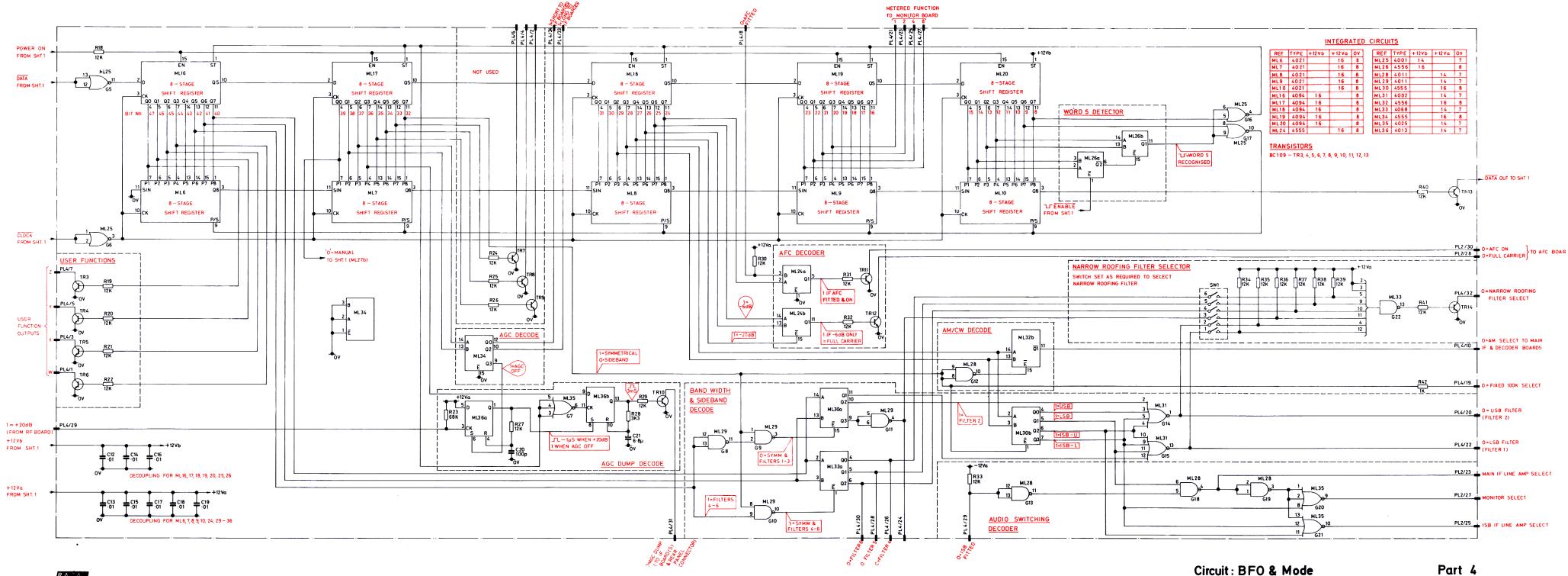

2. Two identical IF boards are fitted in ISB versions of the receiver; when ISB is selected, the main IF board carries the USB channel and the ISB IF board carries the LSB channel. The circuit diagram of the board is given in fig. 6.2.

#### GAIN CONTROLLED IF AMPLIFIER

3. The 1.4 MHz IF output signal from the IF filter board, at board pin 2, is applied to a two-stage integrated circuit amplifier ML3, ML4. The AGC voltage is applied to both amplifiers, via R15 to ML3 and via R33 to ML4. The output signal from ML4 is matched into a 1.4 MHz bandpass filter via TR9 and is then fed to a buffer amplifier TR10, TR11; the output at TR9 is applied to the AGC detector via C34 and an overload limiter (para. 13), and to the third mixer via C42.

#### THIRD MIXER

4. This stage mixes the 1.4 MHz IF signal from TR11 with the 1.5 MHz signal from the synthesizer (at board pin 24) to produce the final IF output signal at 100 kHz. A switching type of integrated circuit mixer is used, ML8, where the 1.4 MHz signal is applied to the signal input (pins 1 and 4) and the 1.5 MHz signal is applied to the switching (carrier) input (pins 8 and 10) via a grounded base voltage amplifier/buffer stage TR14.

5. The output signal from ML8, at pins 6 and 12, is applied to a 100 kHz bandpass filter, R88, C46, T1 and the components bounded by the dashed line; link LK4 is normally connected from A to C and is temporarily moved to position A-B during re-alignment. The gain of the mixer stage is set by R87; this is adjusted for a level of 100 mV at the 100 kHz output socket on the rear panel (connected to board pins 27 and 28) terminated into 50 ohms, with an input level of 5µV at the antenna socket.

#### 100 kHz IF AMPLIFIER

6. The output signal from the 100 kHz bandpass filter is applied to a buffer amplifier TR15, TR16 which feeds the AM and product detector (para. 8) and two 100 kHz IF amplifier stages, TR17, and TR21 (the links at TP14 are included for test purposes). From the main IF board, the two outputs at board pins 27, 28 and 29, 30 are taken to the two 100 kHz IF OUT sockets on the rear panel; for ISB versions, the output signal at pins 29 and 30 on the ISB IF board is taken to the ISB IF OUT socket on the rear panel, and the output at pins 27, 28 is not used.

### IF MUTE

7. When an earth is applied to the rear panel MUTE terminal, either directly or via the serial data from the control panel, it is routed to board pin 26; this turns off TR20 and the +12V supply is removed from the buffer amplifier and the two 100 kHz IF amplifiers.

### AM AND PRODUCT DETECTOR

8. This circuit uses a demodulator integrated circuit ML7. For SSB and CW reception, the 100 kHz IF signal is applied to the signal input (pins 1 and 4), and the 100 kHz signal from the synthesizer at board pin 32 (fixed frequency for SSB, variable by up to plus or minus 4 kHz for CW) is applied via NOR gate G4 to the carrier input (pins 8 and 10). The detected output signal, at pin 6, is coupled by C44 to an active low-pass filter TR18, and then to an audio pre-amplifier stage ML9B.

9. For AM reception, the 100 kHz signal is removed from board pin 32 and an earth is applied to board pin 17; this opens NOR gate G3 for the output signal from the AM detector amplifier, and the output NOR gate G4 is opened by the 0V input applied via R94.

10. The amplitude modulated 100 kHz IF signal is applied to the signal input of ML7 (as for SSB reception) and is also applied to the AM detector amplifier G1, G2; this effectively removes the amplitude modulation and produces a high-level squarewave output at the carrier frequency which is applied via G3 and G4 to the carrier input of ML7.

### AUDIO PRE-AMPLIFIER

11. The audio pre-amplifier uses an operational amplifier ML9B. Negative feedback is applied via R131 and the gain figure of approximately eight times is set by the ratio of R131 plus R132 to R132. The audio output at board pin 15 is applied to the AF board.

### AF MUTE

12. Board pin 19 is externally connected to board pin 26 (para. 7). When an earth is applied, TR19 is turned off and the +12V supply is removed from the low-pass filter and the audio pre-amplifier.

### AGC DETECTOR

13. The 1.4 MHz IF signal output from TR10, at TR9, is applied to the temperaturecompensated AGC detector stage TR5, TR6, via an overload-limited amplifier TR12, TR13; this stage has a linear gain characteristic up to the overload point when the output level remains constant for higher input signal levels. The positive output voltage from the detector is taken from the emitter of TR5 and is applied to the AGC amplifier.

### AGC AMPLIFIER

14. The positive output voltage from the AGC detector is applied via switched time constant components to a linear d.c. amplifier stage ML1A. R14 and C11 are provided for spike reduction and may be brought into circuit by making link LK3 and breaking link LK2. When AGC SHORT is selected, a '1' is applied to board pin 9; this is applied to the control input of transmission gate G6, and R16 is connected across the time constant capacitor C8. When AGC LONG is selected, the '1' input is transferred from board pin 9 to board pin 8 and the additional parallel-connected time constant capacitors C9, C80 are brought into circuit via transmission gate G5. Transmission gate G7 forms part of the AGC hang circuit described in para. 18.

### AGC Dump

15. The AGC dump circuit is activated each time AGC LONG is selected at the control panel. Its purpose is to discharge the time constant capacitors so that they may re-charge to the level of the signal being received. When an earth pulse is applied to board pin 7, TR1 conducts and turns on TR2, TR3 and TR4. TR2 and TR3, connected in parallel to produce a lower impedance, discharge time constant capacitors C8, C9 and C30, whilst TR4 discharges the spike reducer capacitor C11 when link LK2 is broken.

16. The AGC dump circuit is also used to effectively switch off the AGC when manual control of the IF gain is required; the earth is maintained at board pin 7, and the manual gain control voltage from the interface unit is applied to board pin 6 in place of the AGC output voltage from ML1A (diode D2 is thus reverse biased).

17. The gain control voltage at board pin 6 is applied to ML1B; this stage sets the AGC threshold and slope characteristics before application to the 1.4 MHz IF amplifier stages ML3, ML4.

### AGC Hang

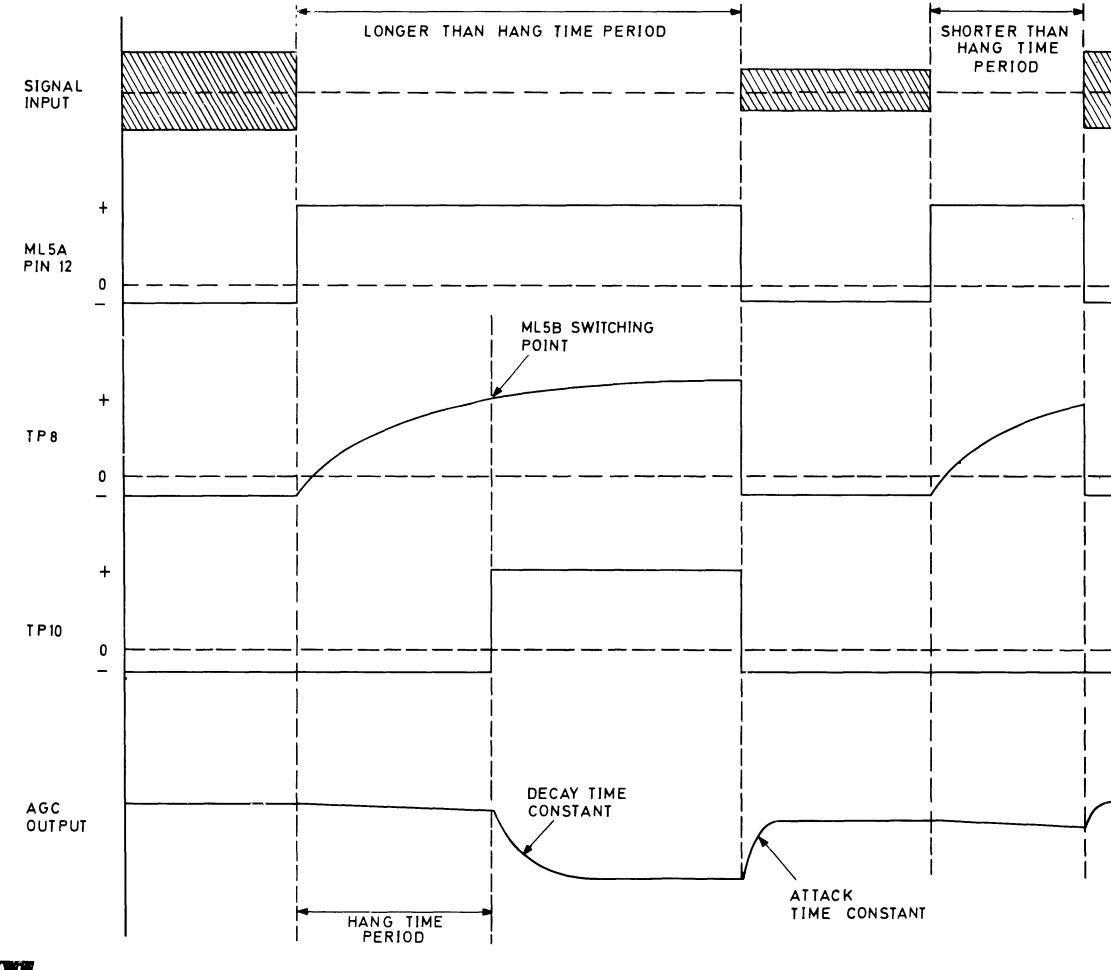

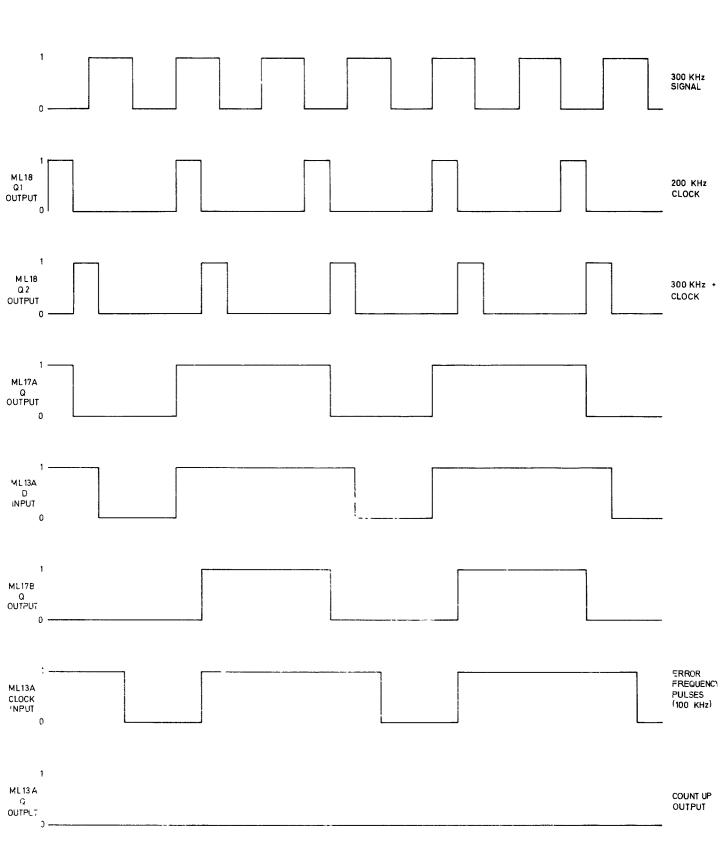

The AGC hang circuit maintains the level of the AGC output voltage from ML1A, following an interruption in the received transmission, for a period of approximately

5 seconds. The circuit is only operative when AGC LONG is selected.

19. The IF output signal from TR13 is coupled by C23 to a temperature-compensated detector stage TR7, TR8. The output from TR8 is applied to the inverting input of ML5A whilst R49 sets the voltage level applied to the non-inverting input such that the output at ML5A pin 12 is negative (clamped to approximately -0.7V by D5) when a received signal is present. This negative voltage is applied to the non-inverting input of comparator ML5B; the potential divider R58, R59 sets the voltage at the inverting input of ML5B to approximately +4V, and this results in a negative output at TP10, which is limited to approximately -0.7V by diode D7.

20. When a break in the received transmission occurs, the corresponding reduction in the emitter current of TR8 causes the voltage level at ML5A pin 1 to fall below the preset voltage level at ML5A pin 2; the output at ML5A pin 12 switches from negative to positive and capacitor C33 charges via R51, R54, R55 and transmission gate G8 (turned on by the '1' at board pin 10). Once the level of the exponentially rising voltage at ML5B pin 6 exceeds the level of the fixed potential applied to ML5B pin 7, the output at ML5B pin 10 switches from negative to positive; this is applied to the control input of transmission gate G7, the time constant capacitors discharge via R20 and G7, and the AGC voltage output from ML1A falls exponentially to zero.

When the received transmission recommences, the emitter current of TR8 rises, the output of ML5A switches from positive to negative and C33 rapidly discharges via R55, D6 and the low output impedance of ML5A. The output from ML5B switches from positive to negative, transmission gate G7 is turned off, and the AGC voltage from TR5 re-charges the time constant capacitors via R19.

22. The operation of the hang detector circuit, as described above, and also where the break in the received signal is shorter than the hang time period, is shown in the timing diagram fig. 6.1.

Timing Diagram : AGC Hang Detector

NOT TO SCALE

Part 3 Fig. 6·1

- - AGC LINE

| RACAL    | 3        |       |          |         |       |

|----------|----------|-------|----------|---------|-------|

| WOH 6247 | DC 77000 | 3/6.2 | WOH 6247 | DC77000 | 3/6.2 |

| 1 2      |          | 1/2   | 1        |         | 2/2   |

#### AP 116E 0755 6A2 Nov 83 (Amdt 2)

| RACAL    | DA76999/2  | 6·3<br>2/3 |

|----------|------------|------------|

| WOH 6247 | DA 76999/4 | 6.3        |

| 1        |            | 1/3        |

| WOH 6247 | DA75999/3  | 6.3        |

| 1        |            | 3/3        |

# Layout: IF Board

Part 3 Fig.6∙3

# CHAPTER 7

AF BOARD PM662

#### CONTENTS

|                                                                                             | Para.            |

|---------------------------------------------------------------------------------------------|------------------|

| INTRODUCTION<br>AUDIO INPUT SWITCHING<br>GAIN-CONTROLLED AMPLIFIERS<br>AF OUTPUT AMPLIFIERS | 1<br>4<br>6<br>7 |

| TABLES                                                                                      |                  |

| Table No.                                                                                   | Page             |

| 1 Audio Input Switching                                                                     | 7-2              |

| ILLUSTRATIONS                                                                               |                  |

|                                                                                             | Fig.No.          |

| Circuit | Diagram: | AF Board PM662 | 7.1 |

|---------|----------|----------------|-----|

| Layout: | AF Board | PM662          | 7.2 |

## CHAPTER 7

## AF BOARD PM662

#### INTRODUCTION

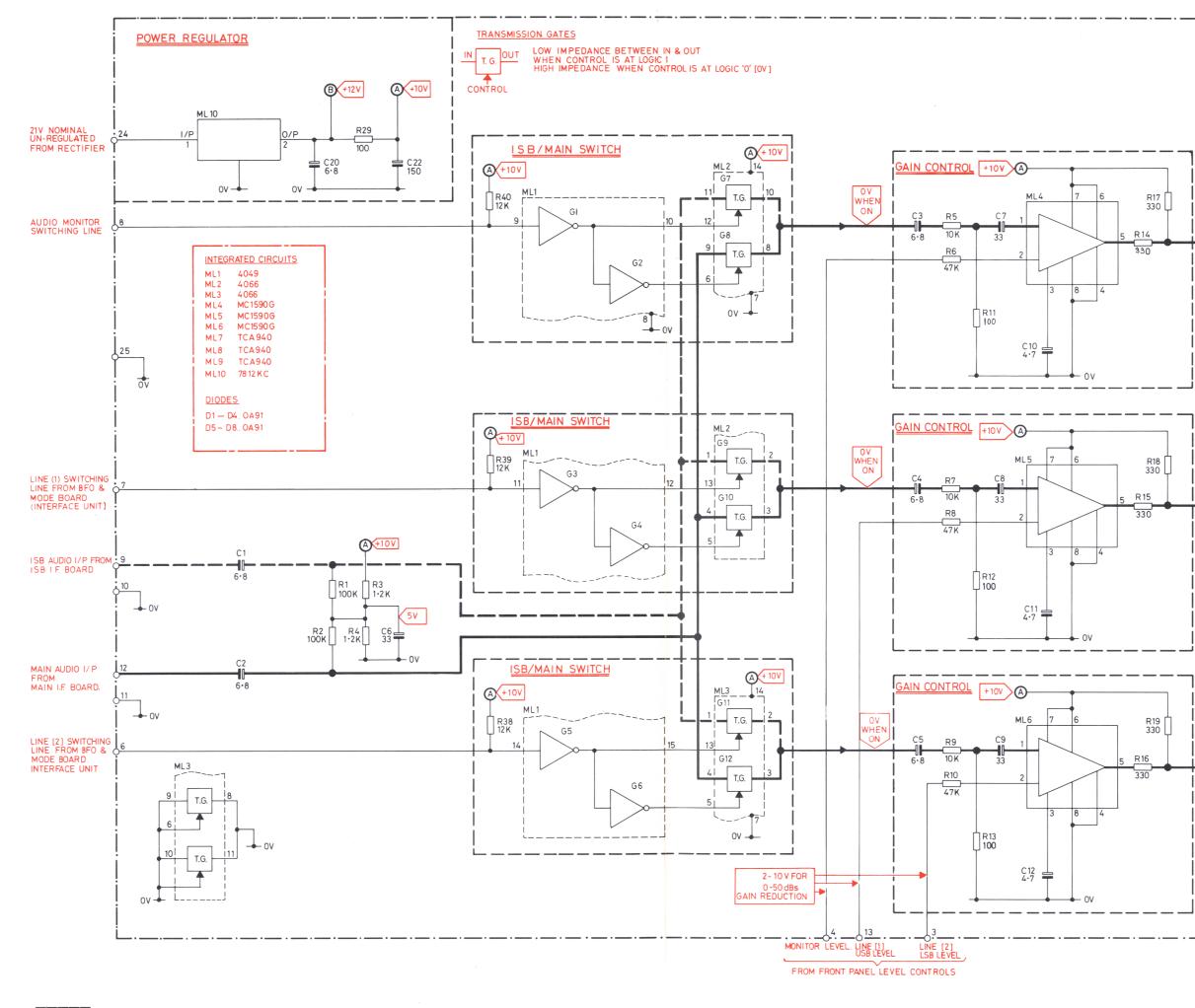

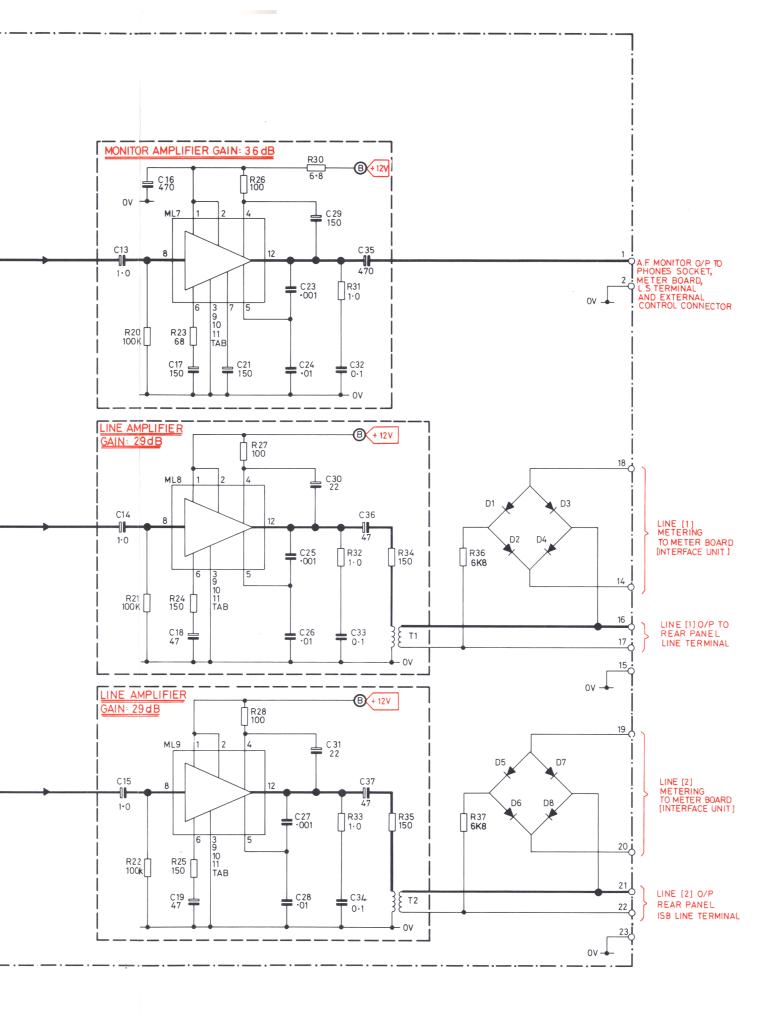

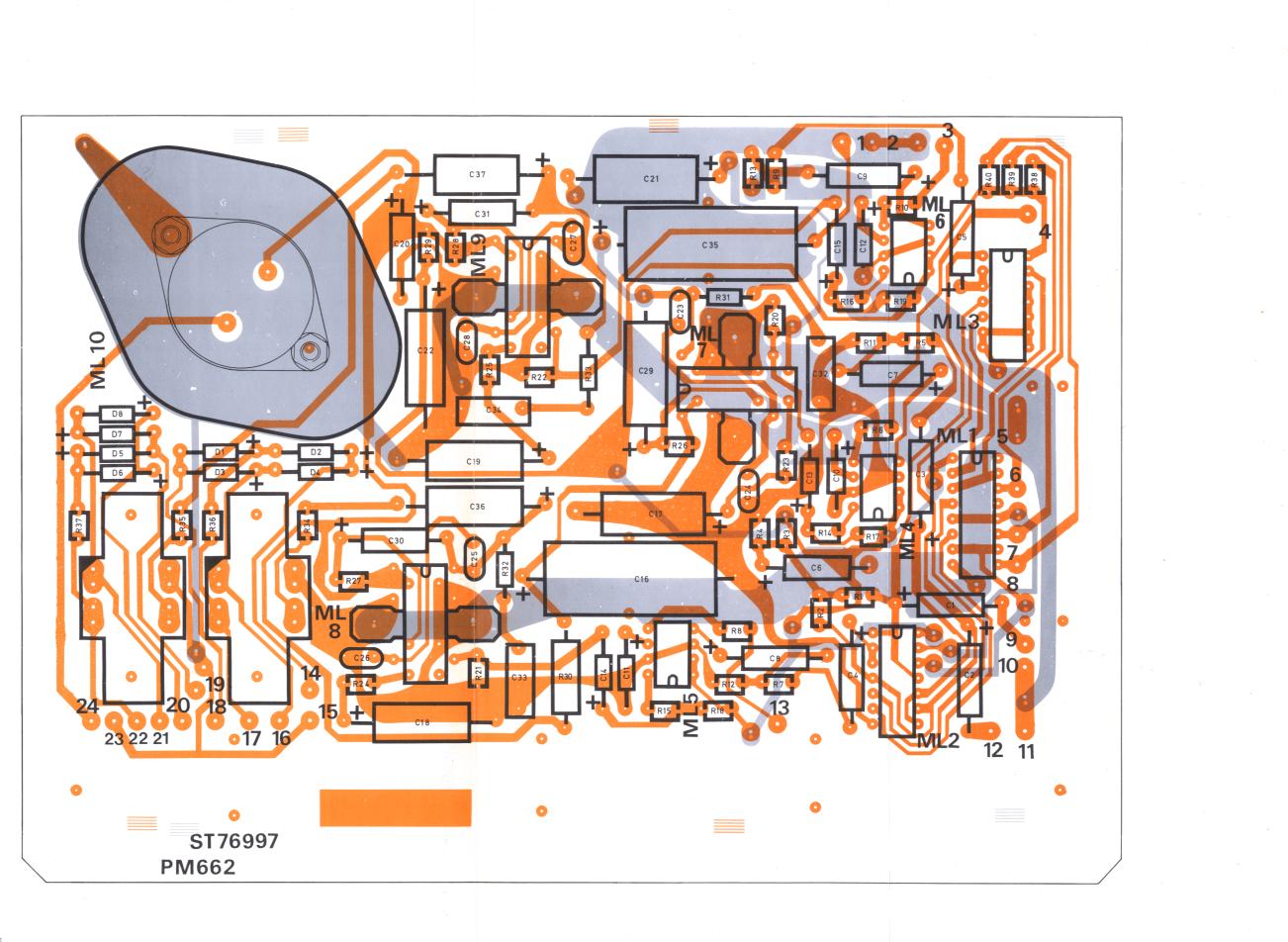

This board contains three audio amplifiers; one supplies the audio monitor output to the phones socket, the rear panel loudspeaker terminals, the rear panel external control connector, and to the front panel meter via the interface unit, whilst the remaining two amplifiers provide the audio line output signals (line output and ISB line output terminals) together with rectified outputs for metering purposes.

2. The audio input switching, which is controlled by the serial data from the control panel via the interface unit, is arranged such that for SSB receivers (or ISB receivers switched to SSB) the audio output signal from the main IF board is applied to all three audio amplifiers, whilst for ISB receivers (set for ISB operation) one line amplifier is fed from the main IF board and the other line amplifier is fed from the ISB IF board. The input signal to the audio monitor amplifier is fed from the main IF board when ISB-U is selected, or from the ISB IF board when ISB-L is selected at the control panel.

3. The circuit diagram of the AF board is given in fig. 7.1.

#### AUDIO INPUT SWITCHING

4. The audio input switching is controlled by the MODE push-button switches on the control panel via the serial control data and the interface unit (BFO and mode board). Transmission gates (G7 to G12) are used as the switch elements and these are controlled by the logic levels on the three switching lines, at board pins 8, 7 and 6. For example, if a '0' is applied to board pin 8, the resulting '1' output from the inverting buffer G1 opens transmission gate G7 for the audio output signal from the ISB IF board, at board pin 9. When the '0' is removed from board pin 8, a '1' is applied to the input of G1 (from the +10V supply via R40) and the resulting '1' output from G2 opens transmission gate G8 for the audio output signal from the main IF board, at board pin 12.

5. Details of the audio switching arrangements for all modes for both SSB and ISB versions of the receiver are given in table 1.

### GAIN-CONTROLLED AMPLIFIERS

6. The three gain-controlled amplifiers are of similar construction and each use highgain wideband amplifier integrated circuit ML4, ML5, ML6. The gain-control voltage applied to pin 2 is set by the respective level control on the receiver front panel (MONITOR LEVEL, USB LINE LEVEL and LSB LINE LEVEL controls).

|               | AUDIO MO<br>AMPLI |                | LINE 1 AMPLIFIER |                | LINE 2 AMPLIFIER |                |

|---------------|-------------------|----------------|------------------|----------------|------------------|----------------|

| MODE          | INPUT<br>SOURCE   | PIN 8<br>LEVEL | INPUT<br>SOURCE  | PIN 7<br>LEVEL | INPUT<br>SOURCE  | PIN 6<br>Level |

| SSB RECEIVERS |                   |                |                  |                |                  |                |

| ALL MODES     | MAIN IF           | ١              | MAIN IF          | 1              | MAIN IF          | 1              |

| ISB RECEIVERS |                   |                |                  |                |                  |                |

| LSB           | ISB IF            | 0              | ISB IF           | 0              | ISB IF           | 0              |

| ISB-U         | MAIN IF           | 1              | MAIN IF          | 1              | ISB IF           | 0              |

| ISB-L         | ISB IF            | 0              | MAIN IF          | 1              | ISB IF           | 0              |

| OTHER MODES   | MAIN IF           | 1              | main if          | ٦              | main if          | 1              |

Table 1: Audio Input Switching

#### AF OUTPUT AMPLIFIERS

7. The audio monitor output amplifier, ML7, has a fixed gain of approximately 36 dB. The output from ML7, which is short-circuit protected, is coupled by C35 to the front panel PHONES socket, the loudspeaker terminals and the external control connector on the rear panel, and to the front panel meter via the meter board (part of the interface unit – Part 4).

The two line output amplifiers ML8, ML9 are similar and have a gain figure of approximately 29 dB. The output signals are transformer coupled to the rear panel LINE O/P and ISB LINE terminals, and are also applied via bridge rectifier circuits D1 to D4 and D5 to D8, to the front panel meter via the meter board (part of the interface unit).

| 1 | RACAL    |         |       |          |          |       |

|---|----------|---------|-------|----------|----------|-------|

|   | WOH 6247 | DC76997 | 3/7.1 | WOH 6247 | DC 76997 | 3/7.1 |

|   | 2 3      |         | 1/2   | 2        |          | 2/2   |

Circuit: AF Board PM662 Part 3 Fig 7.1

Layout: Audio Frequency Board

# PART 4

INTERFACE UNIT MS614

#### CONTENTS

- CHAPTER 1 GENERAL DESCRIPTION

- CHAPTER 2 DISMANTLING AND REASSEMBLY

- CHAPTER 3 FUNCTIONAL DESCRIPTION

- CHAPTER 4 SERIAL CONTROLLER BOARD PS667

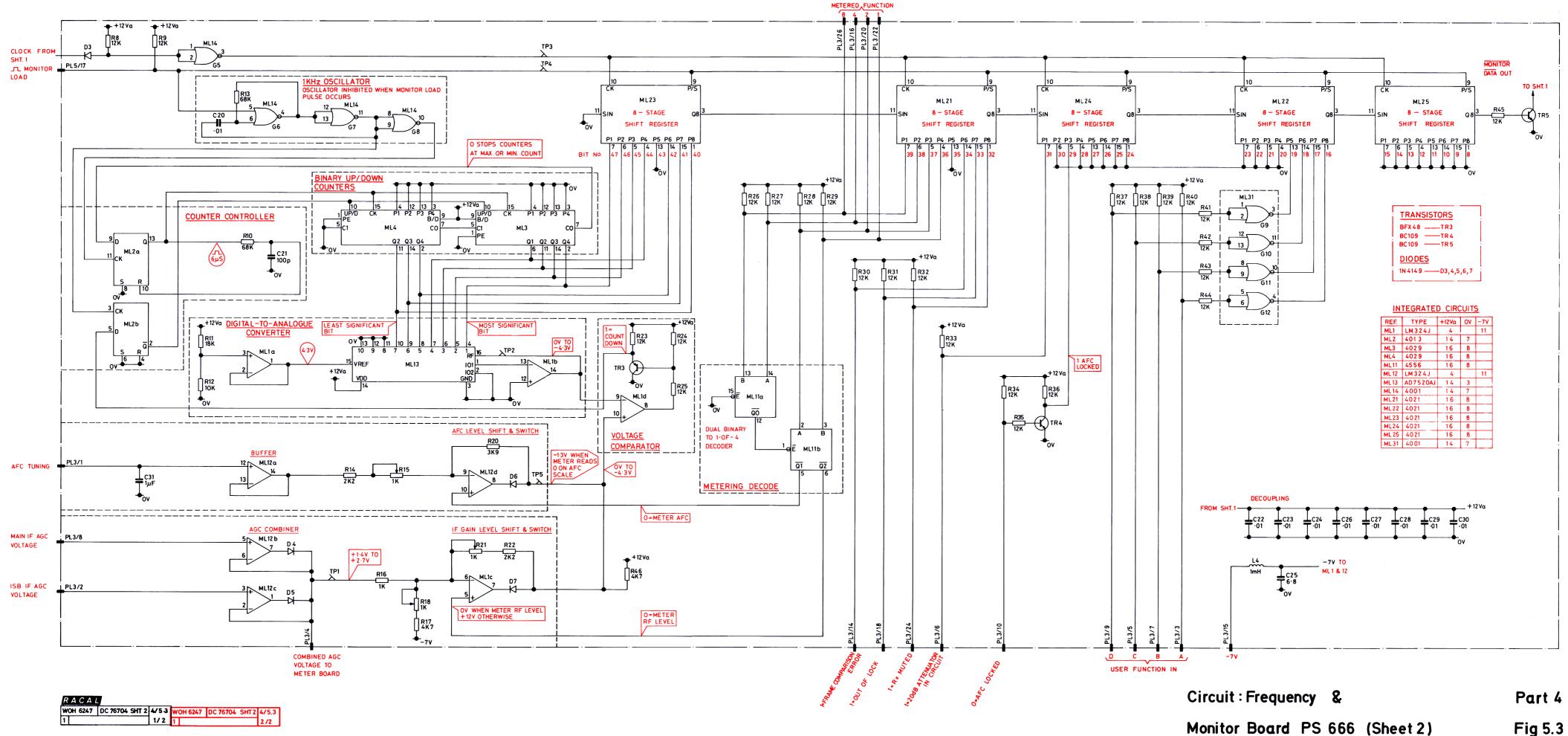

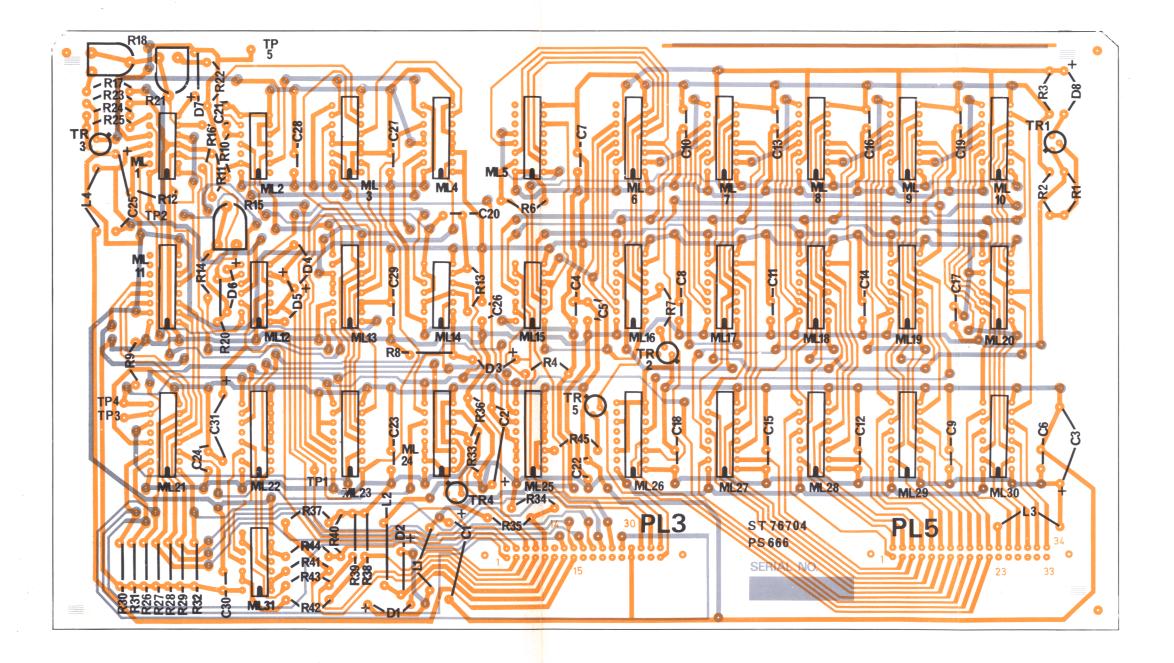

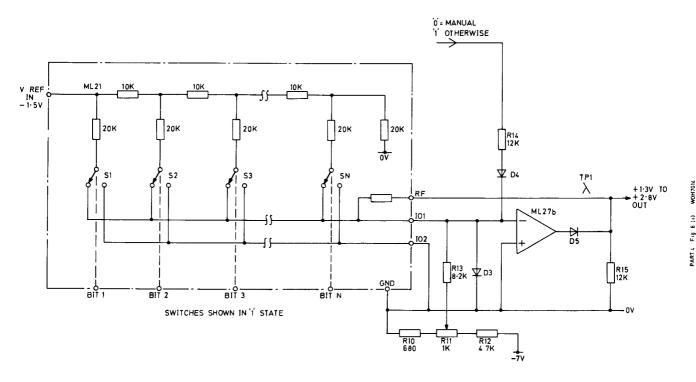

- CHAPTER 5 FREQUENCY AND MONITOR BOARD PS666

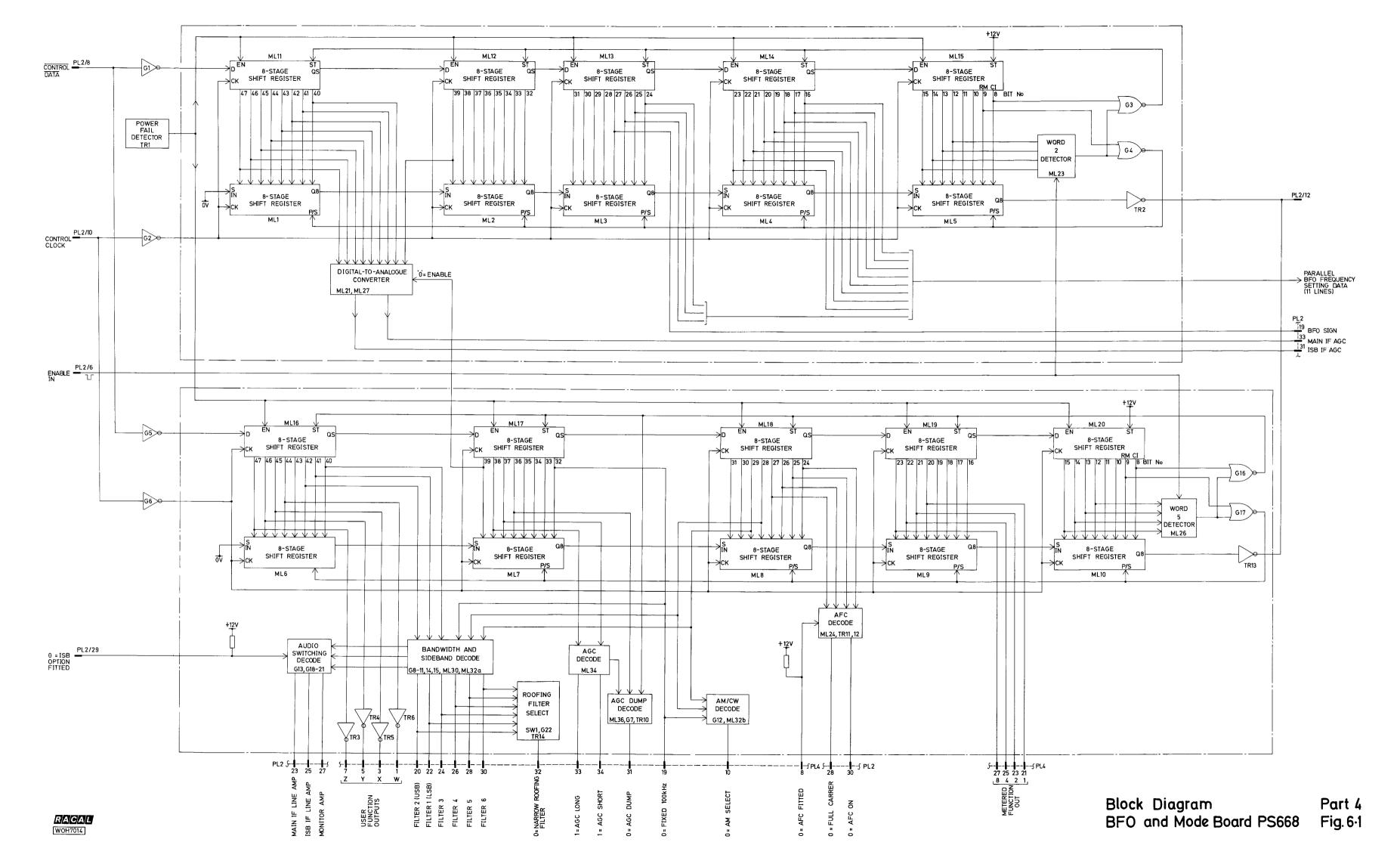

- CHAPTER 6 BFO AND MODE BOARD PS668

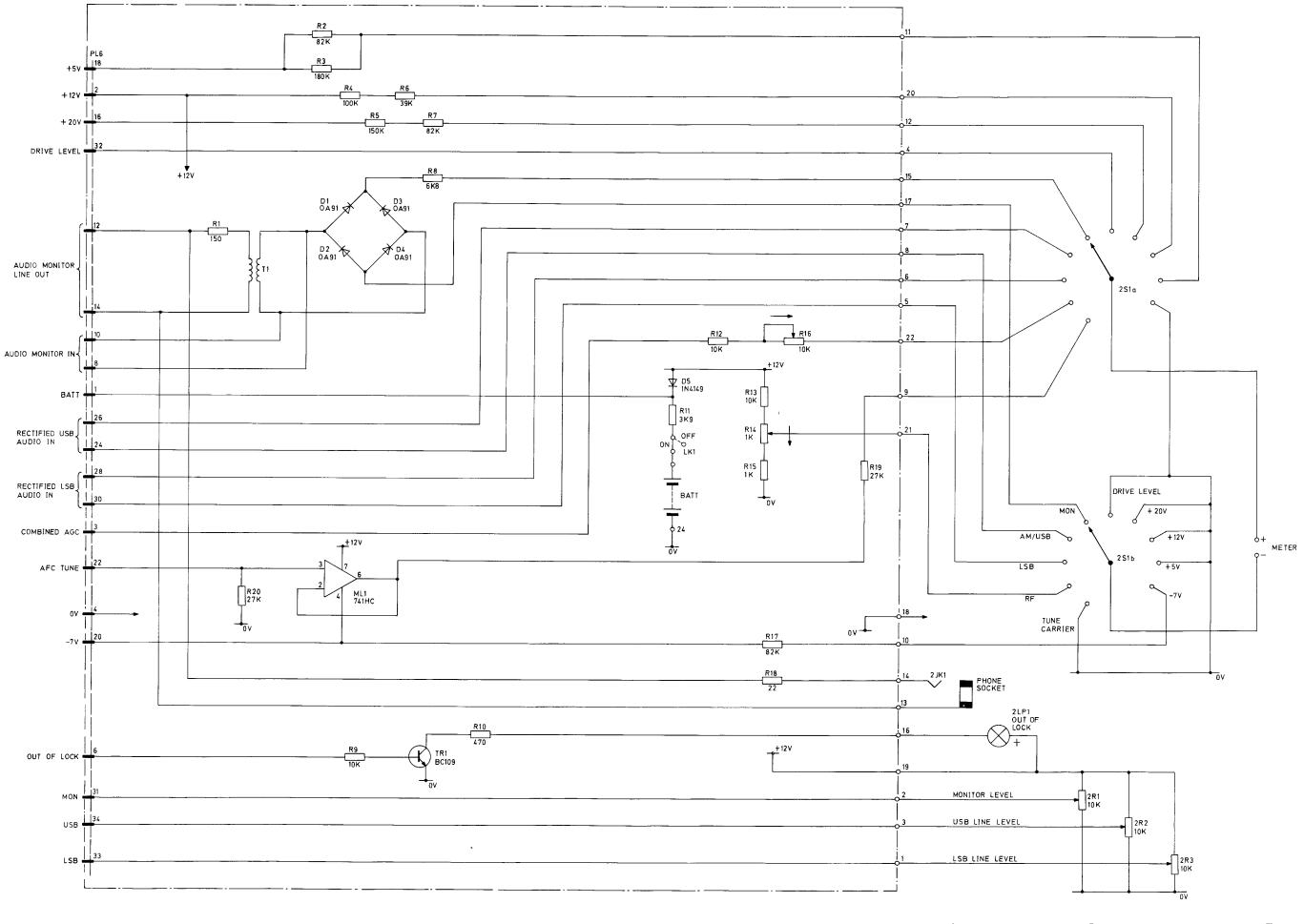

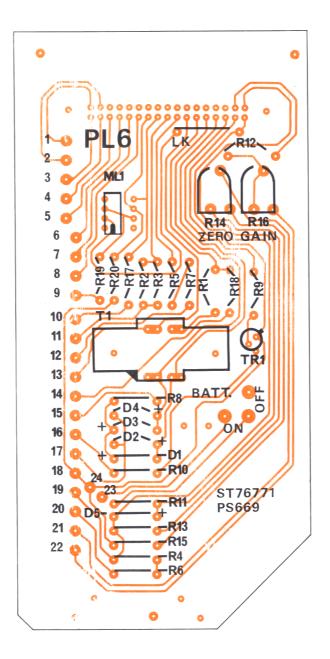

CHAPTER 7 METER SWITCHING/STANDBY BATTERY BOARD PS669

## <u>CHAPIER\_1</u>

## GENERAL DESCRIPTION

### CONTENTS

|                                                | Para.    |

|------------------------------------------------|----------|

| INTRODUCTION<br>BRIEF TECHNICAL DESCRIPTION    | 1<br>2   |

| PHYSICAL DESCRIPTION                           | 6        |

| ILLUSTRATIONS                                  |          |

|                                                | Fig. No. |

| Simplified Block Diagram: MS614 Interface Unit | 1.1      |

Part 4 Chap.1 Contents

.

## <u>CHAPIER 1</u>

## GENERAL DESCRIPTION

#### INTRODUCTION

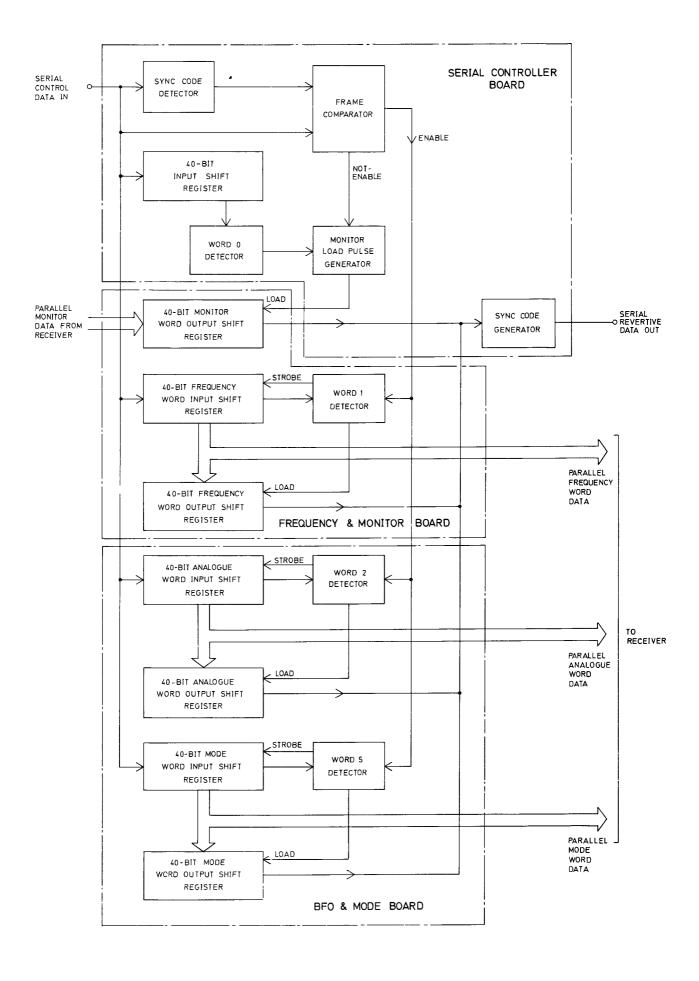

1. The MS614 interface unit converts the serial control data from the MA.1072 into parallel form to control the various receiver functions, and also generates the serial revertive data which is sent back to the MA.1072 control panel. A simplified block diagram of the unit is given in fig. 1.1.

#### BRIEF TECHNICAL DESCRIPTION

The serial control data from the MA.1072 is applied in parallel to the sync. code detector, frame comparator and 40-bit input shift register on the serial controller card, and to the 40-bit shift registers for the frequency word, the analogue word and the mode word. When a correct sync. code is recognised, the frame comparison takes place; if successful, an enable pulse is generated which is applied to the word ident. detectors for words 1 (frequency), 2 (analogue) and 5 (mode) via a common enable line.

3. For word 1, word 2 or word 5 data, the strobe output signal from the respective word detector enables the parallel output data from the associated 40-bit input shift register (which is applied to the receiver); a second output signal from the respective word detector loads the parallel data into the associated output shift register, and this is then serially clocked out as revertive data for application to the MA.1072 control panel via a sync. code generator.

4. For word 0 data, or should the frame comparison fail, a monitor load pulse is generated (either by the output from the word 0 detector or by the not-enable output from the frame comparator); the parallel monitor data from the receiver is loaded into the 40-bit monitor word output shift register and is then serially clocked out via the sync. code generator to the MA.1072.

5. A meter and associated switch on the front panel are provided for monitoring power supply and other signal levels from the receiver. These signals are applied to the meter switch via the meter switching/standby battery board. The standby battery is used to preserve the frequency setting and other data during a supply failure.

### PHYSICAL DESCRIPTION

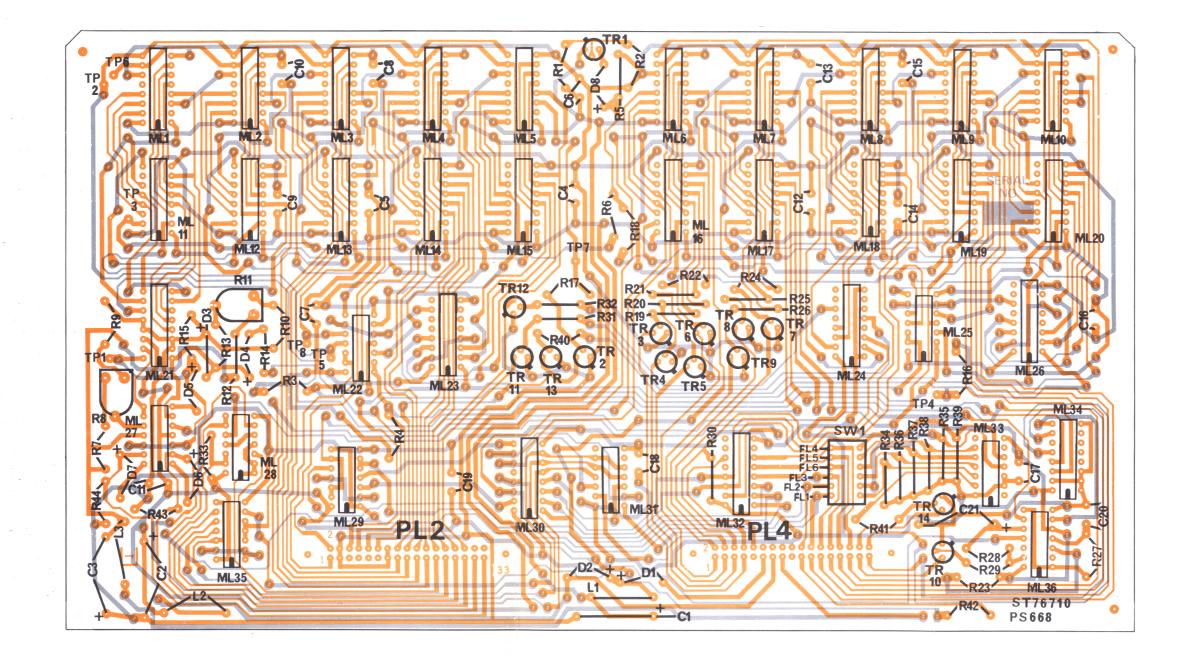

6. The interface unit comprises a metal box structure which is attached to the receiver front panel. The three main printed circuit boards (serial controller, frequency and monitor, and BFO and mode) are mounted one behind the other in spring-loaded slides. The meter switching/standby battery board is also mounted in spring-loaded slides and is positioned behind the front panel meter. The connections to the boards are made via flexible ribbon cable and connector assemblies from an interconnection board which is attached to the inner

rear face of the box structure. Four multi-way connectors are mounted on the interconnection board and these protrude through apertures in the rear member of the box structure for the mating connections from the receiver (one connector is wired to the external control connector on the receiver rear panel).

7. A cableform from the meter switching/standby battery board connects with the front panel meter switch, PHONES socket, the OUT OF LOCK lamp, and the three audio level adjustment potentiometers. A separate five-way connector on the rear member of the box structure is used for the supply connections to and from the front panel POWER switch and associated indicator lamp.

Simplified Block Diagram MS614 Interface Unit Part 4 Fig.1-1

## <u>CHAPTER 2</u>

## DISMANTLING AND REASSEMBLY

#### CONTENTS

|                                 | Para. |

|---------------------------------|-------|

| INTRODUCTION                    | 1     |

| REMOVAL OF INTERFACE UNIT       | 2     |

| ACCESS TO METER SWITCHING BOARD | 3     |

| Battery Link                    | 5     |

| MAIN COMPARTMENT BOARDS         | 6     |

| FRONT PANEL REMOVAL             | 8     |

| INTERCONNECTION BOARD REMOVAL   | 9     |

| BATTERY REMOVAL                 | 10    |

### ILLUSTRATIONS

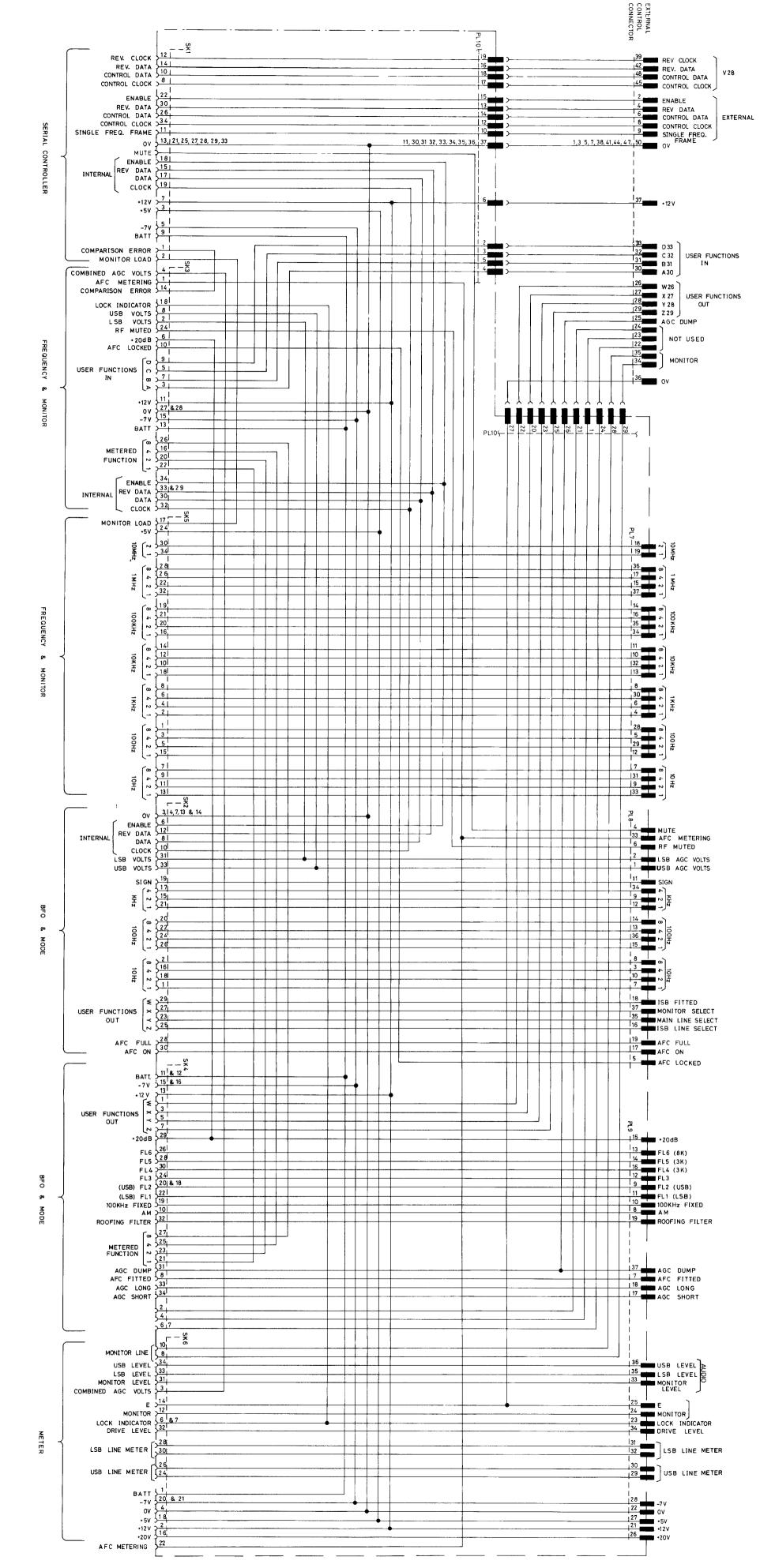

Interconnection Diagram: MS614 Interface Unit

Part 4 Chap.2 Contents

Fig. No. 2.1

٢

#### 'POZIDRIV' SCREWDRIVERS

Metric thread cross-head screws fitted to Racal equipment are of the 'Pozidriv' type. Phillips type and 'Pozidriv' type screwdrivers are <u>not</u> interchangeable, and the use of the wrong screwdriver will cause damage. POZIDRIV is a registered trade mark of G.K.N. Screws and Fasteners Limited. The 'Pozidriv' screwdrivers are manufactured by Stanley Tools Limited.

## <u>CHAPIER\_2</u>

## DISMANTLING AND REASSEMBLY

#### INTRODUCTION

1. This chapter provides instructions for gaining access to the printed circuit boards and chassis components of the MS614 interface unit. The dismantling and reassembly instructions for the remainder of the receiver are given in Part 1, Chap.2. In general, the reassembly is the reverse of the dismantling procedure.

#### REMOVAL OF INTERFACE UNIT

- 2. The interface unit, which includes the receiver front panel, is removed from the receiver as follows:

- 3. (1) Slide the receiver forwards such that the bottom edge of the front panel is clear of the working surface.

- (2) Remove the four chromed front panel screws adjacent to each handle, three fitted with a nylon washer and one recessed, fitted with a spring washer.

- (3) Grip the two handles, slide the unit forwards sufficiently to allow the removal of the five connecting sockets, and then slide the unit forwards to clear the receiver side members.

NOTE: When reconnecting the interface unit to the receiver chassis ensure that the three right-hand multi-way connectors are correctly located by matching the coloured spots on the cable form connector shells with those adjacent to the interface unit plugs. These plugs are numbered, from the top, as PL7, PL8 and PL9; the five-way plug is PL11 and the left hand multi-way plug is PL10.

#### ACCESS TO METER SWITCHING BOARD

- 4. (1) Remove the ribbon connector (brown spot) from the top edge of the meter switching board.

- (2) Slide the board upwards to clear the guide slots. The board is connected via a cableform which has sufficient slack to allow the reconnection of the ribbon connector for maintenance purposes. Before applying power to the receiver insulate the underside of the board.

#### Battery Link

5. The two position link on the meter switching board may be set to the BATTERY OFF position to completely remove all power from the receiver.

#### MAIN COMPARTMENT BOARDS

6. The main compartment boards, namely, from front to rear, the serial controller board PS667, the BFO and mode board PS668, and the frequency and monitor board PS666, are held in slides in the main compartment. Electrical connections are made via ribbon cable and connector assemblies (from the interconnection board) which are colour coded for ease of identification. The coloured dots on the inside of the left-hand compartment side member match those of the left-hand connector on each board to indicate correct positioning.

7. To remove a board, disconnect the ribbon cable connectors from all of the boards and slide the board upwards.

#### FRONT PANEL REMOVAL

- 8. (1) Remove the end cap from the METER switch knob.

- (2) Using an 8 mm ring or socket spanner, release the knob collet nut and remove the knob.

- (3) Remove the three screws, each with a nylon washer, from the centre of the front panel.

- (4) The front panel is now attached only by the two leads to the front panel meter. To completely remove the front panel undo the nuts securing these leads to the meter. Replace the nuts for safe keeping.

#### INTERCONNECTION BOARD REMOVAL

- 9. (1) Remove the three boards from the main compartment (para. 6).

- (2) Disconnect the ribbon cable connector from the meter switching board.

- (3) Remove the seven screws securing the rear plate, three at each side and one in the centre of the flange securing the rear plate to the base plate.

- (4) Remove the locking posts securing the four multi-way connectors to the rear plate.

- (5) Ease off the board from the push-fit nylon stand-off fasteners.

#### BATTERY REMOVAL

- 10. (1) Ensure that the battery link on the meter switching board is set to BATTERY OFF.

- (2) Remove the rear plate (steps (1), (2) and (3) of para. 9).

- (3) Unsolder the battery leads and remove the battery from the two spring clips.

R A C A L WOH6247 DC 77190

Part 4

| R A | ACAL    |           |       |

|-----|---------|-----------|-------|

| WC  | 0H 7014 | DA77099/3 | 4/2.2 |

| 1   |         |           | 1/2   |

| WC  | OH 7014 | DA77099/2 | 4/2.2 |

| 1.  |         |           | 2/2   |

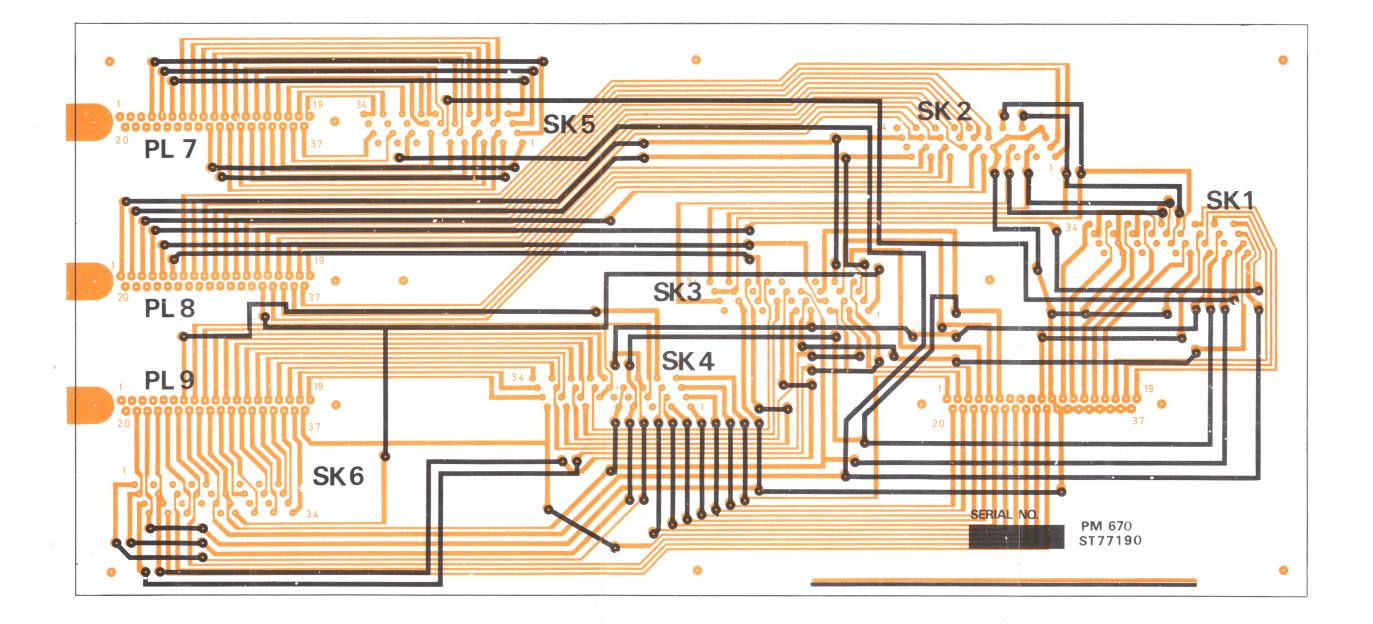

Part 4 Layout: Interconnection Board Fig. 2·2

## <u>CHAPIER\_3</u>

## FUNCTIONAL DESCRIPTION

### CONTENTS

|                     | Para |

|---------------------|------|

| INTRODUCTION        | 1    |

| SYNCHRONISATION     | 2    |

| SERIAL DATA ROUTING | 3    |

| CONTROL INHIBIT     | 12   |

| RETURN MONITOR      | 13   |

|                     |      |

|                     |      |

### ILLUSTRATIONS

|                                          | Fig. No. |

|------------------------------------------|----------|

| Functional Diagram: MS614 Interface Unit | 3.1      |

Part 4 Chap.3 Contents

## <u>CHAPIER 3</u>

## FUNCTIONAL DESCRIPTION

#### INTRODUCTION

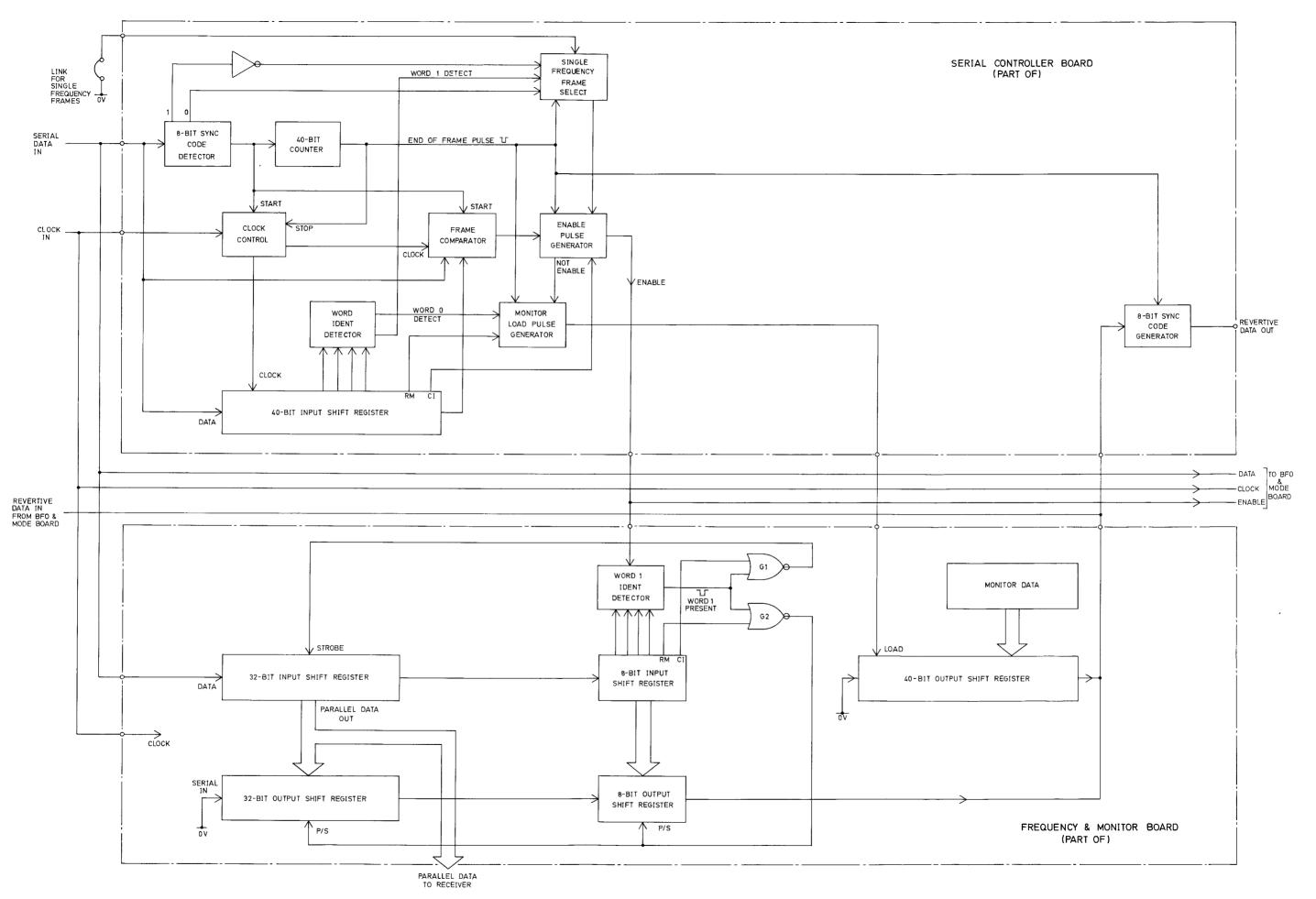

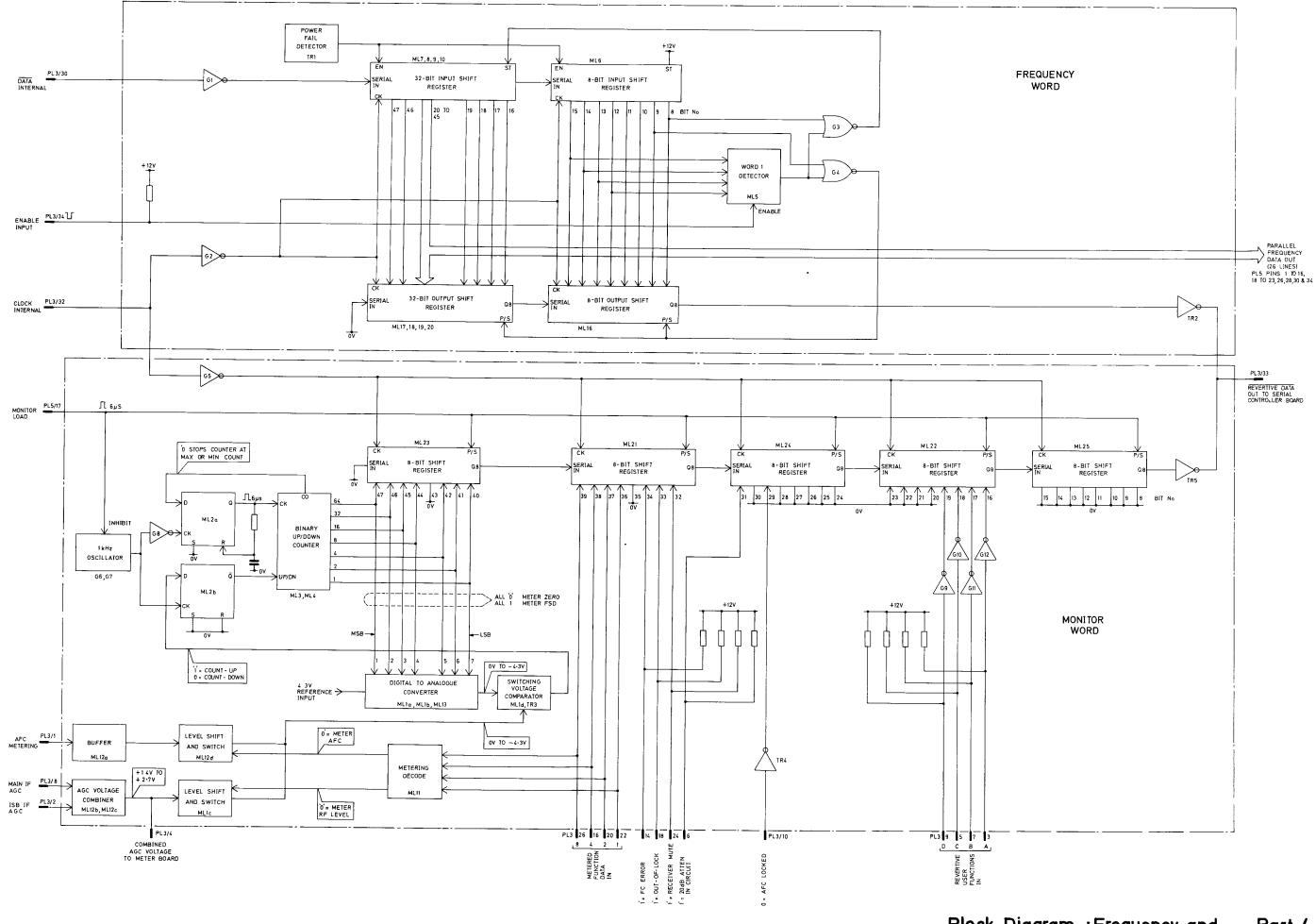

This chapter briefly describes the operation of the interface unit, and should be read in conjunction with the functional diagram given in fig. 3.1. This diagram shows the basic blocks for the monitor word (word 0) and the frequency word (word 1) to illustrate the principles of operation; the same principles however, apply for the remaining words.

#### SYNCHRONISATION

2. The serial data and clock signals from the MA.1072 control panel are applied simultaneously to the frequency and monitor board, the BFO and mode board, and to the serial controller board. When a correct sync. code (a '0' followed by five '1s') is recognised by the sync. code detector on the serial controller board, a start signal is generated which is applied to:

- (1) A 40-bit counter which eventually generates an end-of-frame pulse.

- (2) A frame comparator which compares the next 40-bits of the incoming serial data with the contents of a 40-bit input shift register.

- (3) A clock control circuit which allows the application of 40 clock pulses to the frame comparator and to the 40-bit input shift register.

Thus when the end-of-frame pulse is generated, it signifies that a correct sync. code has been received and that the remaining 40-bits of the data word frame are correctly positioned in the input shift registers on the serial controller, frequency and monitor, and BFO and mode boards.

#### SERIAL DATA ROUTING

3. For the purposes of the following description, assume that the incoming serial data consists of two word 0 frames followed by two word 1 frames and then two word 5 frames. Assume also that the control inhibit bit (CHECK status) is not set (para. 12) and that the return monitor bit (single frequency frames) is not set (para. 13).

4. Word 0 is used for revertive monitor purposes only; it is sent by the MA.1072 as a routine data word to request the return of the monitor information. Since the monitor word frame is also returned following a frame comparison failure (see MA.1072 Maintenance Manual, Chap.2), it follows that every time a word 0 frame is received, a word 0 frame must be returned. Thus every time the word ident. detector detects the presence of word 0 in the 40-bit input shift register on the serial controller board, a monitor load pulse is generated by the combination of the word 0 detect output signal and the end-of-frame pulse.

The monitor load pulse is applied to the 40-bit monitor output shift register (frequency and monitor board), and the monitor data is loaded in.

5. The sync. code of the second word 0 frame is recognised by the 8-bit sync. code detector, the 40-bit counter is restarted, and the remaining 40 bits of the second word 0 frame are clocked into the 40-bit input shift register. At the same time, the monitor word is clocked out of the 40-bit output shift register, via a further shift register (serial controller board) which adds the 8-bit sync. code, and the complete word 0 frame is sent back to the MA.1072 control panel via the revertive data line.

6. The word ident. detector again detects the presence of word 0 in the 40-bit input shift register, a further monitor load pulse is generated as before, and the monitor data is loaded into the 40-bit output shift register.

7. The next frame received in this example contains word 1 which, following sync. code detection, is frame compared with word 0 (contained in the 40-bit input shift register). Since the two frames do not compare, a monitor load pulse is again generated, only this time by the combination of the frame comparator output, the resulting not-enable output, and the end-of-frame pulse. The second monitor word frame is clocked out to the MA.1072 and the monitor data is loaded into the 40-bit output shift register for the third successive time.

8. The next frame comparison (following sync. code detection) is between two word 1 frames; this time (assuming no bit errors are detected), the combination of the frame comparator output and the end-of-frame pulse results in the generation of an enable pulse which is applied via a common line to the word 1 ident. detector on the frequency and monitor board and the word 2 and word 5 ident. detectors on the BFO and mode board. The presence of word 1 in the frequency word input shift register (32-bit register followed by an 8-bit register) is detected, a strobe pulse is applied via NOR gate G1 (the control inhibit input is at '0') and the 32-bit frequency data word is applied in parallel form to both the 32-bit section of the frequency word output shift register and the synthesizer section of the receiver. The word 1 ident. detector also routes a parallel-entry pulse to the frequency word output shift register via NOR gate G2 (the return monitor bit is set to '0') and the 40 bits of the frequency word are loaded in. During this time, the third word 0 frame is clocked out as revertive data to the MA.1072 control panel.

9. The next data frame in the sequence contains word 5 (para. 3). Since this will not frame compare with word 1, a monitor load pulse is generated (frame comparator output and resultant not-enable pulse together with the end-of-frame pulse) and the monitor data is loaded into the monitor word 40-bit output shift register. At the same time, the frequency word is clocked out via the 8-bit sync. code generator to the MA.1072.

10. The last frame in this example sequence also contains word 5. This results in the generation of the enable pulse (assuming no bit errors are detected), the word 5 ident. detector on the BFO and mode board causes the mode word to be entered into the mode word output shift register, and this is clocked out via the 8-bit sync. code generator, following the transmission of the previously generated monitor word frame.

11. If the two word 5 frames do not compare, a monitor load pulse is generated (combination of the frame comparator output, the not-enable pulse and the end-of-frame pulse) and a monitor word frame is returned to the MA.1072.

#### CONTROL INHIBIT

12. The control inhibit bit (bit 8 of the SCORE format) is set to a '1' at the MA.1072 when the CHECK status is selected. The control inhibit bit output from the 40-bit input shift register on the serial controller board causes the generation of the enable pulse (the frame comparator is by-passed), whilst the control inhibit bit outputs from the control word input shift registers prevent strobe pulse generation, i.e. the output from G1 is forced to a '0' and similarly for the remaining control words. The absence of the strobe pulse prevents the updating of the parallel output data (the parallel outputs of the data word input shift registers are latched) and thus further control of the receiver is inhibited. Since routine data only is received in the CHECK status, and since no frame comparison takes place, the control word ident. detectors cause the receiver setting information to be returned to the MA.1072 in sequential double frames which lag the forward data by one frame (48 bits).

#### **RETURN MONITOR**

13. The return monitor bit (bit 9 of the SCORE format) is set to a '1' at the MA.1072, together with a '0-1' code for the single-frame check bits (bits 46 and 47) of the frequency word, when single frequency word frames are required together with continuous revertive monitor. To allow the transfer of single frequency frames two connections are required, one at the MA.1072 and one at the RA.1784. A link is required between pins 17 and 11 (earth) at PL1 on the MA.1072 for the transmission of single frequency frames when free tuning, and a link is required between pins 9 and 7 (earth) at the external control connector on the RA.1784 rear panel to inhibit frame comparison on frequency frames. Note that the frequency frames are only sent singly whilst new frequency data is being generated; once the required frequency has been set, routine frequency frames are sent in pairs and frame comparison is restored at the RA.1784.

14. The link between pins 9 and 7 at the external control connector on the receiver rear panel routes a '0' to the single frequency frame select circuit on the serial controller board. To inhibit frame comparison on frequency frames, the remaining inputs to this circuit must all be at '0' when the end-of-frame pulse is generated; the output from the word ident. detector will pulse to '0' when the presence of word 1 in the 40-bit input shift register is detected, whilst the other two inputs are derived from the single frame check bits of the frequency word. When the last 40 bits of the frequency word are correctly positioned in the 40-bit input shift register, bits 40 to 47 will also be located in the 8-bit sync. code detector. The '0' code for bit 46 and the inverted '1' code for bit 47 are thus applied to the single frequency frame select circuit, the enable pulse is generated, and the frame comparator is effectively by-passed.

15. The return monitor bit output from the 40-bit input shift register on the serial controller board is applied to the monitor load pulse generator and the resulting load pulse enters the monitor data into the 40-bit monitor output shift register. The return

monitor bit output from the frequency word input shift register is applied via NOR gate G2 as a serial-entry signal to the frequency word output shift register to inhibit parallel data entry.

16. When tuning ceases at the MA.1072, routine data double frequency frames are transmitted, the single frame check bits of the frequency words are both set to '0', and thus frame comparison is restored.

4

•

# CHAPTER 4

# SERIAL CONTROLLER BOARD PS667

#### CONTENTS

|                                          | Para.        |

|------------------------------------------|--------------|

| INTRODUCTION                             | 1            |

| FUNCTIONAL DESCRIPTION                   |              |

| Control Data Input                       | 2            |

| Control Clock Input                      | 2<br>3<br>3A |

| Clock Pulse Generator                    | 3A           |

| Sync. Code Detector                      | 4            |

| PTT/Mute Circuit                         | 4<br>6<br>8  |

| Counter and Control                      |              |

| 40-bit Input Shift Register              | 10           |

| Frame Comparator                         | 14           |

| Error Counter                            | 16           |

| Sync. Code Generator                     | 18           |

| Return Monitor                           | 20           |

| CIRCUIT DESCRIPTION                      |              |

| Control Data Input                       | 22           |

| Control Clock Input (Standard Version)   | 23           |

| Control Clock Input (Modified Version)   | 23A          |

| Clock Pulse Generator (Standard Version) | 24           |

| Clock Pulse Generator (Modified Version) | 24A          |

| Sync. Code Detector                      | 25           |

| Power Fail Detector                      | 28           |

| 40-Bit Counter and Control               | 29           |

| Muting                                   | 32           |

| 40-Bit Input Shift Register              | 35           |

| Word Detector                            | 37           |

| Frame Comparator                         | 40           |

| Monitor Load Pulse Generator             | 41           |

| Enable Pulse Generator                   | 44           |

| Error Counter                            | 49           |

| Sync. Code Generator                     | 50           |

#### TABLES

| Table No. |                                      | Page |

|-----------|--------------------------------------|------|

| 1         | Binary to 1-of-4 Decoder Truth Table | 4-8  |

RA.1784 Maintenance

#### ILLUSTRATIONS

#### Fig.No.

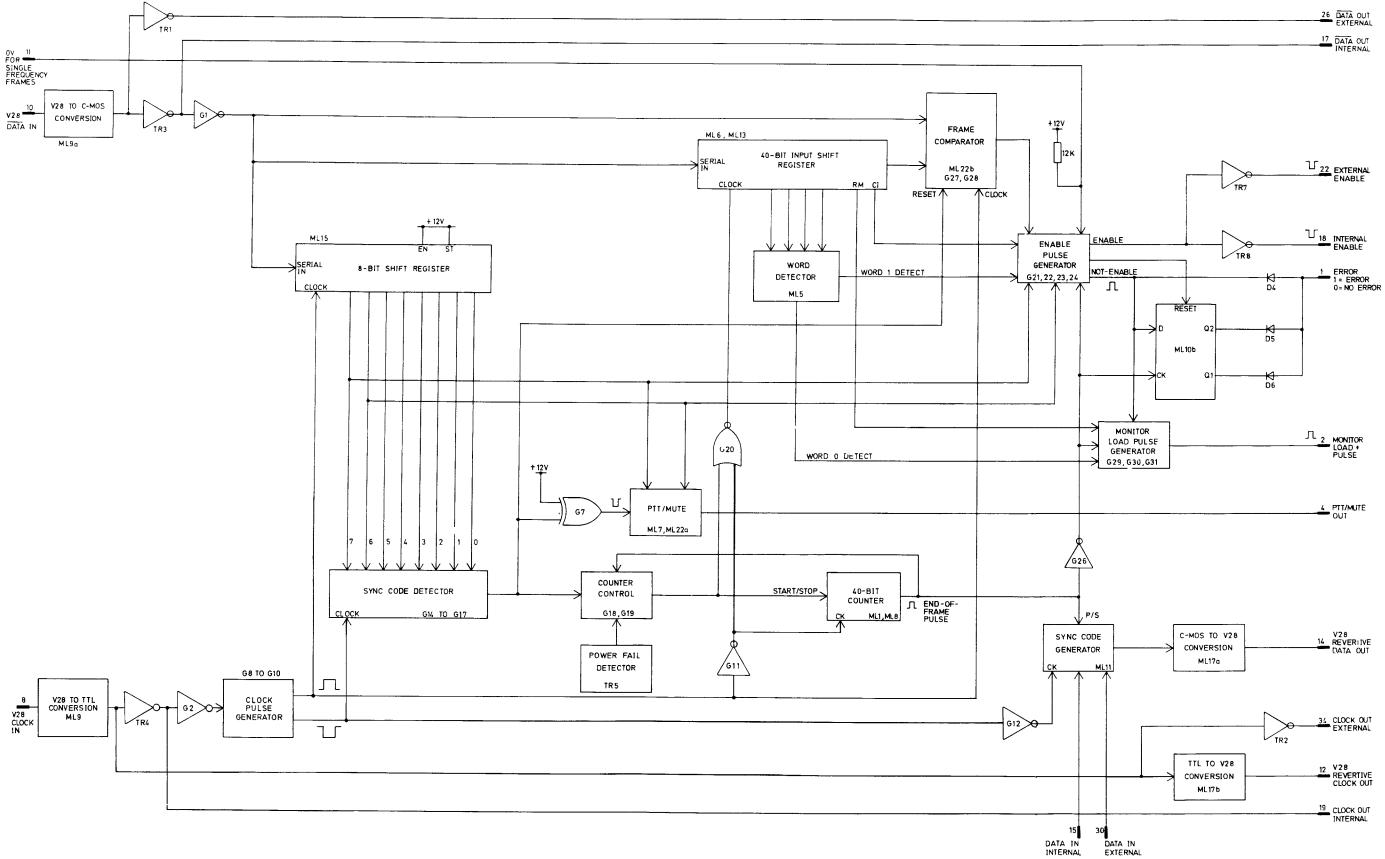

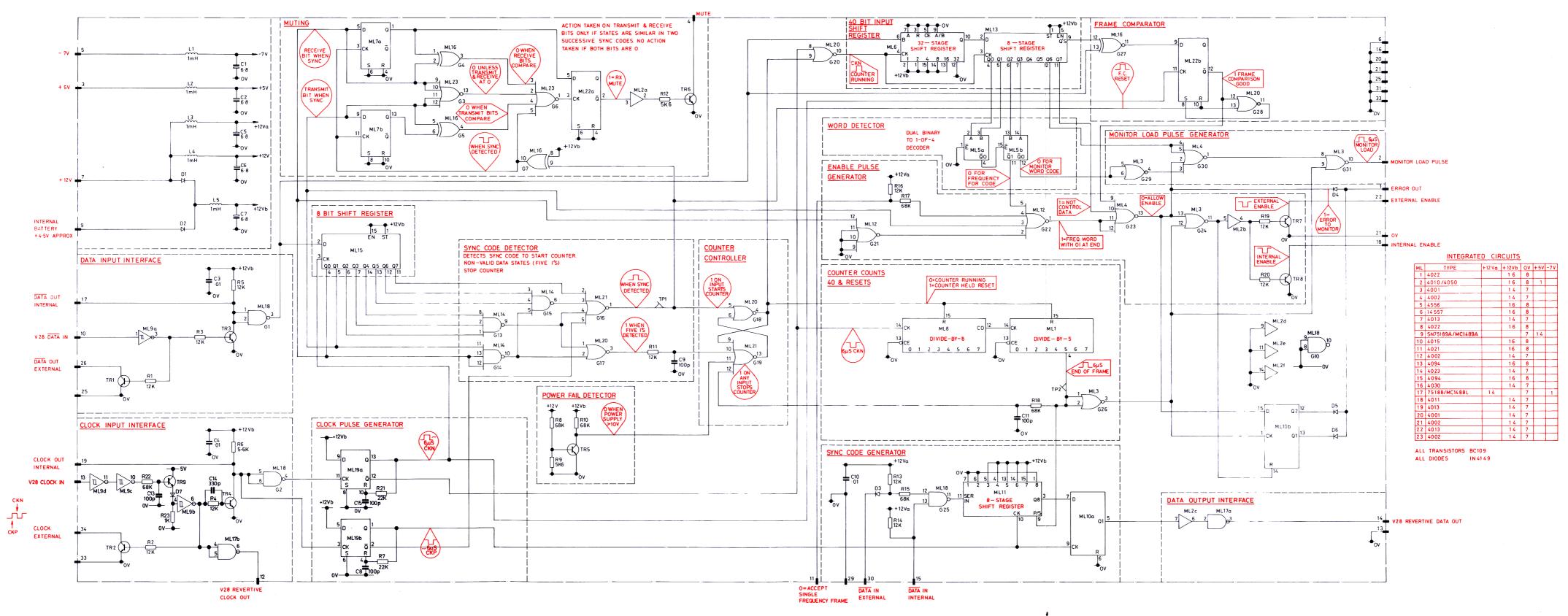

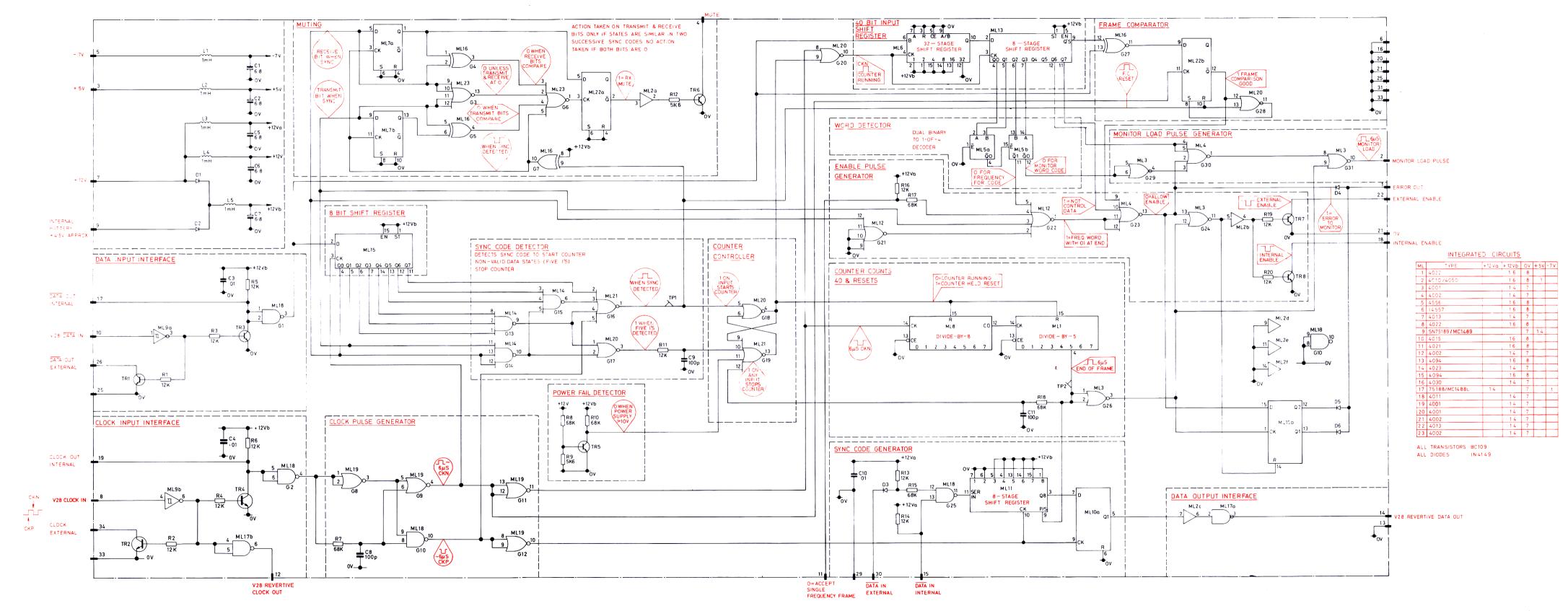

| Block Diagram: Serial Controller Board PS667                      | 4.1  |

|-------------------------------------------------------------------|------|

| Block Diagram: Serial Controller Board PS667 (Standard Version)   | 4.1A |

| Circuit Diagram: Serial Controller Board PS667                    | 4.2  |

| Circuit Diagram: Serial Controller Board PS667 (Standard Version) | 4.2A |

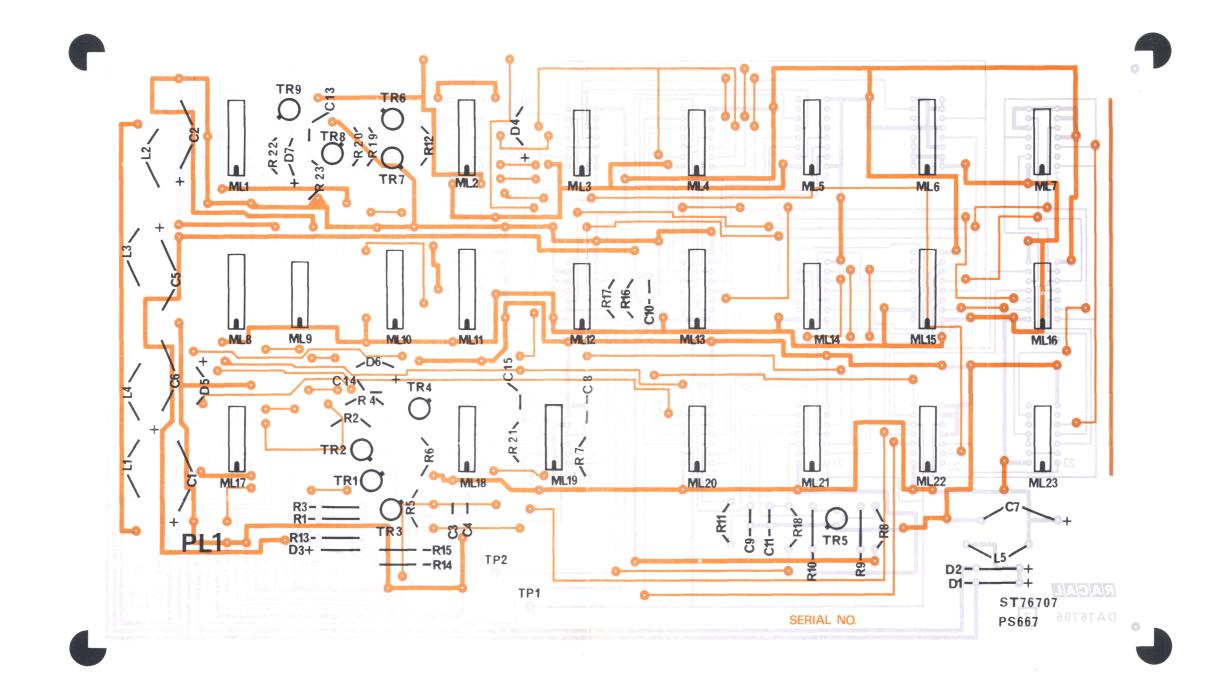

| Layout: Serial Controller Board PS667                             | 4.3  |

.

# CHAPTER 4

# SERIAL CONTROLLER BOARD PS667

#### INTRODUCTION

1. The serial controller board contains the synchronisation circuits, the frame comparator, the PTT/Mute control circuit and the sync. code generator for the revertive data.

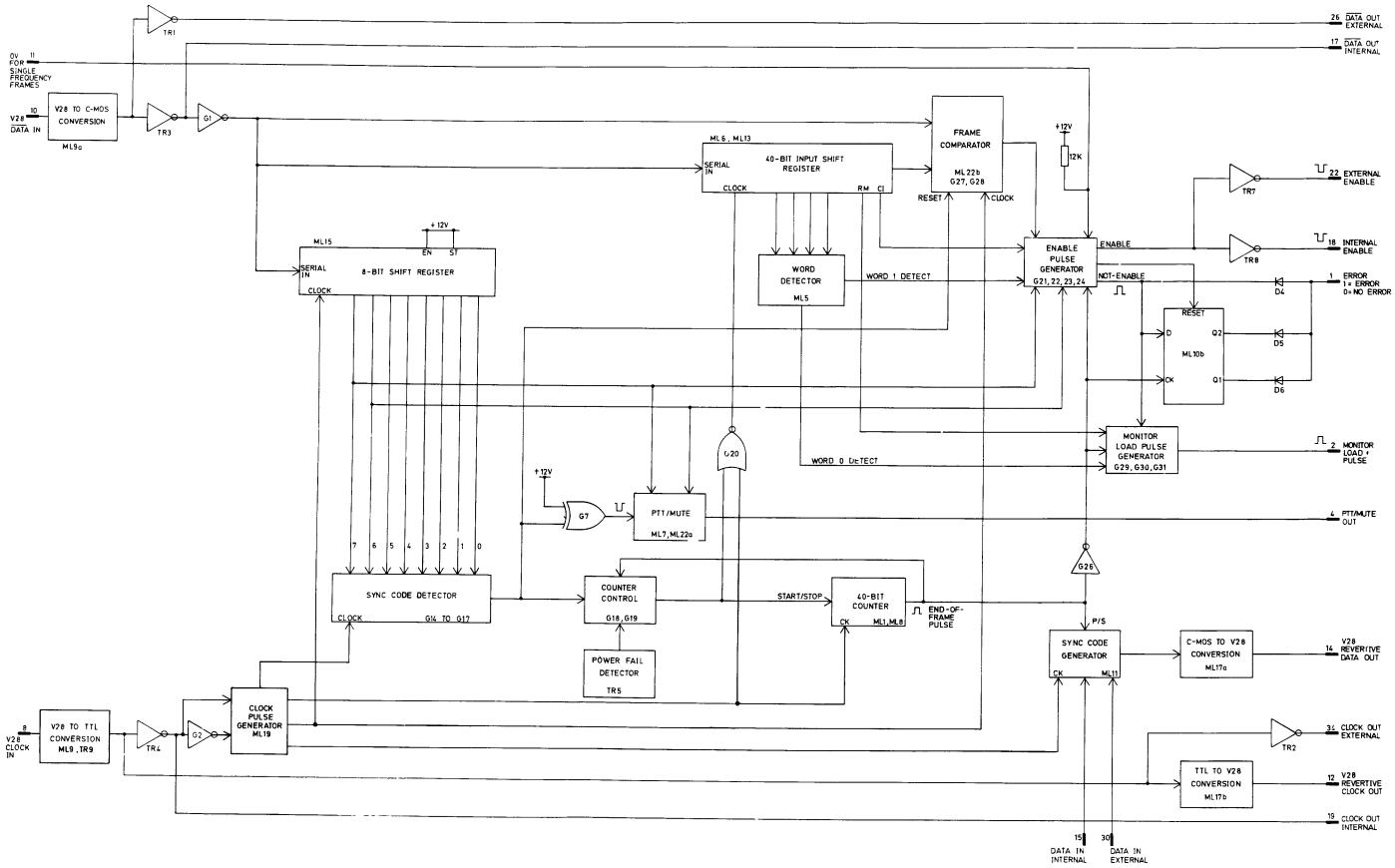

1A. Two versions of the board are currently in Service use, the standard version and that incorporating Mod No. A 8882. A block diagram of the board is given in fig. 4.1 (modified version) and fig. 4.1A (standard version). The circuit diagrams for these versions are given in fig. 4.2 and fig. 4.2A respectively. The layout diagram (fig. 4.3) relates to the standard version only.

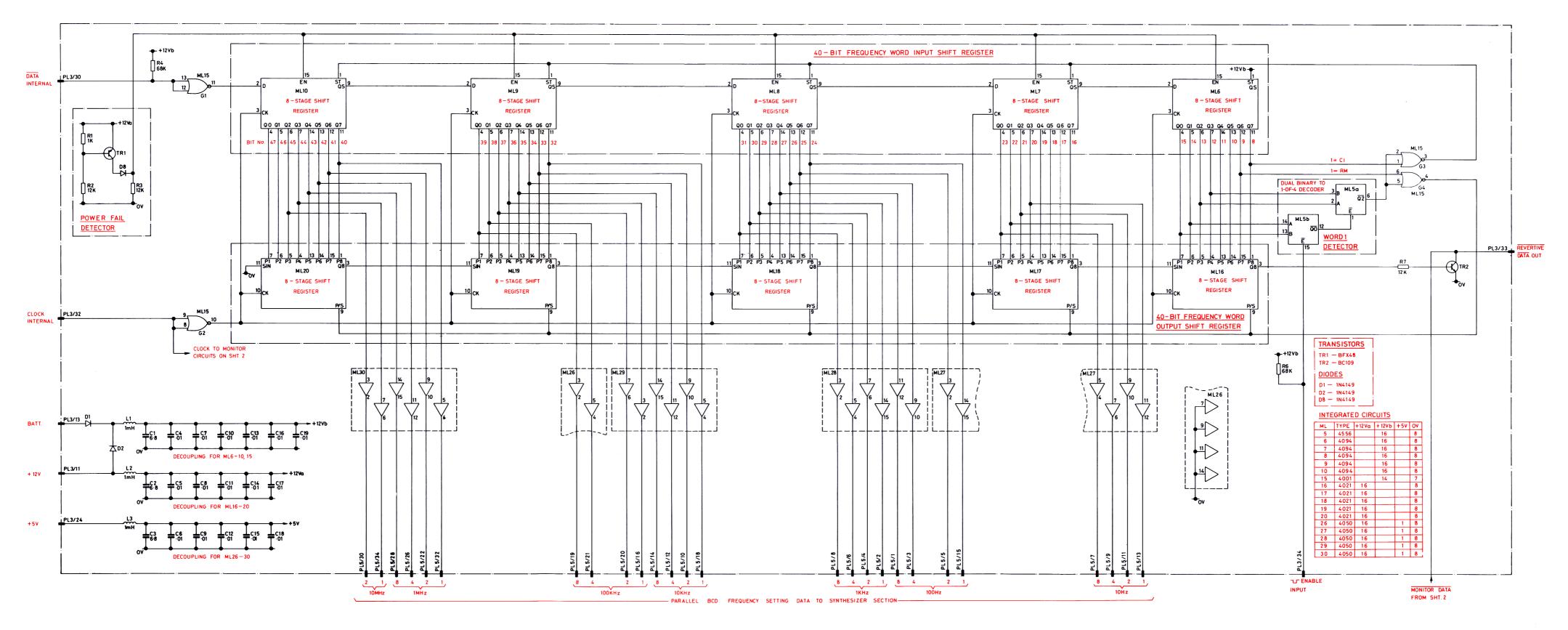

#### FUNCTIONAL DESCRIPTION

#### Control Data Input

2. The V28 inverted control data input from the MA.1072 (+12V for binary '0', -12V for binary '1'), at board pin 10 (fig.4.1), is converted to TTL levels (+5V for binary '1' and OV for binary '0'); it is then applied via inverting buffer TR1 (at C-MOS levels) to the external control connector (on the receiver rear panel) via board pin 26, and via inverting buffer TR3 to the frequency and monitor board and to the BFO and mode board, via board pin 17. The inverted data output from TR3 is also applied via C-MOS inverter G1 to an 8-bit shift register ML15, a 40-bit shift register ML6, ML13, and to the frame comparator.

#### Control Clock Input

- 3. The V28 control clock signal from the MA.1072, at board pin 8, is converted to TTL levels and is then applied

- (1) To a TTL to V28 level conversion stage, which provides the revertive clock output signal (board pin 12).

- (2) Via inverting buffer TR2 and board pin 34 to the external control connector (on the receiver rear panel).

- (3) Via inverting buffer TR4 and board pin 19 to the frequency and monitor board, and the BFO and mode board.

- (4) Via TR4 and G2 to the clock pulse generator.

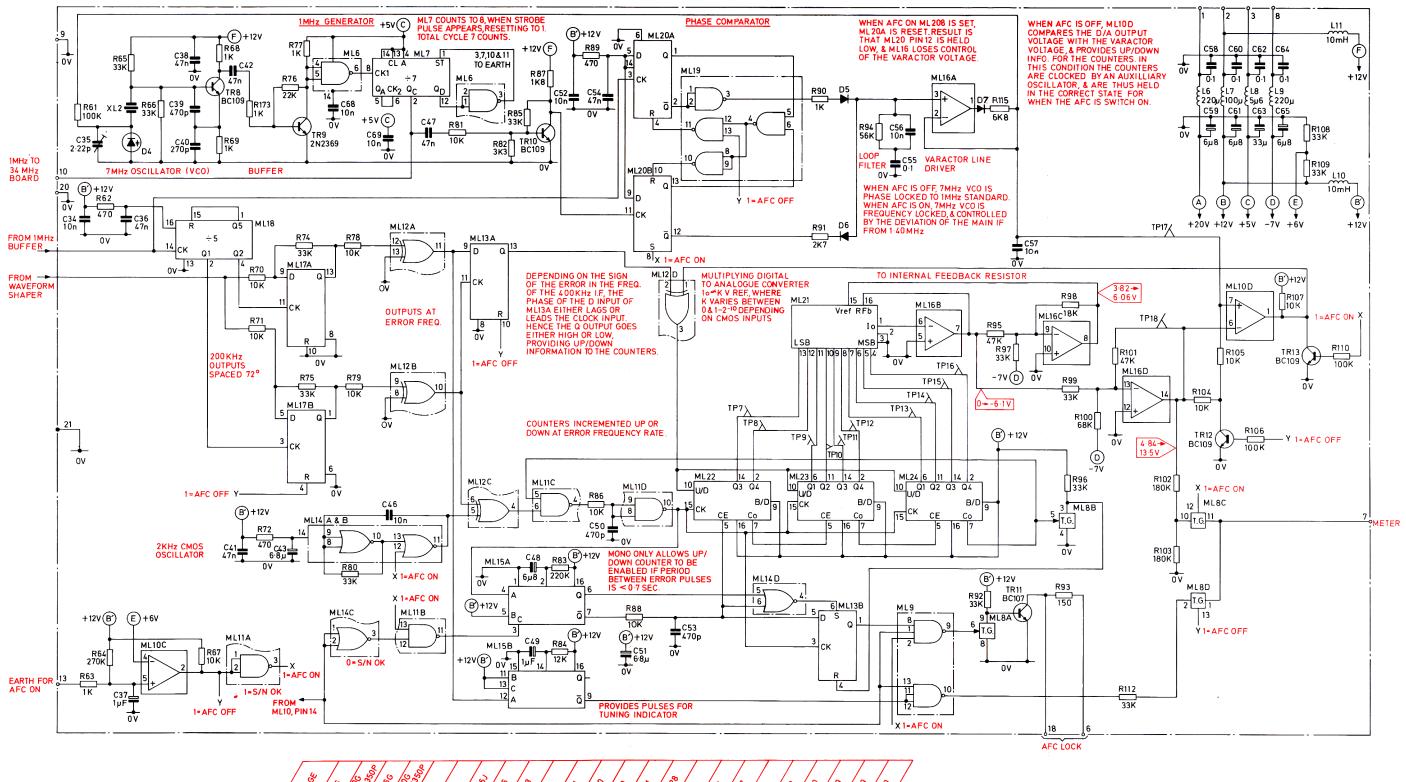

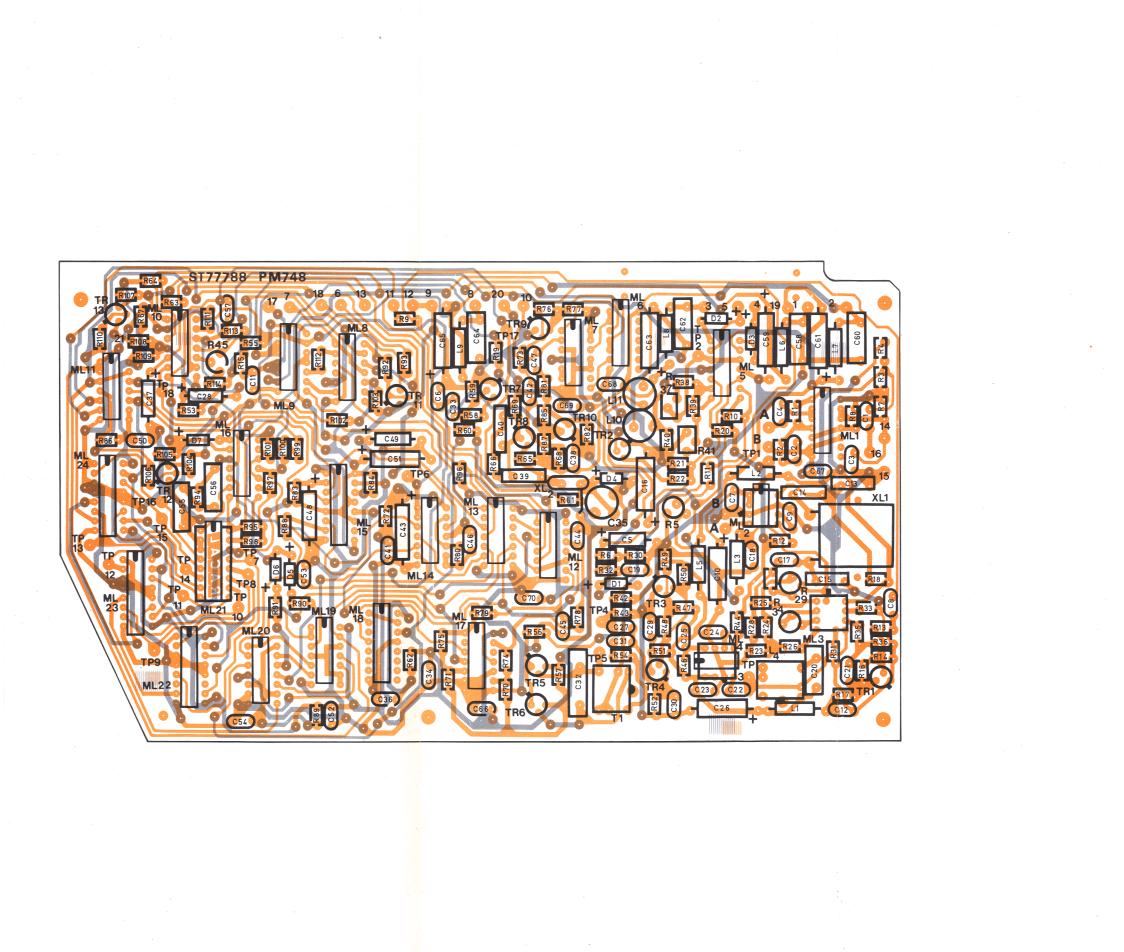

#### Clock Pulse Generator