# Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This pdf document was generated by me Colin Hinson from a Crown copyright document held at R.A.F. Henlow Signals Museum. It is presented here (for free) under the Open Government Licence (O.G.L.) and this pdf version of the document is my copyright (along with the Crown Copyright) in much the same way as a photograph would be.

The document should have been downloaded from my website <u>https://blunham.com/Radar</u>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<u>https://blunham.com/Radar</u>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you personally – I know that I would have liked to have found some of these files years ago – they would have saved me a lot of time !

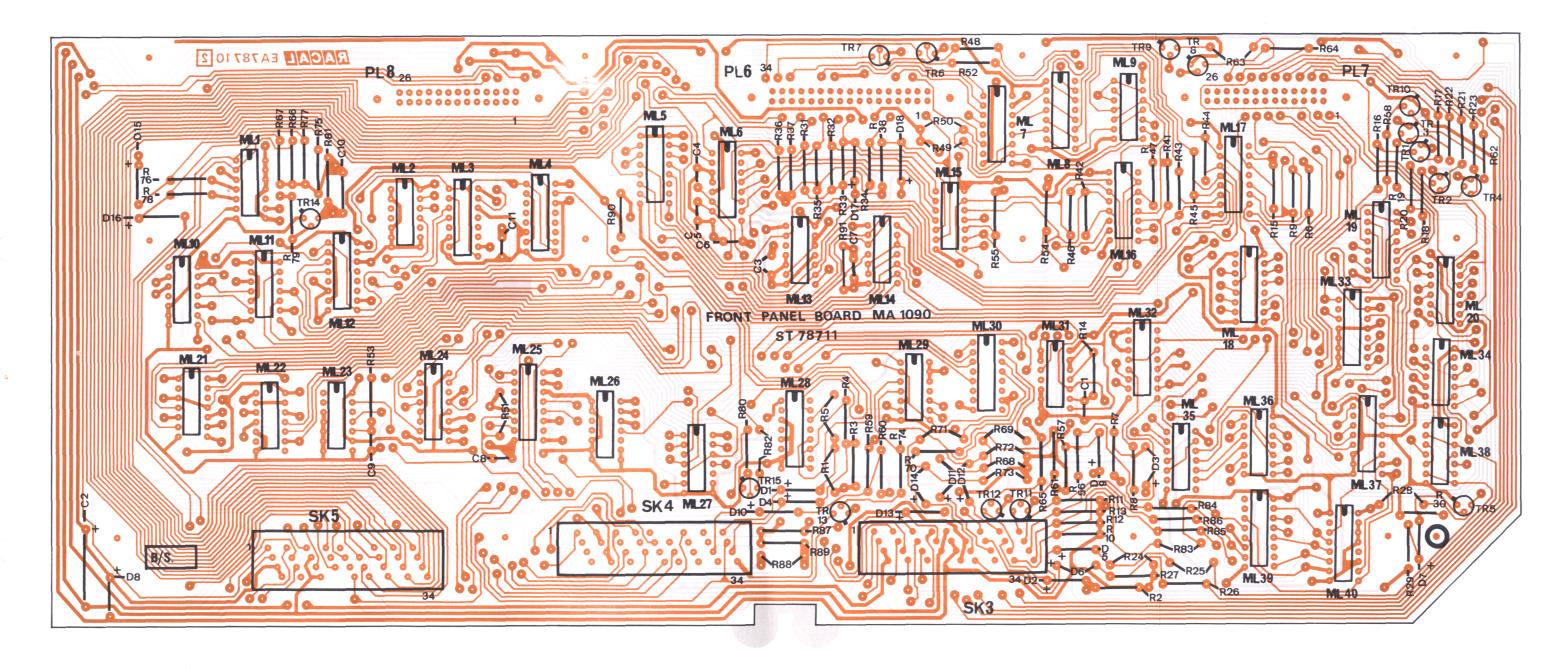

Colin Hinson In the village of Blunham, Bedfordshire.

AP 116E-0278-16

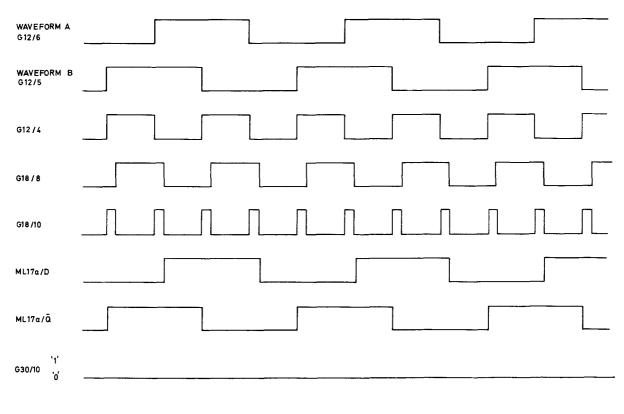

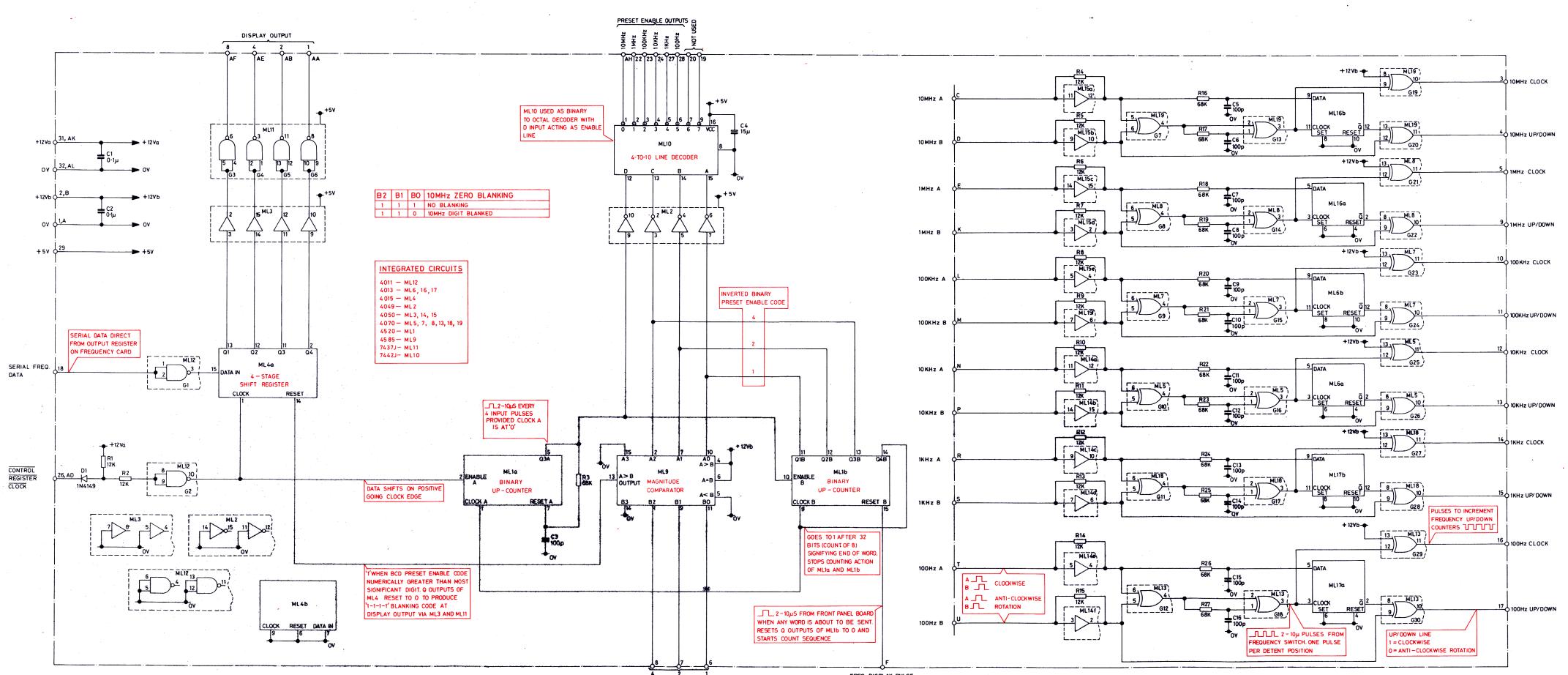

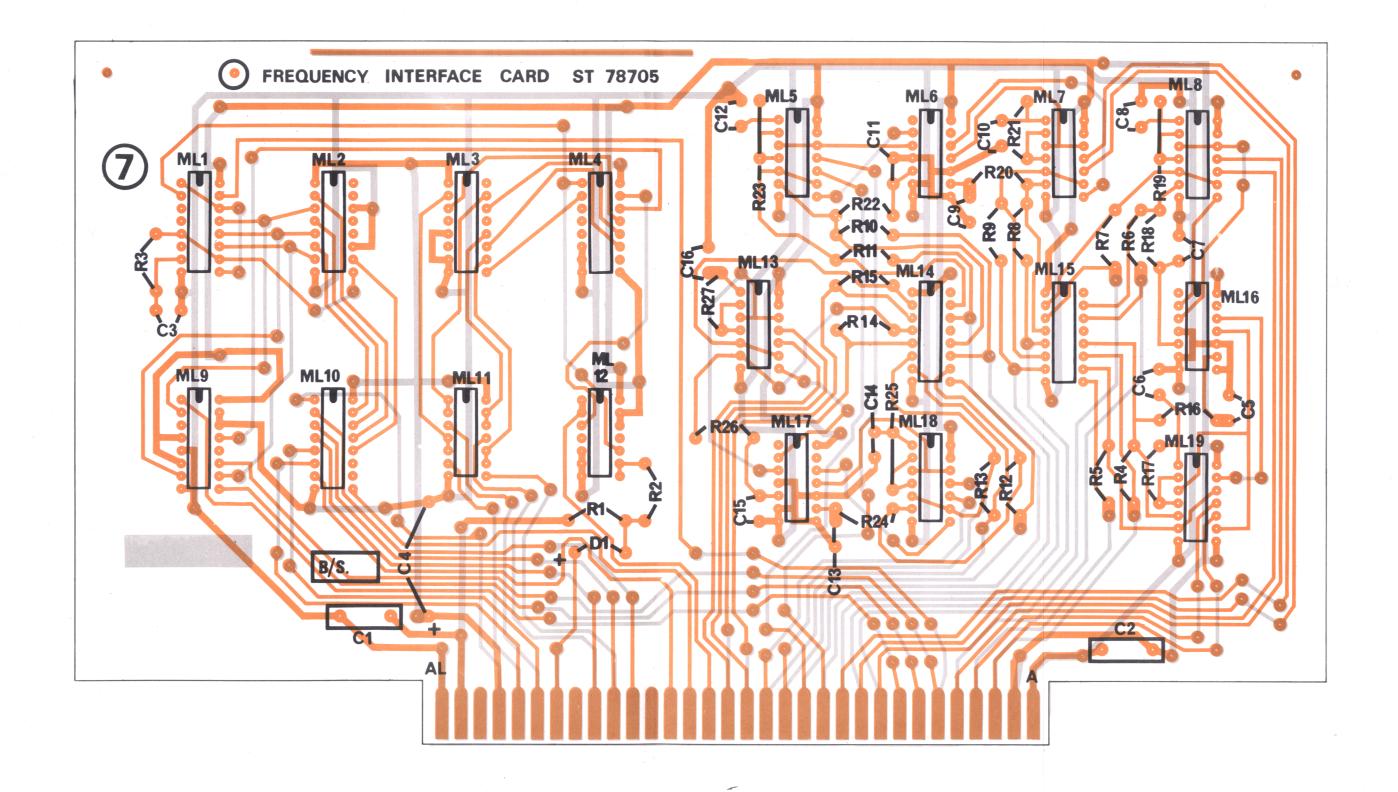

June 1980

## TRANSMITTER CONTROL UNIT (Racal Type MA. 1090)

### TECHNICAL AND REPAIR MANUAL

BY COMMAND OF THE DEFENCE COUNCIL

Ministry of Defence

Sponsored for use in the

ROYAL AIR FORCE by D. Sigs (Air)

Prepared by Racal Communications Systems Ltd., Bracknell, Berks.

Publications authority: ATP/MOD (PE)

Service users should send their comments through the channel prescribed for the purpose in : AP 100B-01 Order 0504

#### MODIFICATION RECORD

The following record confirms that this publication incorporates all technical changes necessitated by the modifications listed below. Information on modification titles, classification categories and Mark applicabilities is given in Topic 2.

Mod. No.

Brief description

A9378

TC0052

Replace nicad battery

Reduce arcing on mains switch

# Maintenance Manual

# MA. 1090 Transmitter Control Unit

Racal Communications Limited Western Road, Bracknell, RG12 1RG EnglandTel: Bracknell (0344) 3244Telex: 848166Grams: Racal Bracknell.Prepared by Group Technical Handbooks Department, Racal Group Services Limited.Printed in EnglandRef. WOH 8307Issue 2.7.80-30

### LETHAL WARNING

Voltages within this equipment are sufficiently high to endanger life.

Covers are NOT to be removed except by persons qualified and authorised to do so and these persons should always take extreme care once the covers have been removed.

Resuscitation instructions are given overleaf.

## FIRST AID

### in case of Electric Shock

- 1. Lay victim on his back.

- 2. Clear victim's mouth and throat.

- 3. Tilt victim's head back as far as possible and raise his head.

Have someone else send for a Doctor Keep patient warm and loosen his clothing

- 4. Pinch victim's nostrils.

- 5. Take a deep breath.

- Cover the victim's mouth with yours and blow, watching his chest rise. Note: Blow forcefully into adults, but gently into children.

- 7. Move your face away to allow victim to breathe out, watching his chest fall.

- 8. Repeat first five to ten breaths at a rapid rate; thereafter, take one breath every three to five seconds.

- 9. Keep victim's head back as far as possible all the time.

DO NOT Give liquids until patient is conscious

#### HANDBOOK AMENDMENTS

Amendments to this handbook (if any), which are on coloured paper for ease of indentification, will be found at the rear of the book. The action called for by the amendments should be carried out by hand as soon as possible.

#### ORDERS FOR SPARE PARTS

In order to expedite handling of spare part orders please quote:-

- (1) Type and serial number of equipment.

- (2) Circuit reference, description, Racal part number, and manufacturer of part required.

- (3) Quantity required.

- NOTE: If the equipment is designed on a modular basis, please include the type and description of the module for which the replacement part is required.

MA.1090 Transmitter Control Unit

### MA.1090 TRANSMITTER CONTROL UNIT

#### CONTENTS

TECHNICAL SPECIFICATION

GENERAL DESCRIPTION CHAPTER 1 INSTALLATION INFORMATION CHAPTER 2 OPERATING INFORMATION CHAPTER 3 DISMANTLING AND RE-ASSEMBLY CHAPTER 4 SERIAL CONTROL SYSTEM CHAPTER 5 FUNCTIONAL DESCRIPTION CHAPTER 6 CHAPTER 7 LOGIC LEVELS FRONT PANEL ASSEMBLY CHAPTER 8 CHAPTER 9 FRONT PANEL BOARD FREQUENCY CARD CHAPTER 10 CHAPTER 11 FREQUENCY INTERFACE CARD CONTROL PROCESSOR CARD CHAPTER 12 CHAPTER 13 STATUS CARD DISPLAY PROCESSOR CARD CHAPTER 14 CHAPTER 15 POWER SUPPLIES CHAPTER 16 MOTHERBOARD PARTS LIST CHAPTER 17 **ALTERNATIVES AMENDMENTS**

### TECHNICAL SPECIFICATION

| Frequency:           | selected by six                                                                                     | range 0.0 to 29 999.9 kHz<br>rotary switches. Minimum<br>Hz. Frequency display provided<br>prs.                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode:                | Selected by eig<br>buttons as follow                                                                | ht interlocked illuminated push-<br>ws:-                                                                                                           |

|                      | CW (selects KE<br>AM-6 (selects U<br>USB-20<br>USB SUPP<br>LSB-20<br>LSB SUPP<br>ISB-20<br>ISB SUPP |                                                                                                                                                    |

| External Entry:      | for external free<br>Frequency Entry                                                                | de via front panel EXTERNAL socket<br>quency data entry from the MA.1083<br>/ Pad. Rear panel connections are<br>ternal data entry from external   |

| Transmitter Control: | Eight illuminate<br>follows:-                                                                       | ed push-buttons are provided as                                                                                                                    |

|                      | OFF:                                                                                                | Cancels the STANDBY and EHT ON selections.                                                                                                         |

|                      | STANDBY:                                                                                            | Selects the STANDBY-ON<br>condition. Cancels OFF and<br>EHT ON.                                                                                    |

|                      | EHT ON:                                                                                             | Selects the EHT ON condition if<br>STANDBY is already selected.<br>Not operational when MA.1090<br>is used with Racal solid-state<br>transmitters. |

|                      | RESET:                                                                                              | Resets the transmitter trip<br>conditions and initiates a tuning<br>sequence.                                                                      |

|                    | LOW POWER:                        | Selects the LOW POWER<br>condition; may be cancelled by<br>a second press.                                                                    |

|--------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                    | MUTE:                             | Cancels OPERATE and TRANSMIT, and mutes the transmitter.                                                                                      |

|                    | OPERATE:                          | Cancels MUTE and TRANSMIT;<br>allows the external PTT line to<br>control the transmit state of the<br>transmitter.                            |

|                    | TRANSMIT:                         | Cancels MUTE and OPERATE.<br>Sets the transmitter to the<br>TRANSMIT state.                                                                   |

| Transmitter State: | of the transmitt<br>and TRANSMIT  | ators are provided to show the state<br>er. STANDBY, EHT ON, READY<br>indicators are illuminated in green,<br>/ER in amber, and FAULT in red. |

| Status Controls:   | Four push-butto<br>and RECALL.    | ons designated CHECK, IN, OUT                                                                                                                 |

|                    |                                   | rogates the transmitter control settings<br>e MA.1090 front panel controls.                                                                   |

|                    | both the MA.1                     | ta from an external source to control<br>090 and the transmitter; disables the<br>panel controls.                                             |

|                    |                                   | he output control data to be<br>an external control unit.                                                                                     |

|                    |                                   | ws subsequent recall of frequency and<br>ernal memory) without affecting the<br>strol state.                                                  |

| Status Indicators: | indicator shows<br>available from | are provided; a green CONTROL ON<br>s that control of the transmitter is<br>the MA.1090. A red LINE FAULT<br>s failure of the control link.   |

| Serial Control System: | format is used for the<br>This specifies data co                           | ontrol Of Racal Equipment)<br>interchange of serial data.<br>ding and should be consulted<br>ecification of the serial data<br>5).                                                                                                                   |

|------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signalling Levels:     |                                                                            | nnections are compatible with<br>eristics of CCITT recommendation<br>clauses of V24.                                                                                                                                                                 |

| Frame Length:          | Each data frame comp<br>16-bit preamble and c                              | rises 48 bits and consists of a<br>1 32-bit data word.                                                                                                                                                                                               |

| Control Words:         | The MA.1090 uses the control purposes:                                     | e following two words for                                                                                                                                                                                                                            |

|                        |                                                                            | uency setting<br>e and transmitter control                                                                                                                                                                                                           |

| Revertive Words:       | monitored information                                                      | vord, is used for revertively<br>. Words 1 and 3 may be<br>sing the CHECK status.                                                                                                                                                                    |

| Computer Word:         | Word 9, the operator computer control of the                               | addressing word, is used for<br>ne MA.1090 status.                                                                                                                                                                                                   |

| Data Transfer Rates:   | Internal Clock: 19.2<br>External Clock: from                               | k bauds +4% –10%<br>100 bauds to 20k bauds                                                                                                                                                                                                           |

| Line Requirements:     | The line connections<br>following CCITT V24                                | provided conform to the<br>descriptions:-                                                                                                                                                                                                            |

|                        | V24 Designator                                                             | Description                                                                                                                                                                                                                                          |

|                        | 101<br>* 102<br>* 103<br>* 104<br>105<br>106<br>* 113<br>114<br>115<br>134 | Chassis Earth<br>Signal Earth<br>Control Data output<br>Revertive Data input<br>Request to send (RTS) output<br>Ready for sending (RFS) input<br>Control Clock output<br>Master Clock input<br>Revertive Clock input<br>Revertive Data Present input |

\* Denotes minimum control line requirement for basic extended control system (four lines).

| Electrical Line Characteristics: | • •                                                              | e: 1 kilohm max.<br>ce: 2500 pF max.                                                                                                                   |

|----------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter Addressing:          | connector to pro                                                 | t may be connected via a rear panel<br>ovide addressing facilities for up to<br>. This uses SCORE word 8, the<br>essing word.                          |

| Control Unit Addressing:         | (00 to 99) to en<br>information to a                             | s fitted with internal address switches<br>able a computer to address<br>a particular MA.1090 via a common<br>uses SCORE word 9, the operator          |

| Computer Support:                | computer to ent<br>MA.1090 status                                | ut ports are provided for access by a<br>er control information or to read the<br>information. These ports are also<br>schanges between control units. |

| Dimensions:                      | Height:                                                          | 178 mm                                                                                                                                                 |

|                                  | Width:<br>Depth:                                                 | 483 mm<br>300 mm                                                                                                                                       |

| Weight:                          | 16 kg (approxim                                                  | nately).                                                                                                                                               |

| Power Requirements:              | Supply voltage:                                                  | 100V to 125V in 5V steps                                                                                                                               |

|                                  |                                                                  | OR                                                                                                                                                     |

|                                  |                                                                  |                                                                                                                                                        |

|                                  |                                                                  | 200V to 250V in 10V steps                                                                                                                              |

|                                  | Tolerance:                                                       | 200V to 250V in 10V steps<br>+6% to -10%                                                                                                               |

|                                  | Tolerance:<br>Frequency:                                         |                                                                                                                                                        |

|                                  |                                                                  | +6% to -10%<br>45 Hz to 400 Hz                                                                                                                         |

| Environmental Conditions:        | Frequency:<br>Power consumpt<br>The equipment<br>requirements of | +6% to -10%<br>45 Hz to 400 Hz                                                                                                                         |

### <u>CHAPTER 1</u>

### GENERAL DESCRIPTION

### CONTENTS

| INTRODUCTION 1                |  |

|-------------------------------|--|

| SCORE FORMAT 2                |  |

| ROUTINE AND NEW DATA 4        |  |

| SYNCHRONISATION 5             |  |

| FRAME COMPARISON 6            |  |

| REVERTIVE DATA 7              |  |

| CLOCK CIRCUITS 8              |  |

| SIGNAL-TO-LINE REQUIREMENTS 9 |  |

| PHYSICAL DESCRIPTION 10       |  |

| Front Panel Assembly 11       |  |

| Power Supply Module 12        |  |

| Chassis Assembly 13           |  |

L

### CHAPTER 1

### GENERAL DESCRIPTION

#### INTRODUCTION

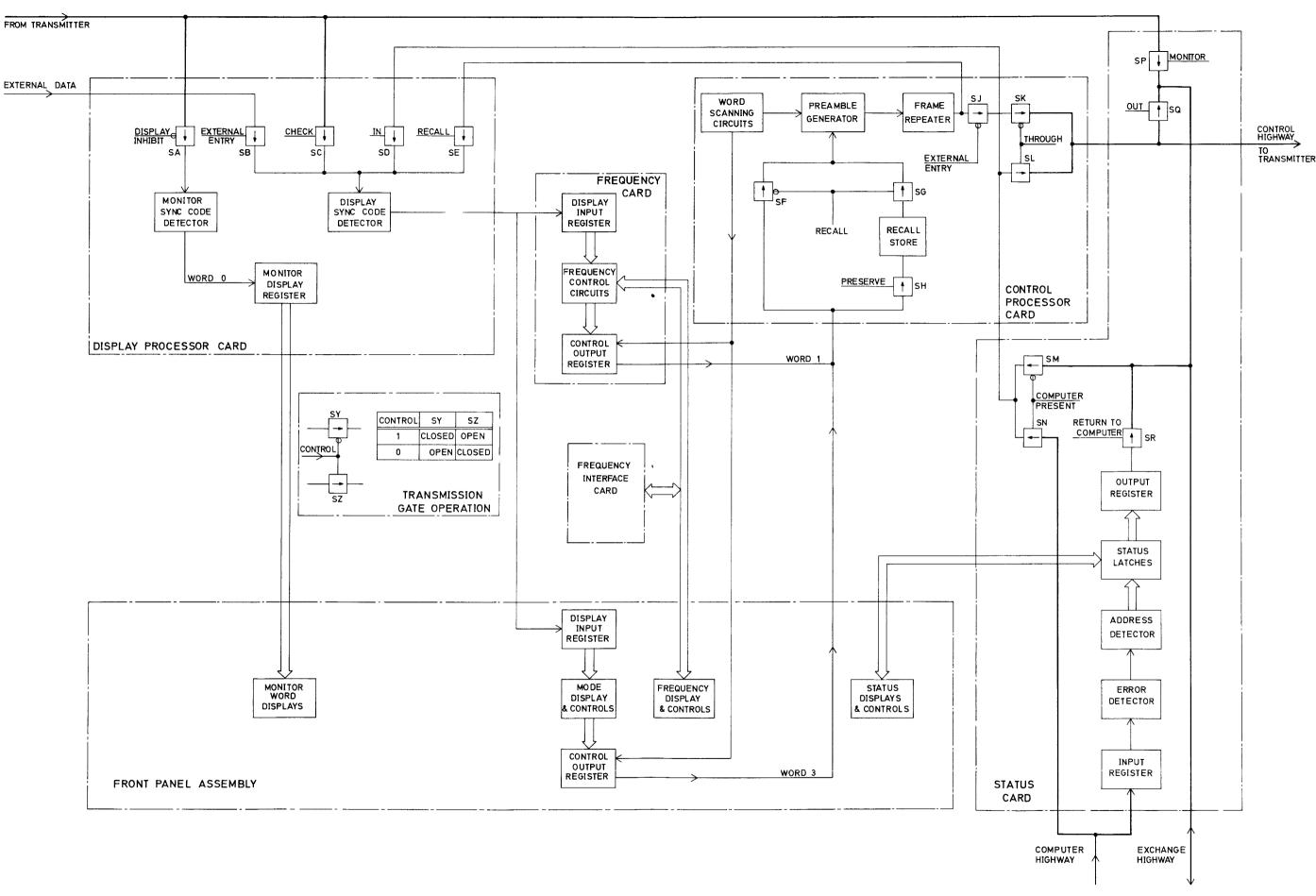

1. The MA.1090 control unit is designed for use with an externally controlled HF transmitter assembly, such as the Racal MA.1722/MA.1720, in conjunction with, for example, the Racal TTA.1860 HF Transmitter. Frequency selection and all other functions such as mode and transmitter control, are achieved by the use serial control data which conforms to the SCORE (Serial Control Of Racal Equipment) format.

#### SCORE FORMAT

2. The SCORE format for serial control, as used by the MA.1090, is fully described in Chap. 5. It is based on a number of 48-bit synchronous frames, each of which contains a 16-bit preamble (synchronisation, word number identification, etc.), followed by a 32-bit data word. The total capacity of the SCORE format is sixteen 32-bit words numbered 0 to 15, each of which may be revertively checked. Of these, the MA.1090 uses word numbers 0, 1 and 3 to control the associated transmitter. Although word 0 is sent as part of the control data sequence, it does not contain any control information and is used only for revertive data. Word 1 is used to convey the frequency setting information, whilst word 3 is used for mode and transmitter control data.

3. Words 8 and 9 have been designated for equipment and operator addressing and are available for use in computer assisted control systems. Words 2, 4 and 5 of the SCORE format have been designated for HF and VHF/UHF receiver control purposes; this leaves eight undesignated words (6, 7 and 10 to 15), any or all of which may be used to expand the control system. Words 1 to 7 may be preserved in the MA.1090 internal memory for subsequent recall purposes; words 8 to 15 cannot be recalled.

#### ROUTINE AND NEW DATA

4. During the time that no MA.1090 front panel control settings are being changed, 'routine data' frames are sent to the associated transmitter in numerical sequence (and then repeated), at a rate determined by the clock frequency. When a front panel control setting is changed however, the routine data sequence is interrupted so that the next frame to be sent will contain the change of function information. Thus the frames are sent out of numerical sequence and priority is given to those frames containing new data. This results in the rapid transfer of the new data in order to up-date the control settings of the associated transmitter as quickly as possible.

#### SYNCHRONISATION

5. The 16-bit preamble at the front of each 32-bit data word contains a 6-bit sync. code consisting of a '0' followed by five consecutive '1s'. This code has to be detected at the associated transmitter for each frame before any further action may take place.

#### FRAME COMPARISON

6. The associated transmitter drive unit assembly contains a frame comparison circuit for error detection purposes. Each control data frame generated by the MA.1090 is sent twice and up dating of the transmitter settings may only take place provided that the two frames are identical. As the probability of two consecutive frames containing identical bit errors is small, the system provides high security against an incorrect transmitter setting.

#### REVERTIVE DATA

7. The format for the revertive data from the associated transmitter is the same as for the forward control data so that essentially an inverse process takes place. Frame comparison however, does not take place as the revertive data is used at the MA.1090 to provide a confidence check only, i.e. the presence or absence of the revertive data has no effect on the transmitter control functions.

#### CLOCK CIRCUITS

8. The clock circuits provide the timing signals required by the various parts of the system. The basic clock signal may be derived either from the internal 19.2 kHz clock generator or an externally connected master clock generator.

#### SIGNAL-TO-LINE REQUIREMENTS

9. The signal-to-line requirements for the serial control of the associated transmitter are based on the International Telegraph and Telephone Consultative Committee (CCITT) recommendations V24 and V28; these are described in Chap. 5. Separate lines are used for data, clock and certain other control signals travelling in each direction.

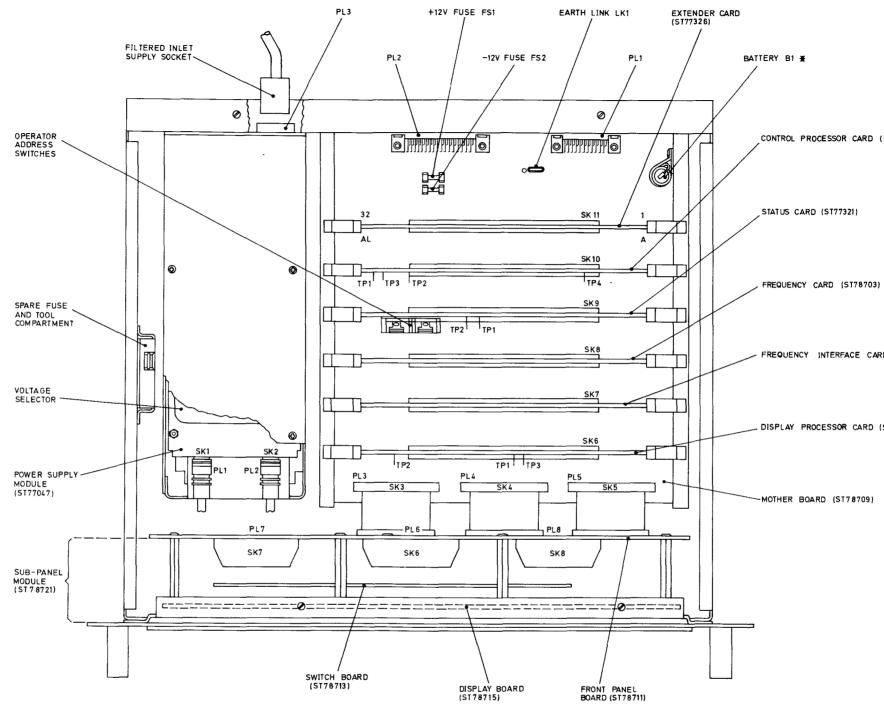

#### PHYSICAL DESCRIPTION

10. The MA.1090 divides into three main separable assemblies, namely the front panel assembly, the power supply module and the chassis assembly.

#### Front Panel Assembly

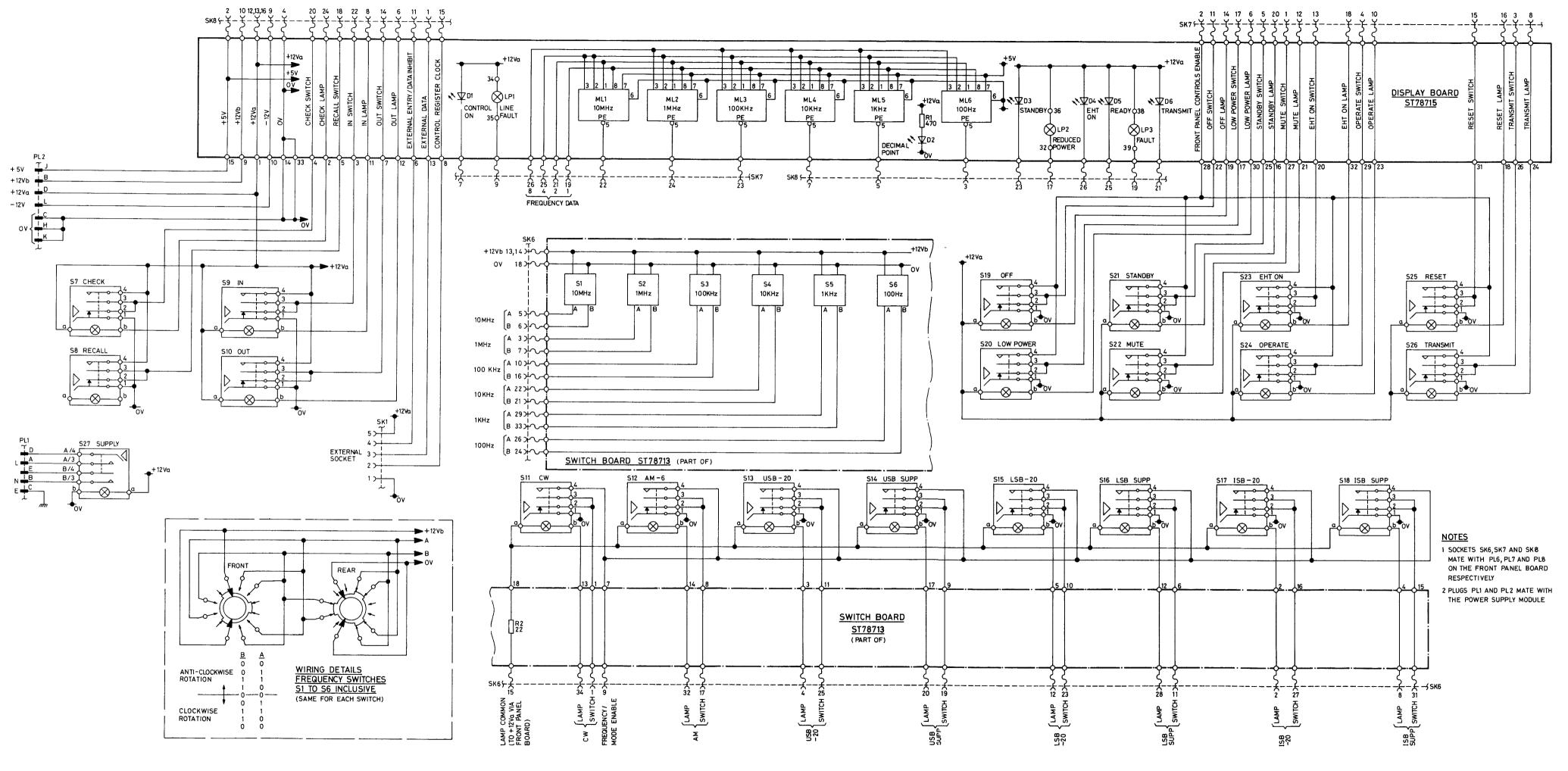

11. The front panel assembly comprises the front panel together with a sub-panel module which contains the front panel board, a switch board assembly, the display board and the various front panel controls and connections. By the removal of front panel

screws the front panel assembly may be detached from the chassis assembly. Electrical connections are made via five cable and connector assemblies; three of these connect with the chassis assembly whilst the remaining two connect with the power supply module.

#### Power Supply Module

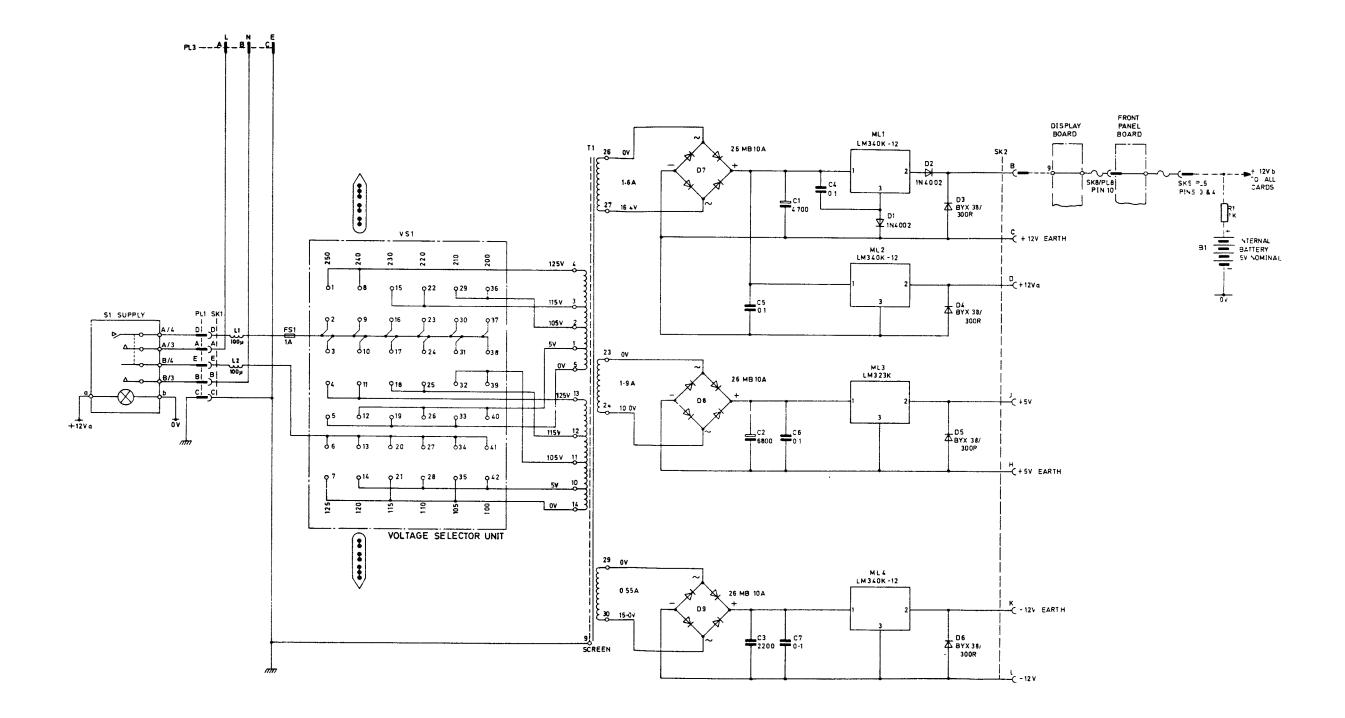

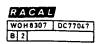

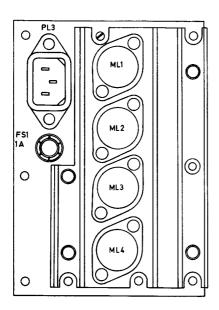

12. The power supply is attached to the chassis base plate with six screws, and to the rear panel with a single screw. It has an insulating top cover plate under which is located the supply voltage adjustment panel. The rear face of the module, which carries the supply input connector, the supply input fuse and four three-terminal voltage regulators mounted on a heatsink, protrudes through an aperture in the chassis assembly rear panel. Electrical connections to the remainder of the unit are made via two sockets, one for the supply on/off switching and the other for the regulated voltage outputs.

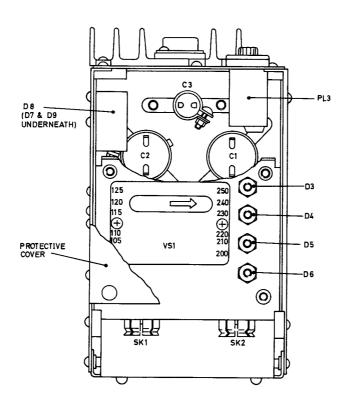

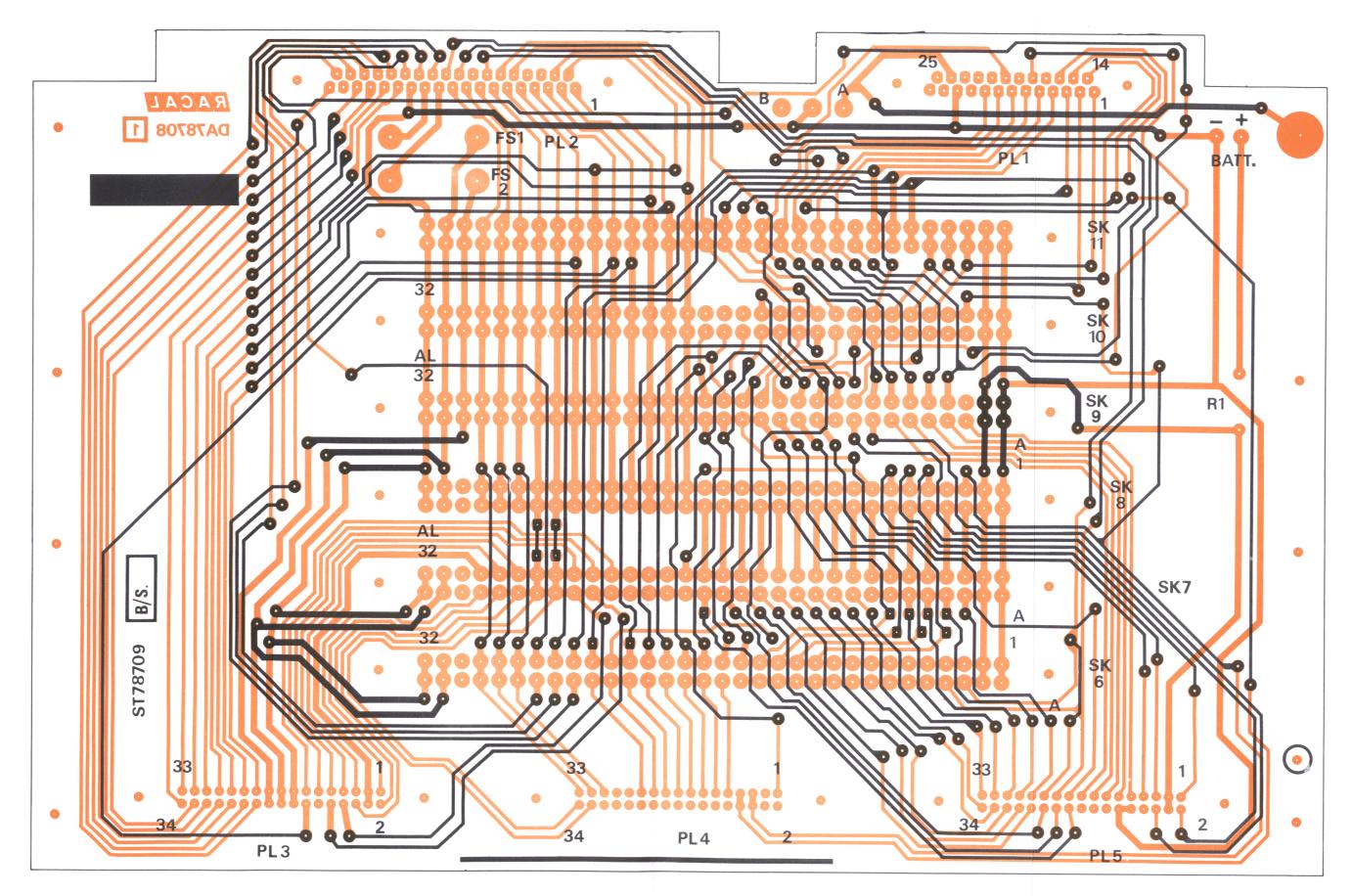

#### Chassis Assembly

13. The chassis assembly houses a motherboard which accomodates (via edge connectors) five printed circuit cards, namely the display processor card, the frequency card, the frequency interface card, the status card and the control processor card. Also mounted on the motherboard is an extender card which, when positioned in its stowage edge connector, provides a number of voltage and signal monitoring points. The electrical connections between the motherboard and the front panel board are made via three flexible ribbon cable and connector assemblies, whilst the external connection plugs PL1 and PL2 are mounted directly on the motherboard to protrude through apertures in the rear panel.

14. An accessory and spare fuse compartment is located in the left-hand chassis side member; it contains a push-button screen remover, a lamp remover, two spare

100 mA fuses (for the plus and minus 12V fuses FS1 and FS2 mounted on the motherboard) and a spare 1A supply input fuse. The compartment is fitted with a snap-fit cover plate. (A spare lamp is located in the non-illuminated RECALL push-button).

### CHAPTER 2

### INSTALLATION INFORMATION

### CONTENTS

|                             | Para. |

|-----------------------------|-------|

| INTRODUCTION                | 1     |

| REAR PANEL CONNECTIONS      | 2     |

| Power Input Socket          | 3     |

| Power Input Fuse            | 5     |

| Earth Terminal              | 6     |

| Multi-way plugs PL1 and PL2 | 7     |

| Internal controls           |       |

| Voltage Selector            | 8     |

| Earth Link                  | 9     |

| Operator Addressing         | 10    |

| Internal Fuses              | 11    |

| MA.1090 EXTERNAL CONNECTOR  | 12    |

#### TABLES

.

| PL1 Connections<br>PL2 Connections | 2-4<br>2-5 |  |

|------------------------------------|------------|--|

|                                    |            |  |

•

#### ILLUSTRATIONS

|                     | Fig. |

|---------------------|------|

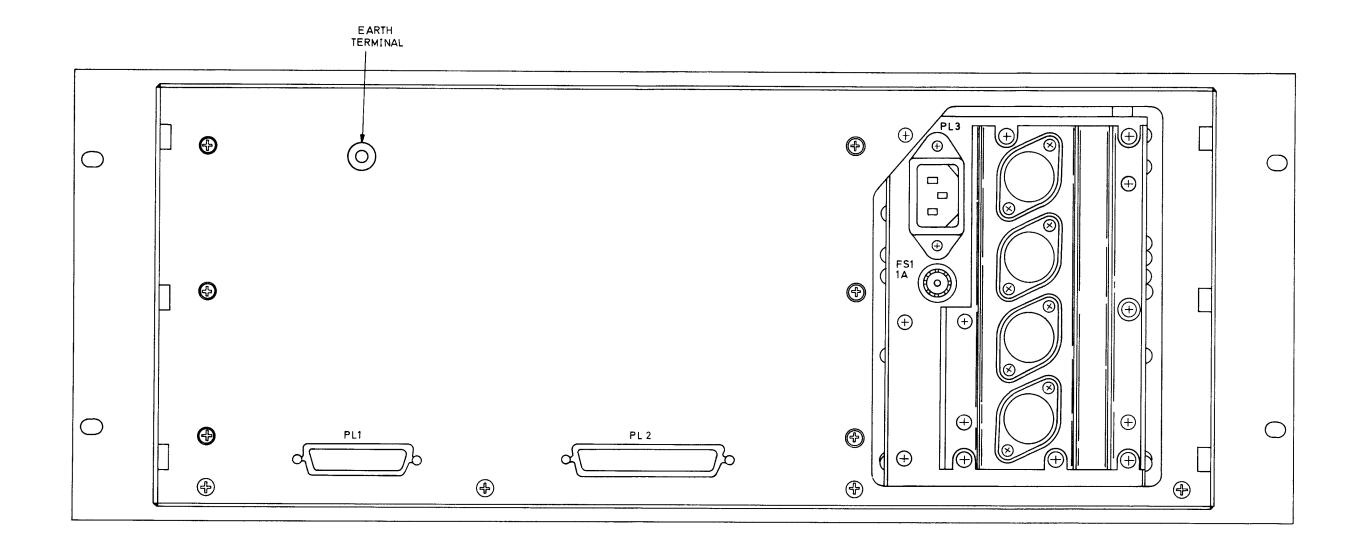

| Rear Panel: MA.1090 | 2.1  |

| Plan View: MA.1090  | 2.2  |

Page

### <u>CHAPTER 2</u>

### INSTALLATION INFORMATION

#### INTRODUCTION

This chapter provides information to assist in the installation of an MA.1090 into a transmitter system. The MA.1090 may be connected in a number of ways depending on the particular installation or application, ranging from a single unit controlling a single transmitter over short lines (extended control) to a computer assisted multi-address system employing several transmitters, and controlled from a remote point where the data is conveyed via a pair of data modems. Detailed installation information is therefore beyond the scope of this manual and reference should be made to the appropriate system manuals.

#### REAR PANEL CONNECTIONS

2. A brief description for each rear panel connection is given. Refer to Fig. 2.1 for a rear view of the MA.1090.

#### Power Input Socket

3. The power supply input connection mates with PL3 and is made via a 3-way socket and cable assembly. The cable connections are as follows:-

| Brown        | Live    |

|--------------|---------|

| Blue         | Neutral |

| Green/Yellow | Earth   |

4. The 3-way socket is of the filtered inlet type (Belling Lee L.2134A, Racal No. 928265); the connections are as follows:-

| L | Live    |

|---|---------|

| Ņ | Neutral |

| ÷ | Earth   |

#### Power Input Fuse

- The power input fuse, FS1, mounted below the power input connector, is a slowblow type, rated at 1A. The replacement is a Belling Lee L2080/1, Racal No.

922456.

- <u>NOTE:</u> Spare fuses are located in a compartment in the left-hand member of the chassis assembly. A spare lamp is mounted in the RECALL push-button.

#### Earth Terminal

6. A terminal is provided on the rear panel of the MA.1090 for connection to the earthing system of the rack or cabinet.

#### Multi-way Plugs PL1 and PL2

7. The connections to these plugs are listed in tables 1 and 2. The actual connections required are dependent upon the particular installation and reference should be made to the respective system manual. The mating socket details are as follows:-

- PL1 25-way connector, Cannon DB25S, Racal No. 915970 Shell junction, Cannon DB51213-1, Racal No. 914299 Retainer, Cannon DB5122-1, Racal No. 914245

- PL2 37-way connector, Cannon DC375, Racal No. 915656 Shell junction, Cannon DC51215-1, Racal No. 918105 Retainer, Cannon DC51222-1, Racal No. 914245

#### INTERNAL CONTROLS

#### Voltage Selector

The MA.1090 is fitted with a voltage selector panel which is accessible after removing the unit top cover plate and the power supply module cover plate (fig. 2.2). Ensure that the voltage selector is correctly set to suit the intended source of supply.

#### Earth Link

A two-position link, LK1, provides for isolated signal earth and chassis earth connections (position B) or common signal and chassis earth connections (position A).

The location of LK1 is shown in fig. 2.2.

#### **Operator Addressing**

10. Two thumbwheel switches are mounted on the status card (fig. 2.2) for operator addressing purposes. These are for use with computer assisted systems and are described in the appropriate systems manuals.

#### Internal Fuses

Two fuses, FS1 and FS2, are fitted to the motherboard (fig. 2.2); these fuses protect the +12V and -12V supplies which are available for external use (Table 2). They are rated at 100 mA, replacement Belling Lee L754, Racal No. 915348.

#### MA.1090 EXTERNAL CONNECTOR

12. The EXTERNAL socket on the MA.1090 front panel is for the connection of ancillary equipment such as the Racal MA.1083 frequency entry pad. The mating connector is a 5-pin DIN plug, Farnell E43, Racal No. 918751. The connections are listed below:-

- $1. \quad 0V (Earth)$

- 2. Control Clock output

4

- 3. Serial Data input

- 4. External Entry Select (OV to select)

- 5. +12∨

### TABLE 1: PLI CONNECTIONS

### <u>PL1</u>

| 1  | Master Clock Input            |

|----|-------------------------------|

| 2  | Control Clock Output          |

| 3  | Ready for Sending (RFS) Input |

| 4  | Revertive Clock Input         |

| 5  | Revertive Data Present        |

| 6  | Computer Clock                |

| 7  | Computer Present              |

| 8  | Exchange Clock                |

| 9  | Exchange Busy                 |

| 10 |                               |

| 11 | Signal Earth                  |

| 12 |                               |

| 13 | ~                             |

| 14 | Control Data Output           |

| 15 | Request to Send (RTS) Output  |

| 16 | Revertive Data Input          |

| 17 |                               |

| 18 | Computer Data                 |

| 19 |                               |

| 20 | Exchange Data                 |

| 21 |                               |

| 22 |                               |

| 23 |                               |

| 24 | Chassis Earth                 |

| 25 |                               |

### TABLE 2: PL2 CONNECTIONS

| PL2  |                                                          |

|------|----------------------------------------------------------|

| ן י  |                                                          |

| 2    | Word Enable Lines                                        |

| 3    |                                                          |

| 4 _] |                                                          |

| 5    | Control Register Strobe Used for Extra Word Capability   |

| 6    | Control Register Data                                    |

| 7    | Control Register Clock                                   |

| 8    | Display Register Strobe                                  |

| 9    | Display Register Data                                    |

| 10   | Display Register Clock                                   |

| 11   | -12V                                                     |

| 12   | +12V external use. Protected by 100 mA fuses.            |

| 13   | 0V (Earth)                                               |

| 14   | Ŵ                                                        |

| 15   | X Control User Functions                                 |

| 16   | Y (Input)                                                |

| 17   | z                                                        |

| 18   |                                                          |

| 19   | Spare                                                    |

| 20   | New Data ] Used for Extra Word                           |

| 21   | Word Present Capability                                  |

| 22   |                                                          |

| 23   |                                                          |

| 24   | Control Register Modify – Used for Extra Word Capability |

| 25   | Set CHECK                                                |

| 26   | PTT                                                      |

| 27   |                                                          |

| 28   | External Entry/Data Inhibit                              |

### TABLE 2 (Continued)

| PL2 |  |

|-----|--|

|-----|--|

| 29 | External Data  |                                    |

|----|----------------|------------------------------------|

| 30 | Transmit       |                                    |

| 31 | Mute           |                                    |

| 32 | External Entry |                                    |

| 33 | Auto Reset Swi | itch                               |

| 34 | D <b>7</b>     |                                    |

| 35 | с              | Revertive User Functions (Outputs) |

| 36 | В              |                                    |

| 37 | A              |                                    |

|    |                |                                    |

~

.

ł

1

# REFER TO MOD No. A9378

.

.

.

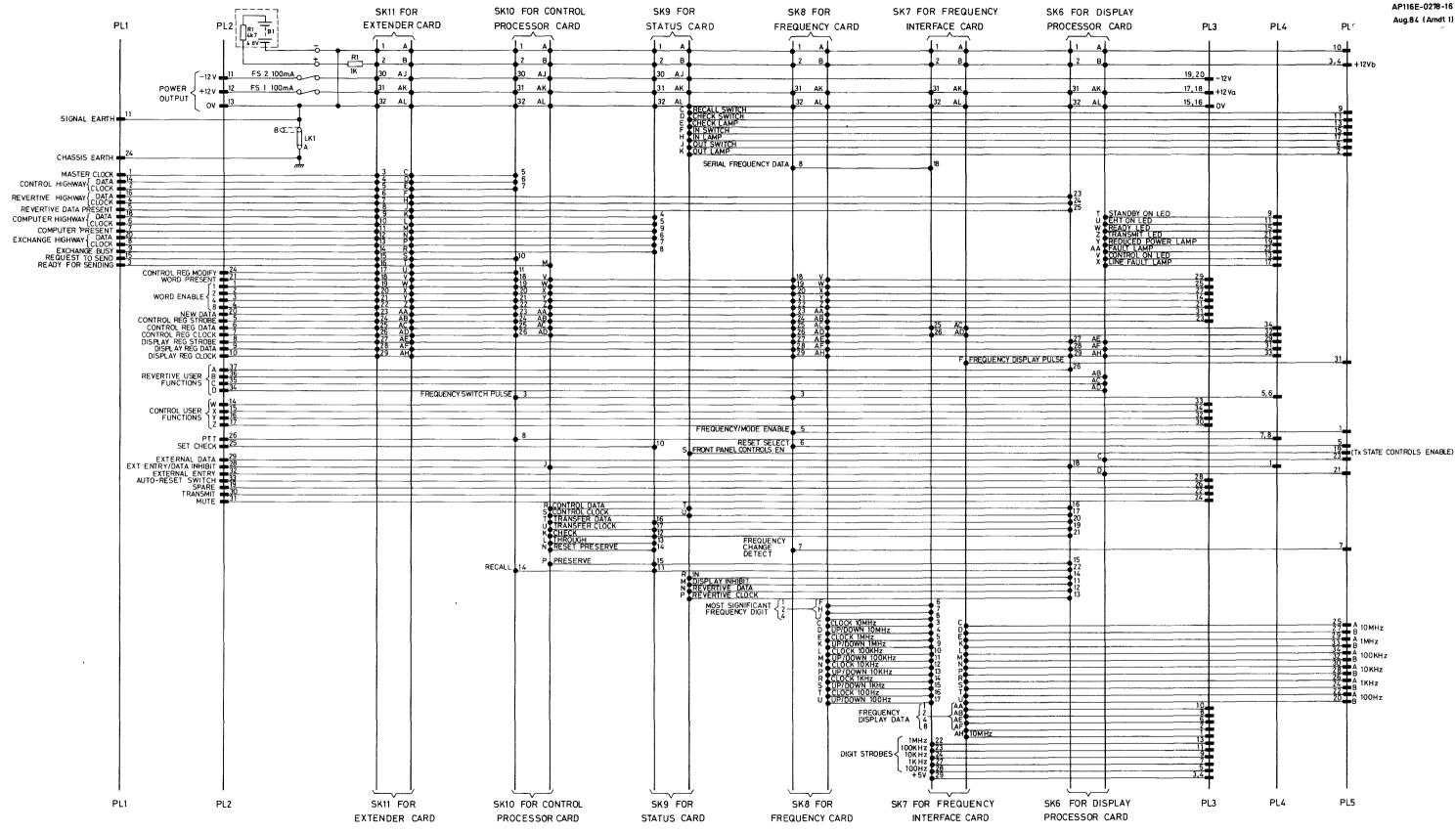

#### AP 116E-0278 -16 Aug.84 (Amdt 1)

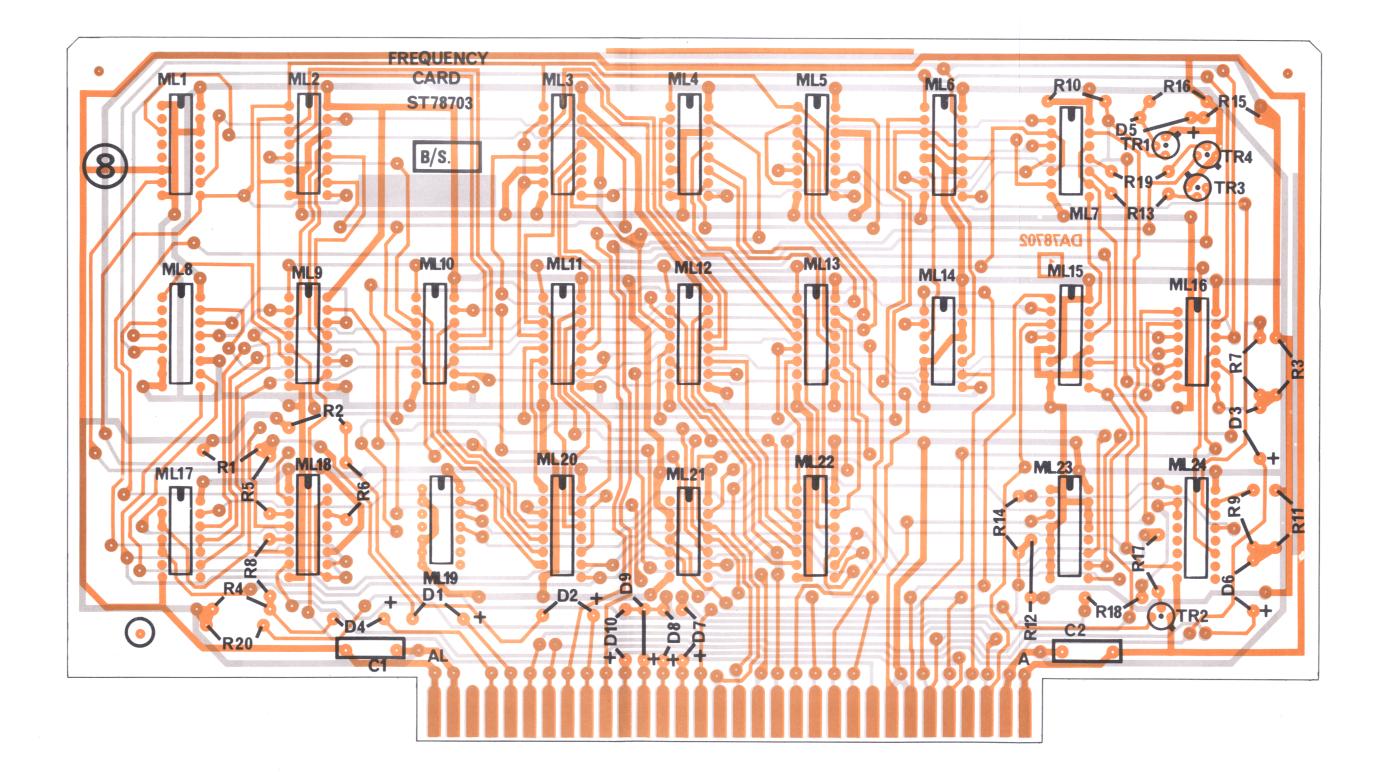

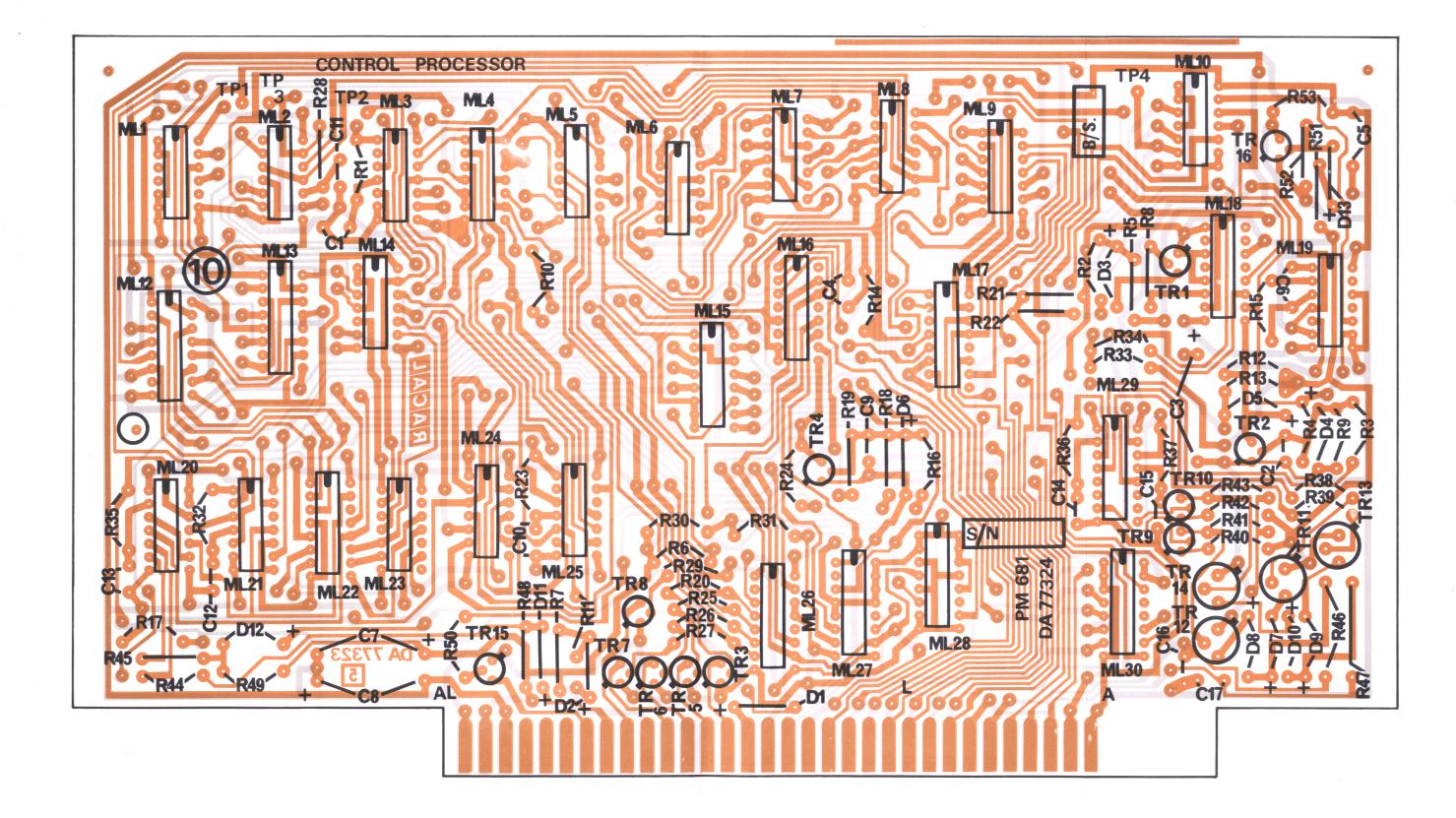

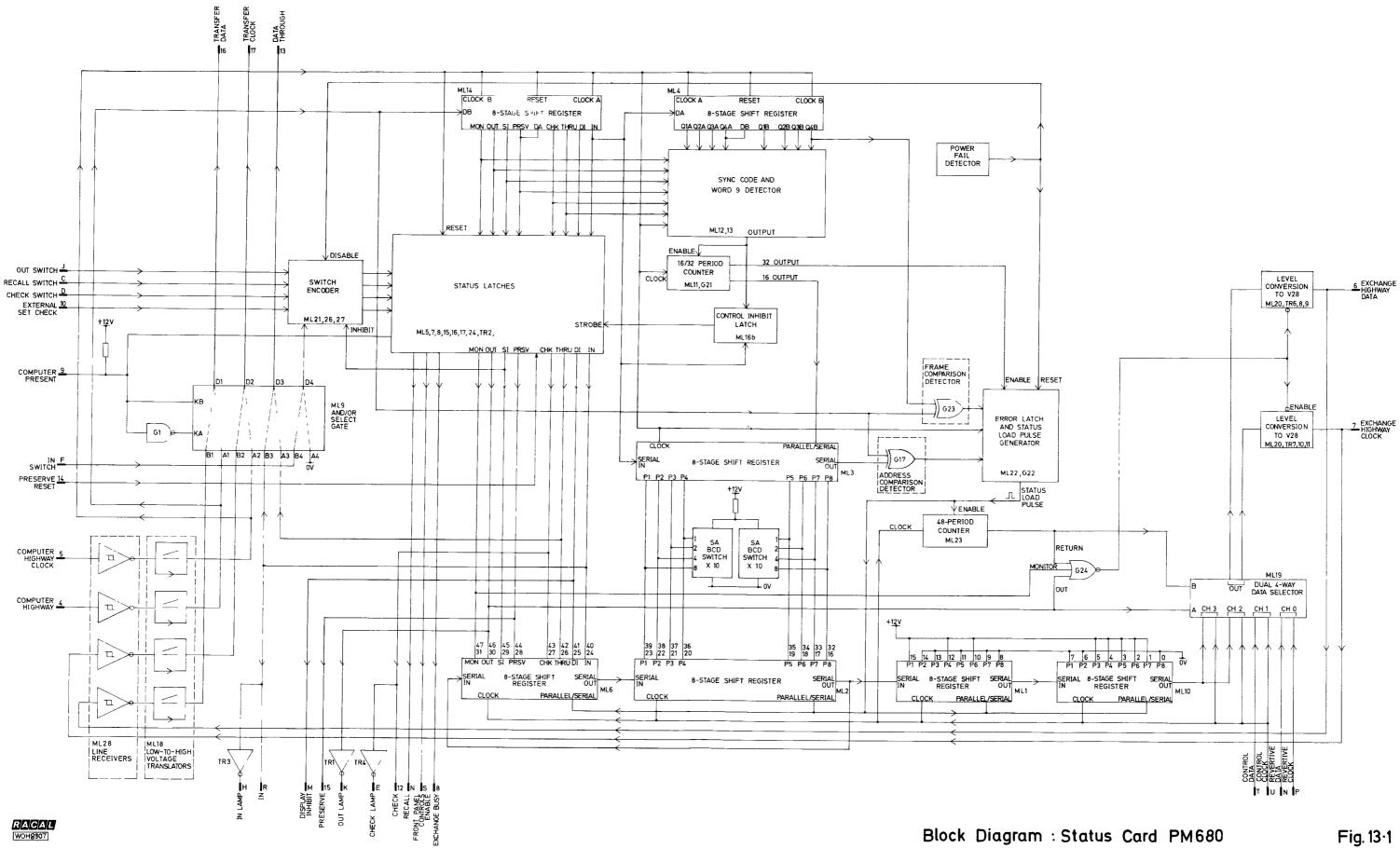

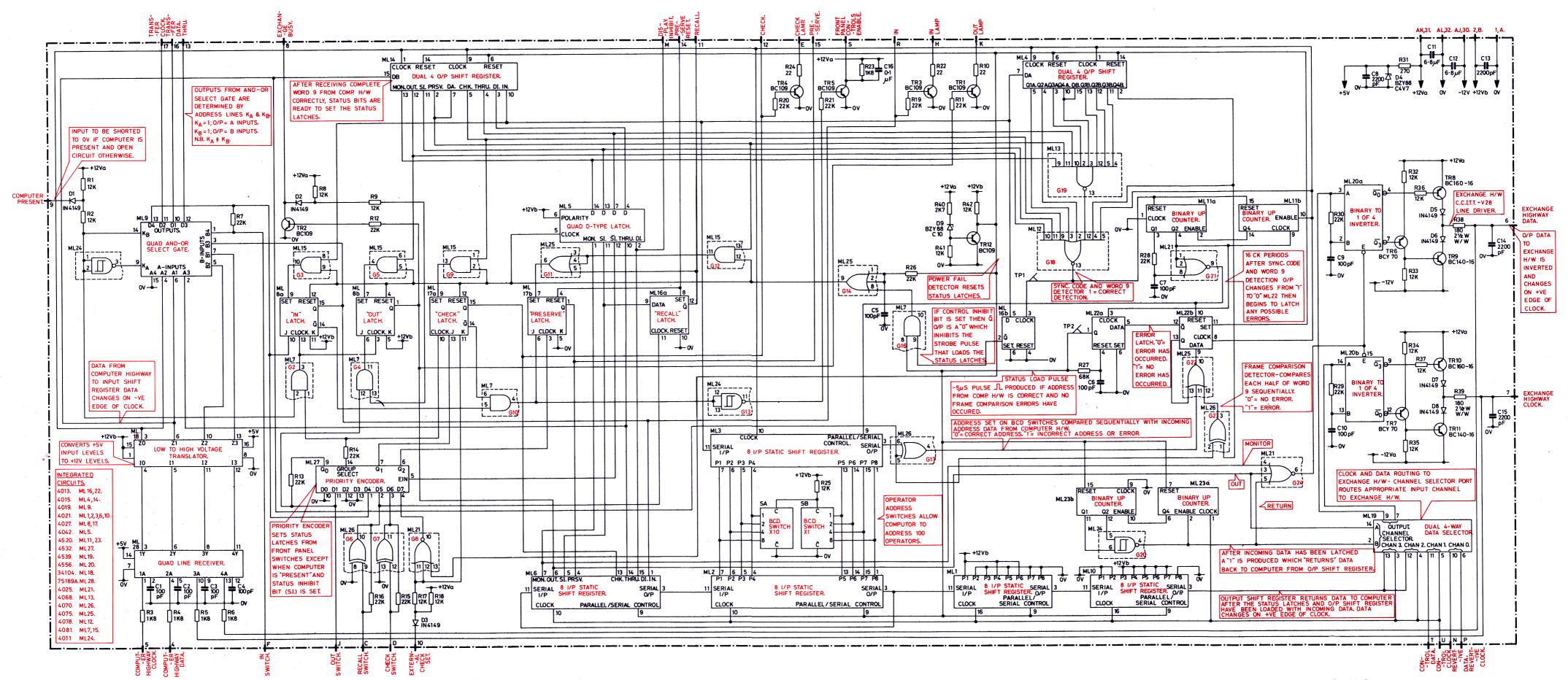

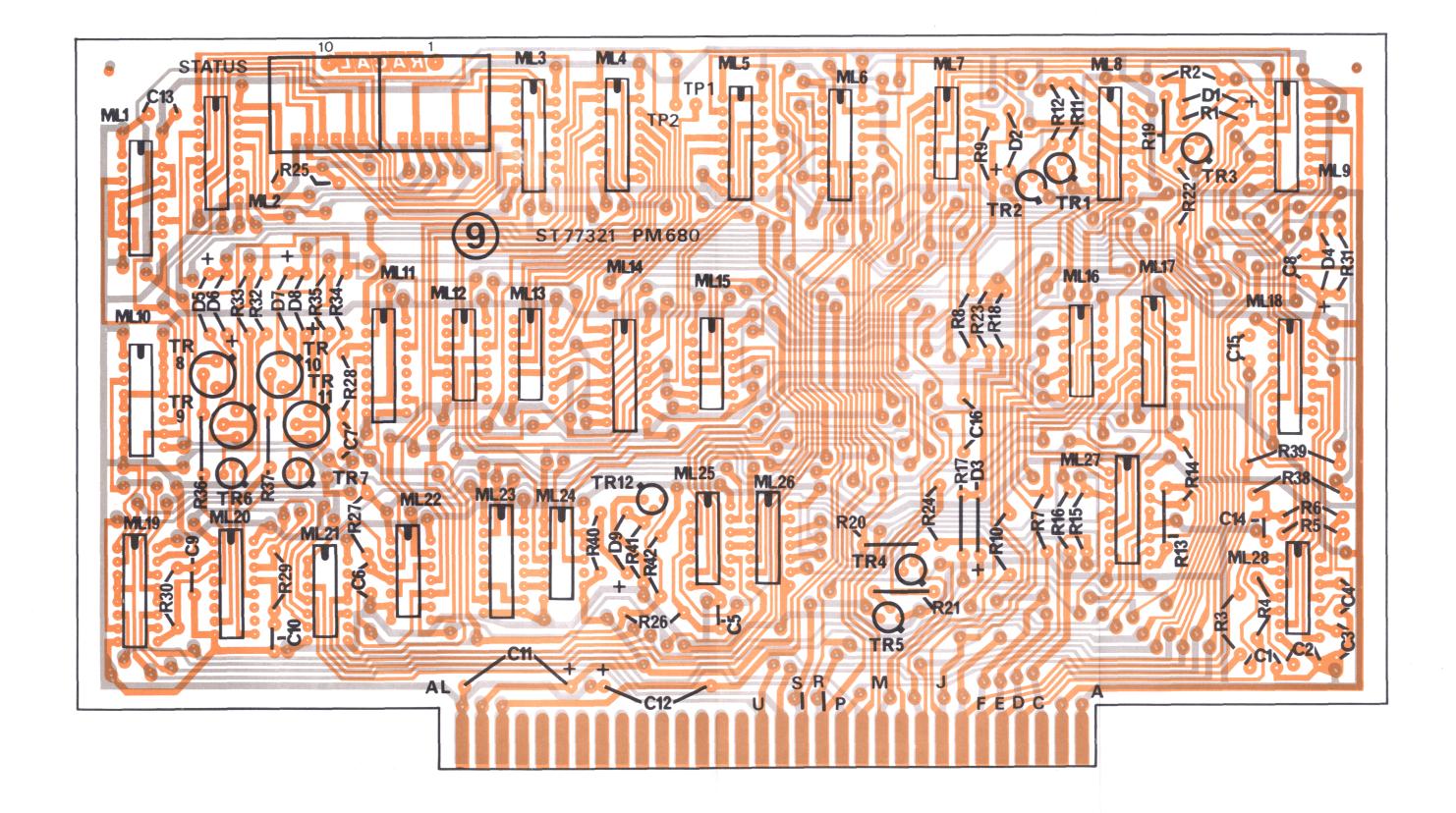

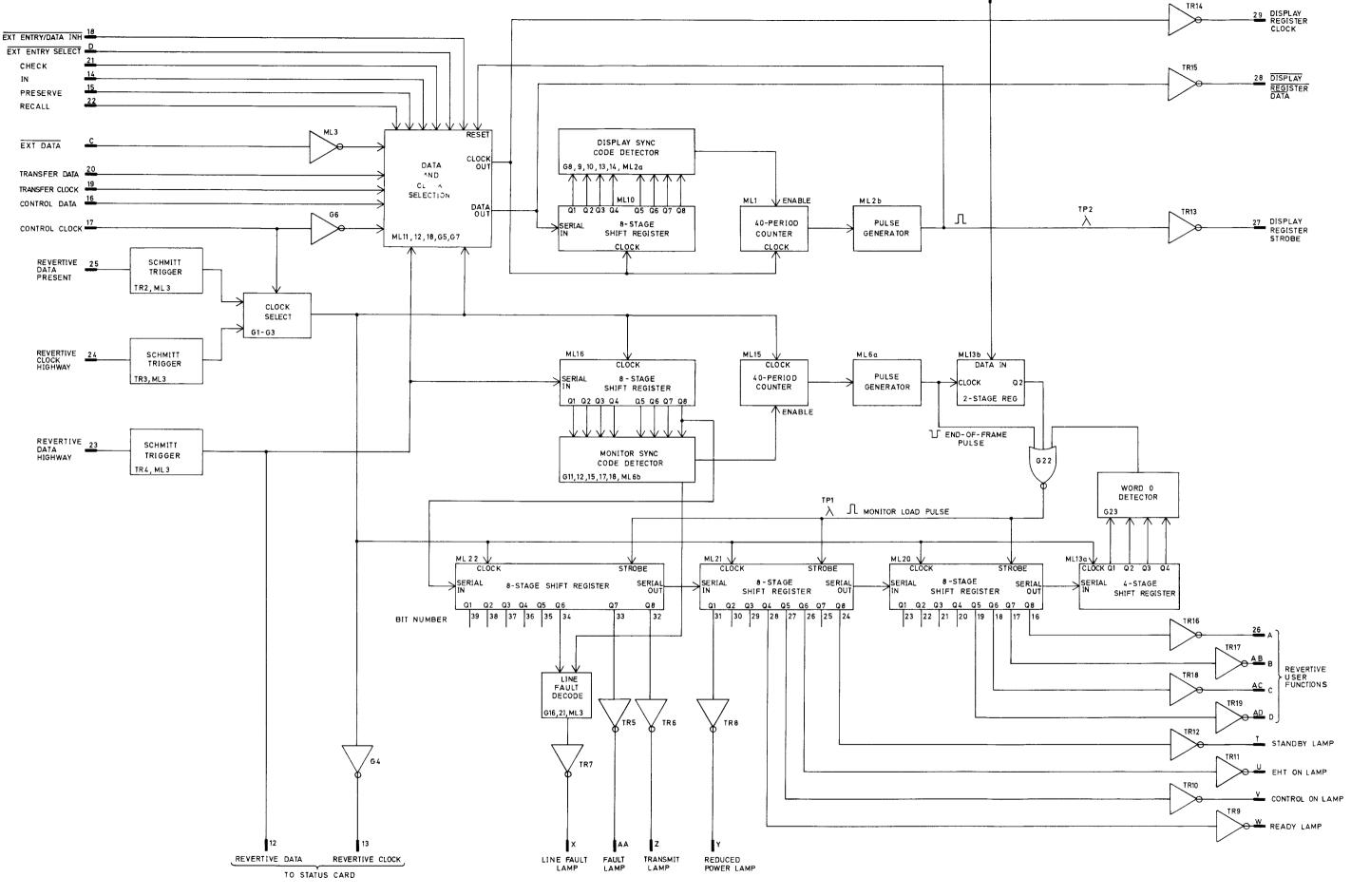

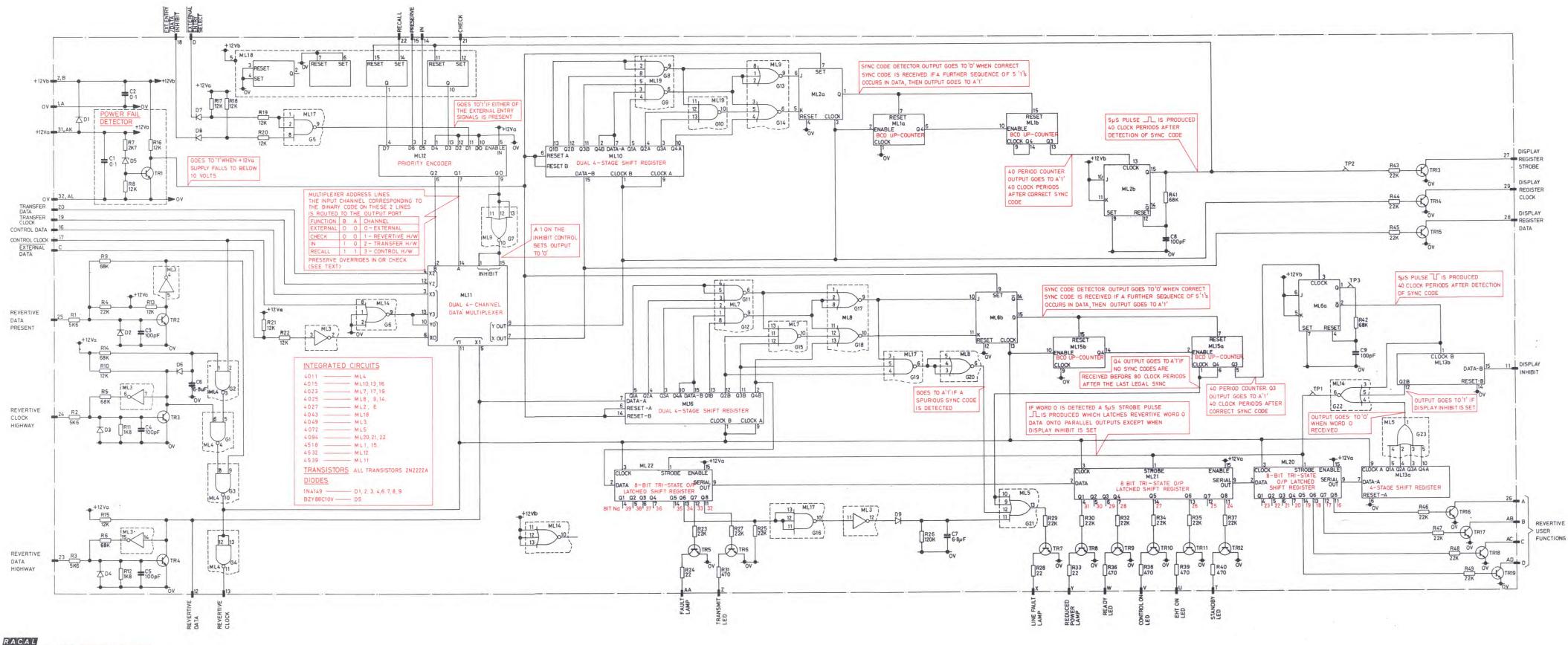

CONTROL PROCESSOR CARD (ST77324)

FREQUENCY INTERFACE CARD (ST78705)

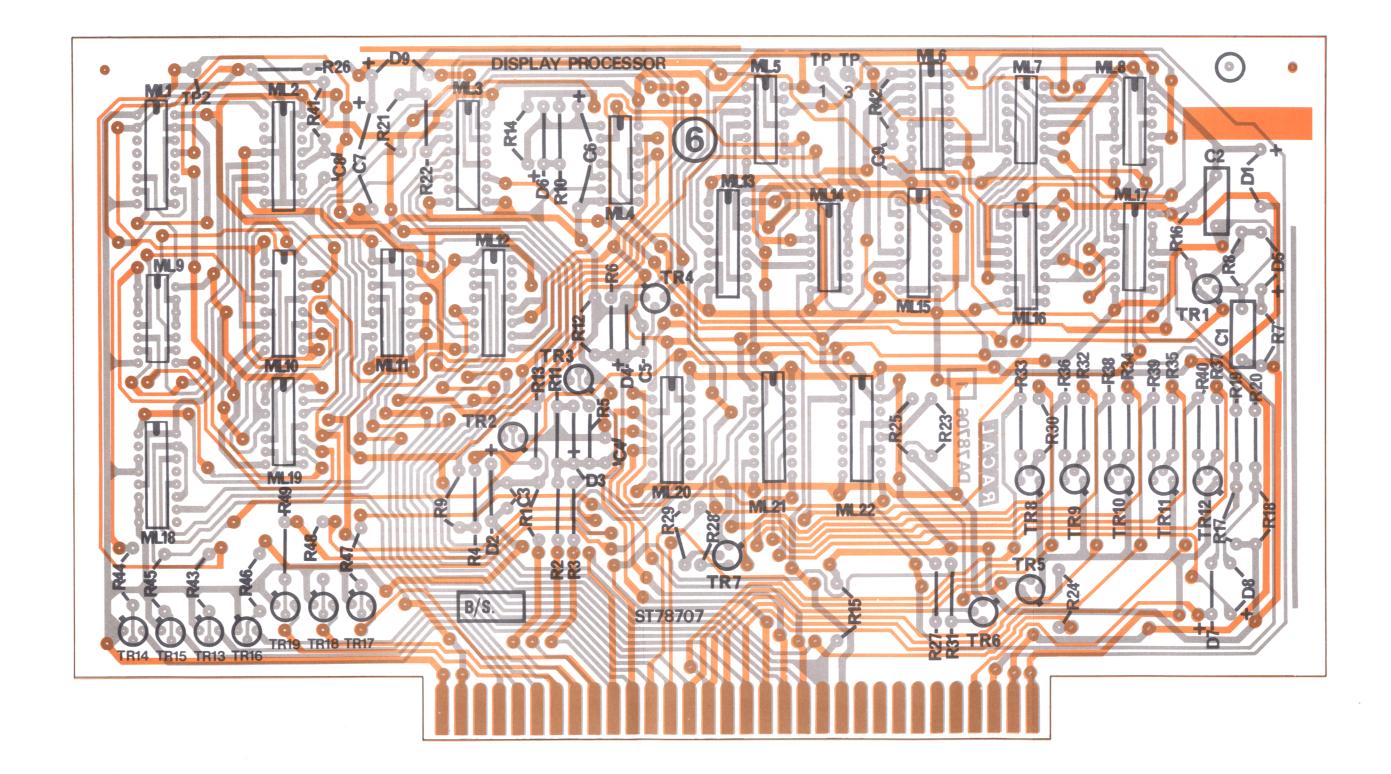

DISPLAY PROCESSOR CARD (ST78707)

## Fig. 2.2

### <u>CHAPTER 3</u>

### OPERATING INFORMATION

#### CONTENTS

|                                     | Para. |

|-------------------------------------|-------|

| INTRODUCTION                        | 1     |

| FRONT PANEL CONTROLS AND INDICATORS | 2     |

#### ILLUSTRATIONS

|              |         | Fig. |

|--------------|---------|------|

| Front Panel: | MA.1090 | 3.1  |

•••

### CHAPTER 3

### OPERATING INFORMATION

#### INTRODUCTION

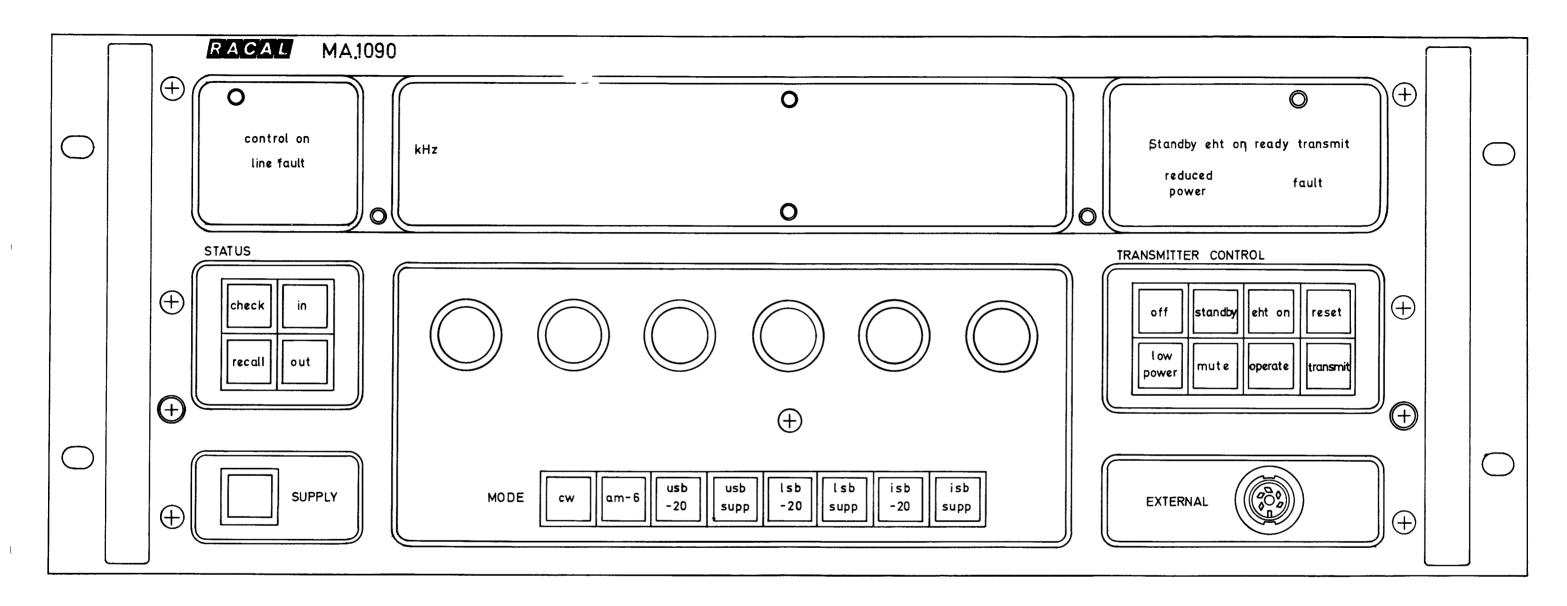

The operating procedures for the MA.1090 are dependent upon the particular installation in which it is employed. This chapter gives a description of each front panel control as a guide to its correct use. A front panel view of the MA.1090 is given in fig. 3.1.

#### FRONT PANEL CONTROLS AND INDICATORS

| 2. | (1) | SUPPLY on/off switch | A mechanically latched push-button switch<br>which illuminates when power is applied to the<br>MA.1090.                                         |

|----|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

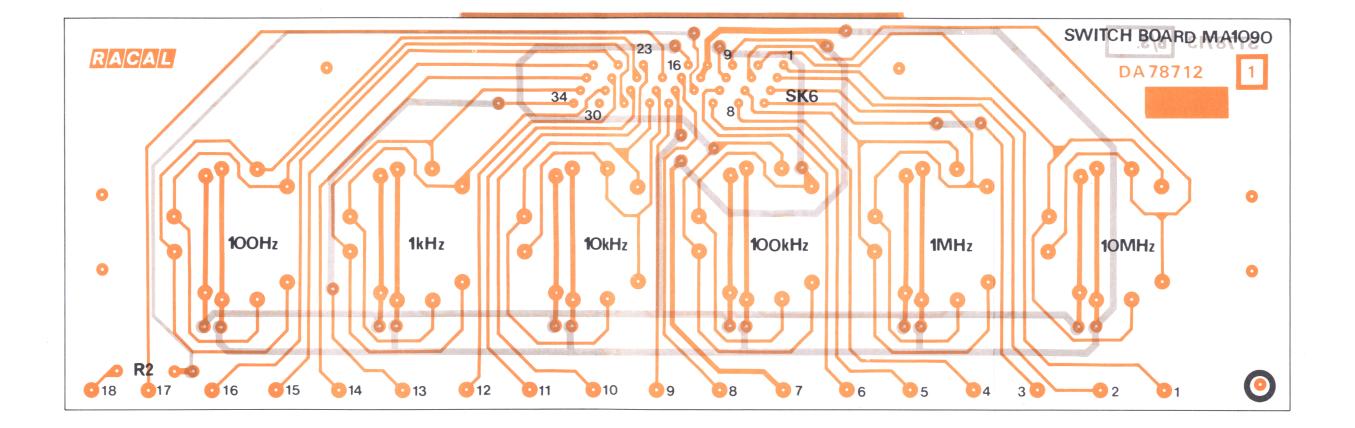

|    | (2) | Frequency Controls   | A bank of six rotary switches is provided for<br>the selection of the operating frequency which<br>is then displayed by the six LED indicators. |

|    | (3) | MODE ~               | Eight illuminated push-button switches are provided for MODE selection, as follows:-                                                            |

|    |     |                      | CM (Selects KEY, LSB, suppressed)<br>AM-6 (Selects USB-6 dB)<br>USB-20<br>USB SUPP<br>LSB-20<br>LSB SUPP<br>ISB-20<br>ISB SUPP                  |

|    | (4) | TRANSMITTER CONTROL  | This section comprises eight illuminated push-<br>button switches as follows:-                                                                  |

|    |     |                      | OFF: Cancels the STANDBY and EHT ON selections.                                                                                                 |

|    |     |                      | STANDBY: Selects the STANDBY condition.<br>Cancels OFF and EHT ON.                                                                              |

|    |     |                      | EHT ON: Selects the EHT ON condition (if applicable) provided STANDBY is already selected.                                                      |

|    |     |                      |                                                                                                                                                 |

**RESET:** Resets the transmitter trip conditions and initiates a tuning sequence.

LOW POWER: Selects the LOW POWER condition; may be cancelled by a second press.

MUTE: Cancels OPERATE and TRANSMIT and mutes the transmitter.

**OPERATE:** Cancels MUTE and TRANSMIT; allows the external PTT (Press-to-transmit) line to control the transmit state of the transmitter.

TRANSMIT: Cancels MUTE and OPERATE, sets the transmitter to the TRANSMIT state.

#### RECALL: A non-illuminated push-button which activates an internal memory to set the control unit to predetermined frequency and MODE settings without affecting the TRANSMITTER CONTROL selection.

CHECK: When CHECK is selected the front panel controls are disabled and the settings are entered into the recall store. The transmitter is interrogated and the settings are returned via the revertive data to illuminate the front panel controls and indicators. A second press cancels the CHECK status and also preserves the settings for subsequent recall (except TRANSMITTER CONTROL).

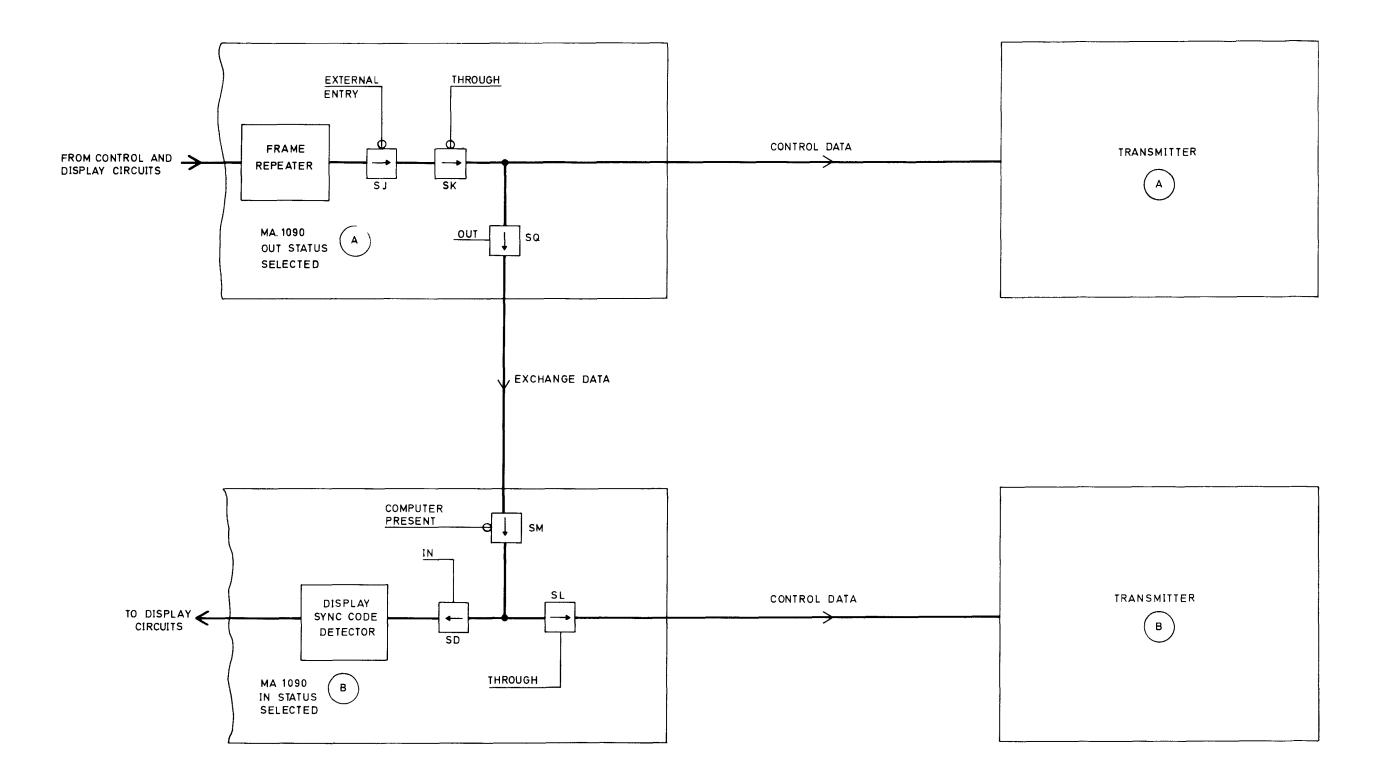

IN: The front panel controls are disabled and the settings are preserved in the recall store. Allows control settings from another MA.1090 (set to OUT) or a computer to be accepted. The IN status may be cancelled by a second press. The former frequency and MODE settings may be recovered by selecting RECALL.

OUT: This allows the control settings to be transferred to another MA, 1090 set to IN.

#### STATUS CONTROLS (5)

#### (6) REVERTIVE INDICATORS

Eight revertively illuminated indicators are provided on the front panel, as follows:-

CONTROL ON: Illuminates in green to indicate that control of the transmitter is available from the MA.1090.

LINE FAULT: Illuminates in red to indicate failure of the control link.

)

)

)

)

١

<u>STANDBY</u> <u>EHT ON</u> <u>READY</u> TRANSMIT Illuminate in green to indicate the state of the transmitter.

<u>REDUCED POWER:</u> Illuminates in amber to indicate a fault condition at the transmitter resulting in reduced output power.

FAULT: Illuminates in red to indicate a fault condition at the associated transmitter.

Provides for the connection of an external unit such as the Racal MA.1083 frequency entry pad.

(7) EXTERNAL socket

## Front Panel: MA.1090

Fig. 3.1

Metric thread cross-head screws fitted to Racal equipment are of the 'Pozidriv' type. Phillips type and 'Pozidriv' type screwdrivers are not interchangeable, and the use of the wrong screwdriver will cause damage. POZIDRIV is a registered trade mark of G.K.N. Screws and Fasteners Limited. The 'Pozidriv' screwdrivers are manufactured by Stanley Tools Limited.

### <u>CHAPTER\_4</u>

### DISMANTLING AND RE-ASSEMBLY

### CONTENTS

|                                  | Para. |

|----------------------------------|-------|

| INTRODUCTION                     | 1     |

| INITIAL PROCEDURE                | 2     |

| REMOVAL OF PRINTED CIRCUIT CARDS | 3     |

| LAMP REPLACEMENT                 | 5     |

| REMOVAL OF FRONT PANEL ASSEMBLY  | 7     |

| REMOVAL OF POWER SUPPLY MODULE   | 8     |

| FRONT PANEL BOARD                | 9     |

| FRONT PANEL REMOVAL              | 10    |

| SWITCH BOARD ASSEMBLY            | 11    |

| DISPLAY BOARD                    | 13    |

| MOTHERBOARD                      | 15    |

#### TABLES

Page

4

Ð

### CHAPTER 4

### DISMANTLING AND RE-ASSEMBLY

#### INTRODUCTION

1. This chapter provides instructions for gaining access to the printed circuits and sub-assemblies of the MA.1090. In general, the re-assembly is the reverse of the dismantling procedure.

#### INITIAL PROCEDURE

- 2. (1) Set the front panel supply push-button switch to off.

- (2) Disconnect all the external cable connectors at the rear panel. (Ensure the sliding locks are released on the multi-way connectors).

- (3) Remove the four screws securing the control unit to the rack or table-top cabinet.

- (4) Withdraw the control unit and place it on a flat clean working surface.

- (5) Remove the top cover plate, held in place with Dzus fasteners.

#### REMOVAL OF PRINTED CIRCUIT CARDS

3. The card guide assembly houses five printed circuit cards and the extender card. A number is printed on the component side of each printed circuit card which corresponds with the number of the mating edge connector mounted on the motherboard. Care must be taken to ensure that a removed card is replaced in the correctly numbered socket (components to the front). The socket numbers for the printed circuit cards are given in Table 1.

| CARD                | CONNECTOR |

|---------------------|-----------|

| Extender            | SK11      |

| Control Processor   | SK10      |

| Status              | SK9       |

| Frequency           | SK8       |

| Frequency Interface | SK7       |

| Display Processor   | SK6       |

#### TABLE 1: PRINTED CIRCUIT CARD SOCKET NUMBERS

4. To remove a printed circuit card lift together the inside edges of the two card extractor levers to disengage the card from its mating edge connector, then lift the card to clear the slots cut into the card guides.

CAUTION: Do not remove or insert a card with the power applied.

#### LAMP REPLACEMENT

The illuminated push-button switches and the monitor indicators (LINE FAULT, REDUCED POWER and FAULT) accommodate a push-in type lamp (Racal No.

929284). A spare lamp is located in the non-illuminated RECALL push-button. To gain access to the monitor indicators, remove the screen and polarising filter (over the frequency display) by releasing the six knurled screws.

6. Using the screen remover located in the spare fuse compartment, place the jaws in the grooves in the opposing vertical faces of the push-button or lamp holder screen and pull out the screen. Remove the unserviceable lamp using the rubber tubing lamp remover supplied.

#### REMOVAL OF FRONT PANEL ASSEMBLY

- 7. (1) Remove the single screw from the underside of the unit securing the front sub-panel flange to the chassis base.

- (2) Remove the four screws, three fitted with a nylon washer and one recessed, fitted with a spring washer, adjacent to each handle.

- (3) The front panel assembly may now be disengaged from the chassis and lowered to rest on the front panel handles. Note that the control panel may be operated for maintenance purposes with the front panel assembly lowered.

- (4) To completely remove the front panel assembly disconnect the three ribbon connectors from PL3, PL4 and PL5 on the motherboard, and the two connectors from the power supply module, SK1 and SK2.

#### REMOVAL OF POWER SUPPLY MODULE

- 8. (1) Remove the front panel assembly (para. 7).

- (2) Remove the single screw through the rear panel adjacent to PL3.

- (3) Remove the six screws, each with a spring washer, securing the module to the chassis base.

- (4) Lift out the power supply module.

### FRONT PANEL BOARD

9. It is necessary to remove the front panel assembly (para. 7) to gain access to the front panel board which is mounted on twelve stand-off pillars. Once the twelve securing screws, each fitted with a flat and a spring washer, are removed, the board may be hinged on the ribbon cables to reveal the switch board, the display board, the front panel push-button switches and the EXTERNAL socket. To completely remove the front panel board disconnect the three ribbon connectors from PL6, PL7 and PL8.

### FRONT PANEL REMOVAL

- 10. (1) Remove the front panel assembly (Para. 7).

- (2) Remove the collet-type frequency setting control knobs as follows:-

- (a) Remove the knob end cap.

- (b) Release the collet nut using an 8 mm socket or ring spanner.

- (c) Remove the knob.

- (3) Remove the single screw (complete with nylon washer) through the front panel above the LSB-20 push-button) attaching the front panel to the front sub-panel.

- (4) Remove the front panel.

#### SWITCH BOARD ASSEMBLY

11. To gain access to the switch board assembly remove the front panel assembly (Para. 7) and the front panel board (Para. 9). To remove the switch board assembly, proceed as follows:-

- 12. (1) Remove the front panel (Para. 10).

- (2) Remove the three screws, each with a spring washer, through the front subpanel, adjacent to the frequency setting switch spindles.

- (3) The switch board assembly may now be raised to hinge on the connecting cableforms.

- (4) To completely remove the switch board assembly note the cableform colours before unsoldering the leads from the board pins.

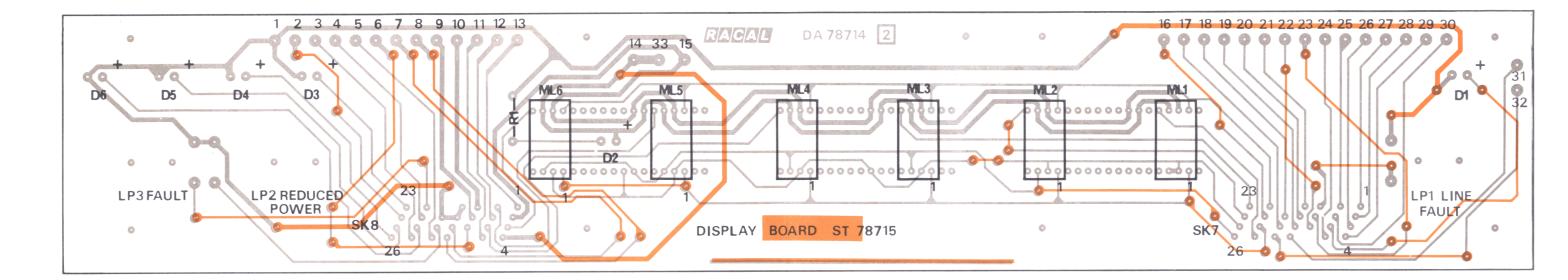

### DISPLAY BOARD

To gain access to six plug-in display integrated circuits, remove the screen and polarising filter attached to the front panel by six knurled screws. To gain access to the display board remove the front panel assembly (Para. 7) and the front panel board (Para. 9). To remove the display board proceed as follows:-

- 14. (1) Remove the front panel (Para. 10).

- (2) Remove the switch board assembly (Para. 12).

- (3) Using a 4BA spanner remove the eight hexagonal pillars, each with a spring washer, securing the display board to the front sub-panel.

- (4) The board may now be raised to hinge on the connecting cableform.

#### MOTHERBOARD

- 15. Should it be necessary to gain access to the motherboard, proceed as follows:-

- (1) Remove completely the front panel assembly.

- (2) Remove the five printed circuit cards and the extender card.

- (3) Remove the six countersunk head screws, three at each side, securing the side members to the rear panel.

- (4) Remove the four domed head screws securing the lower edge of the rear panel to the chassis, and the single screw into the rear face of the power supply module.

- (5) Remove the fourteen screws securing the motherboard and card guide assembly to the base of the chassis.

- (6) The rear panel, motherboard and card guide assembly may now be removed as a complete sub-assembly.

# CHAPTER\_5

# SERIAL CONTROL SYSTEM

### CONTENTS

|                                   | Para. |

|-----------------------------------|-------|

| INTRODUCTION                      | 1     |

| SCORE FORMAT                      | 2     |

| ROUTINE AND NEW DATA              | 5     |

| FRAME COMPARISON                  | 6     |

| PREAMBLE                          | 7     |

| Sync. Code                        | 8     |

| Transmit/Receive                  | 9     |

| Control Inhibit Bit               | 10    |

| Return Monitor Bit                | 11    |

| Address Security Code             | 12    |

| Data Word Ident                   | 13    |

| DATA WORDS                        | 14    |

| WORD 0 - MONITOR                  | 15    |

| User Functions                    | 16    |

| Revertive Indicators              | 17    |

| WORD 1 - FREQUENCY                | 18    |

| WORD 3 - TRANSMIT MODE            | 19    |

| TRANSMITTER CONTROL               |       |

| OFF, STANDBY and EHT ON Selection | 20    |

| RESET                             | 21    |

| Automatic Reset                   | 22    |

| Drive Unit State                  | 23    |

| High/Low Power Selection          | 24    |

| MODE SELECTION                    | 25    |

| USER FUNCTIONS                    | 26    |

| WORDS 8 AND 9 - ADDRESSING        | 27    |

| REVERTIVE DATA                    | 28    |

| Frame Comparison Failure          | 32    |

| Control Inhibit                   | 34    |

| CLOCK CIRCUITS                    | 36    |

| Internal Clock                    | 37    |

| External Master Clock             | 38    |

| SIGNAL-TO-LINE REQUIREMENTS       | 39    |

| Recommendation V24                | 40    |

| Recommendation $V28$              | 41    |

MA.1090

### CONTENTS (Continued)

Para.

| CONTROL WORD GENERATION                 | 42       |

|-----------------------------------------|----------|

| Routine Control Data<br>New Contol Data | 43<br>51 |

| DISPLAY REGISTER DATA                   | 56       |

### TABLES

|          |                   | Page |

|----------|-------------------|------|

| Table 1: | SCORE Data Format | 5-3  |

### ILLUSTRATIONS

|                                                   | Fig. |

|---------------------------------------------------|------|

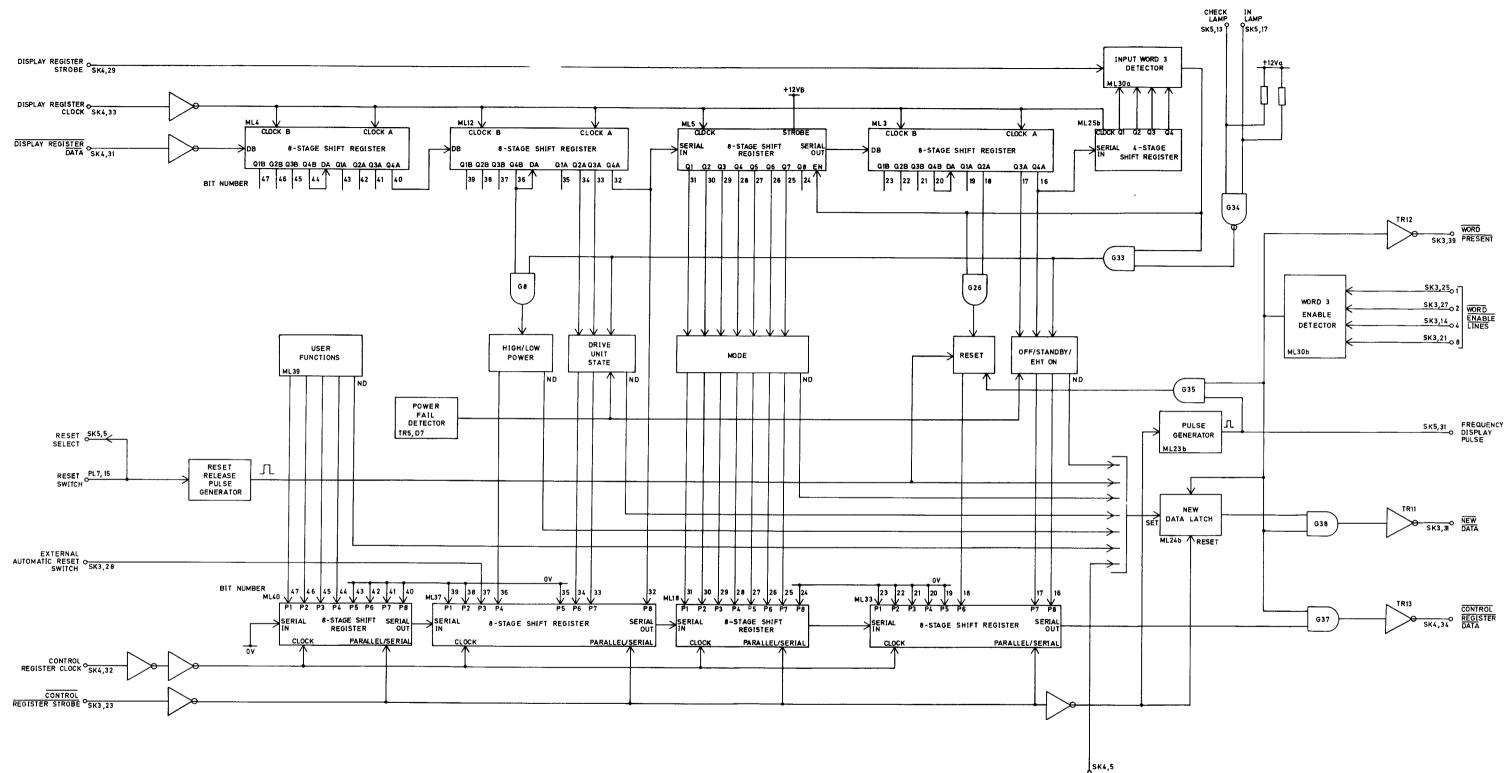

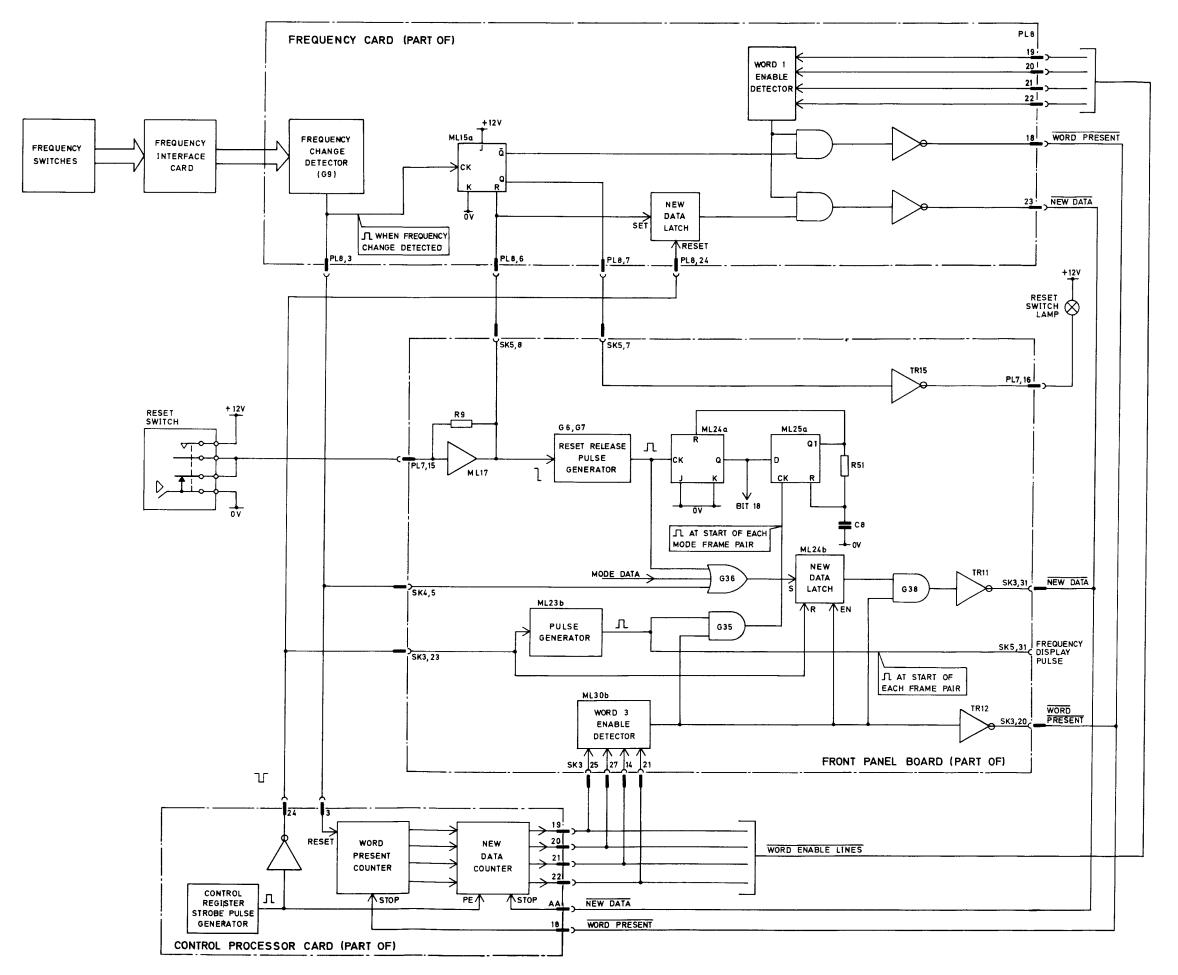

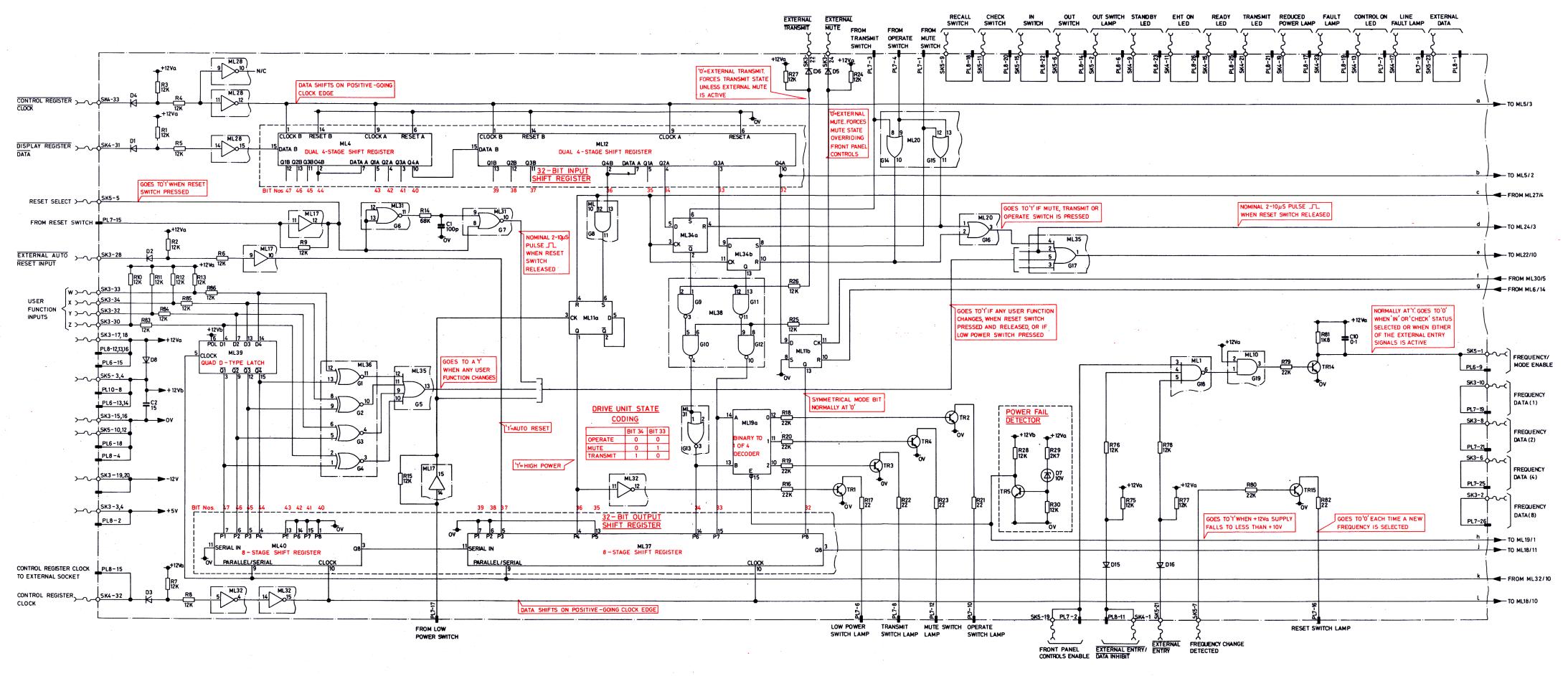

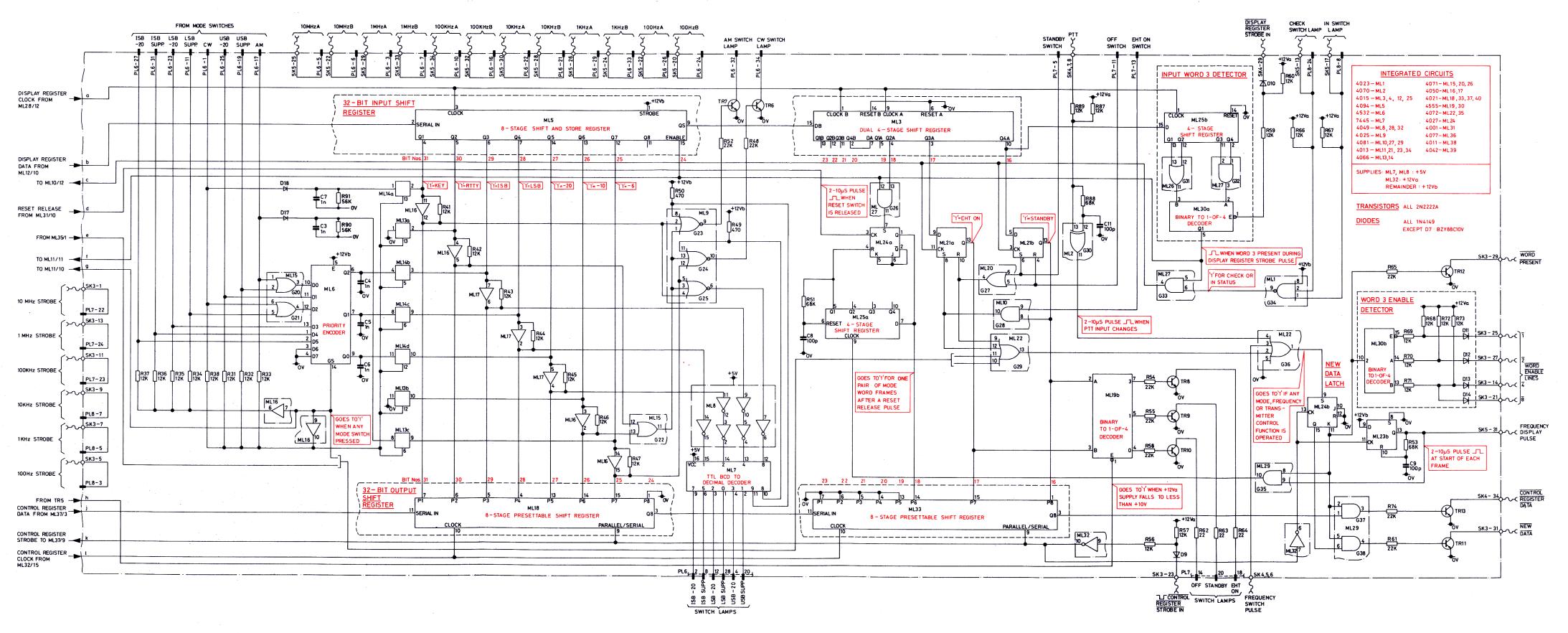

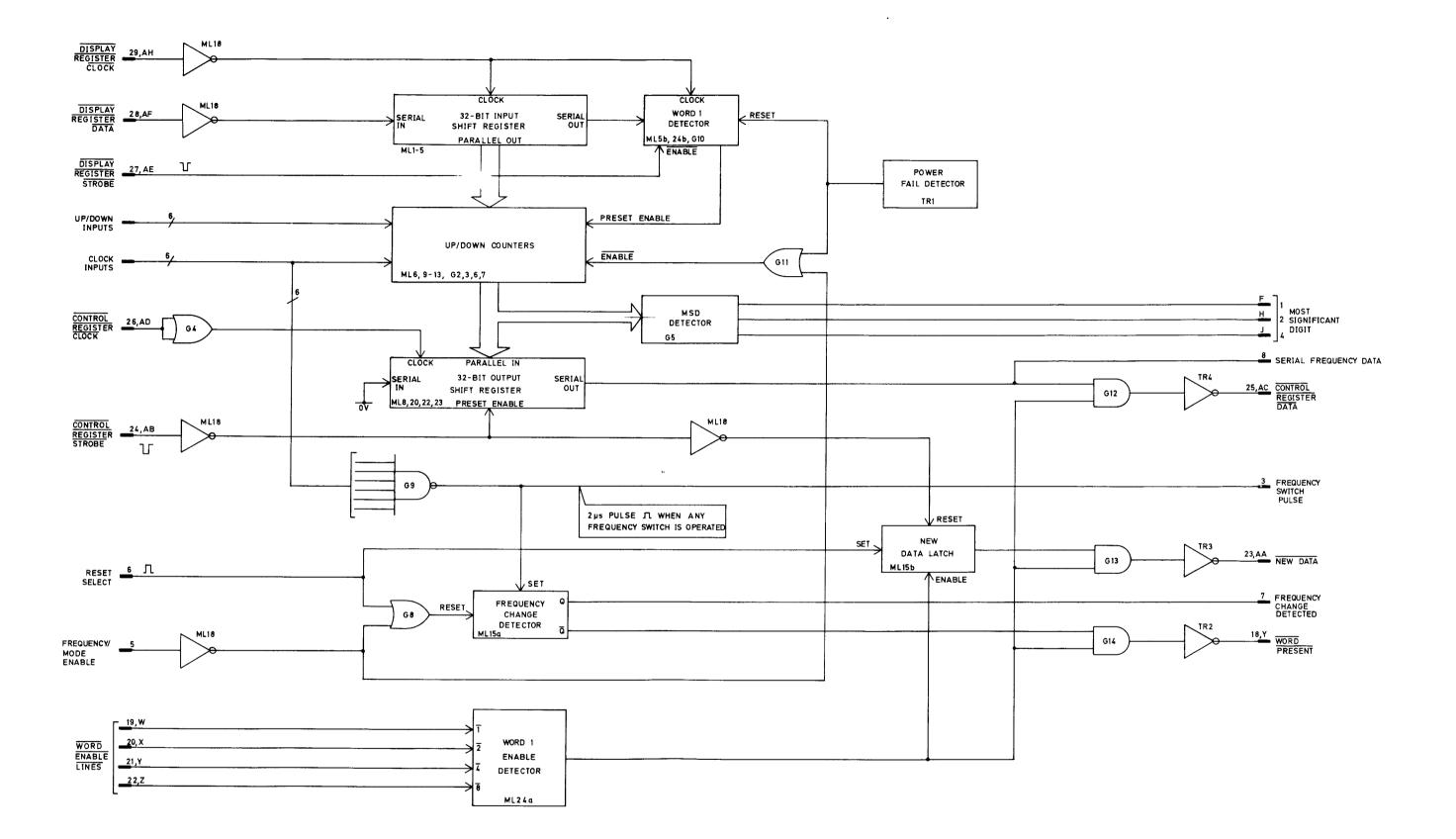

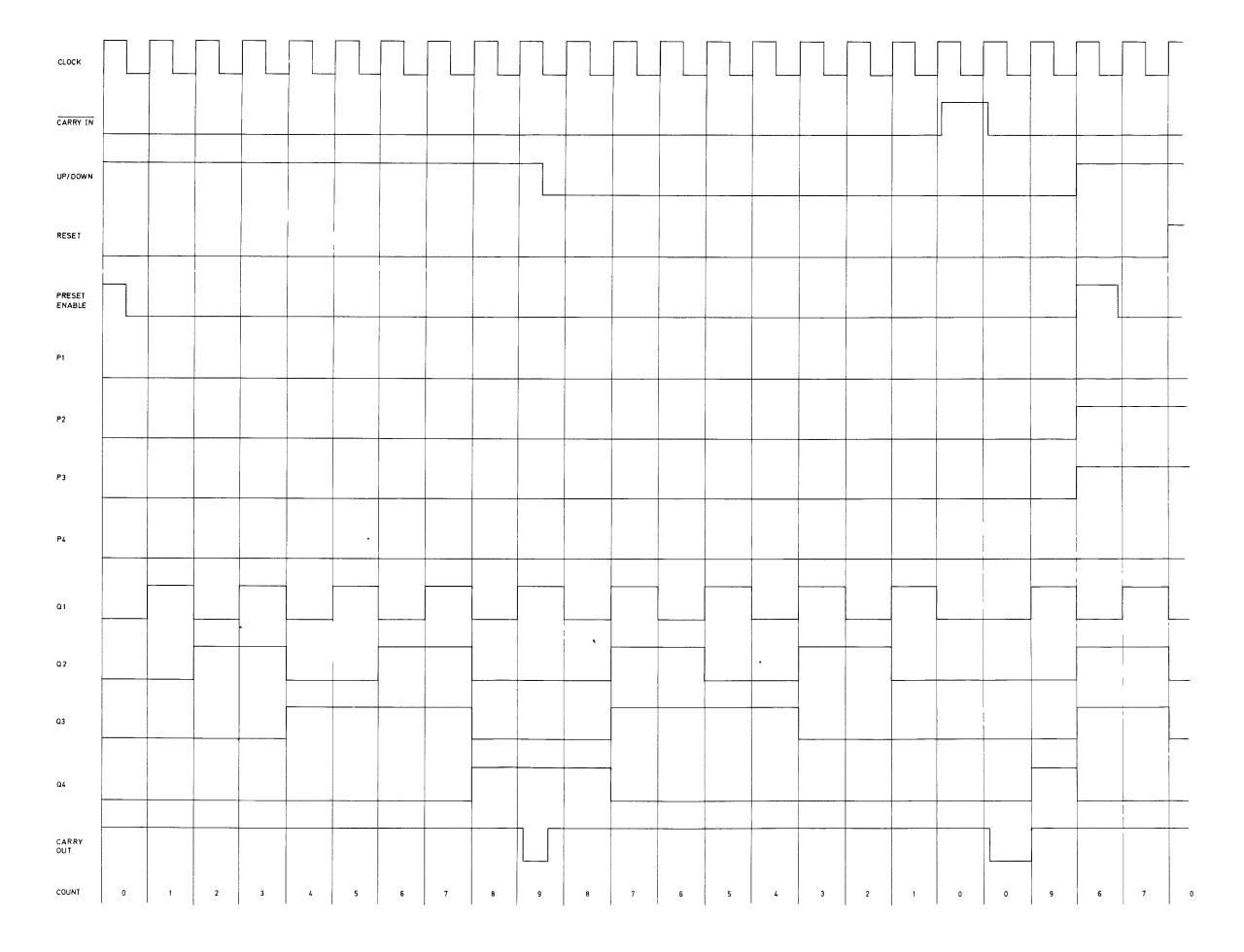

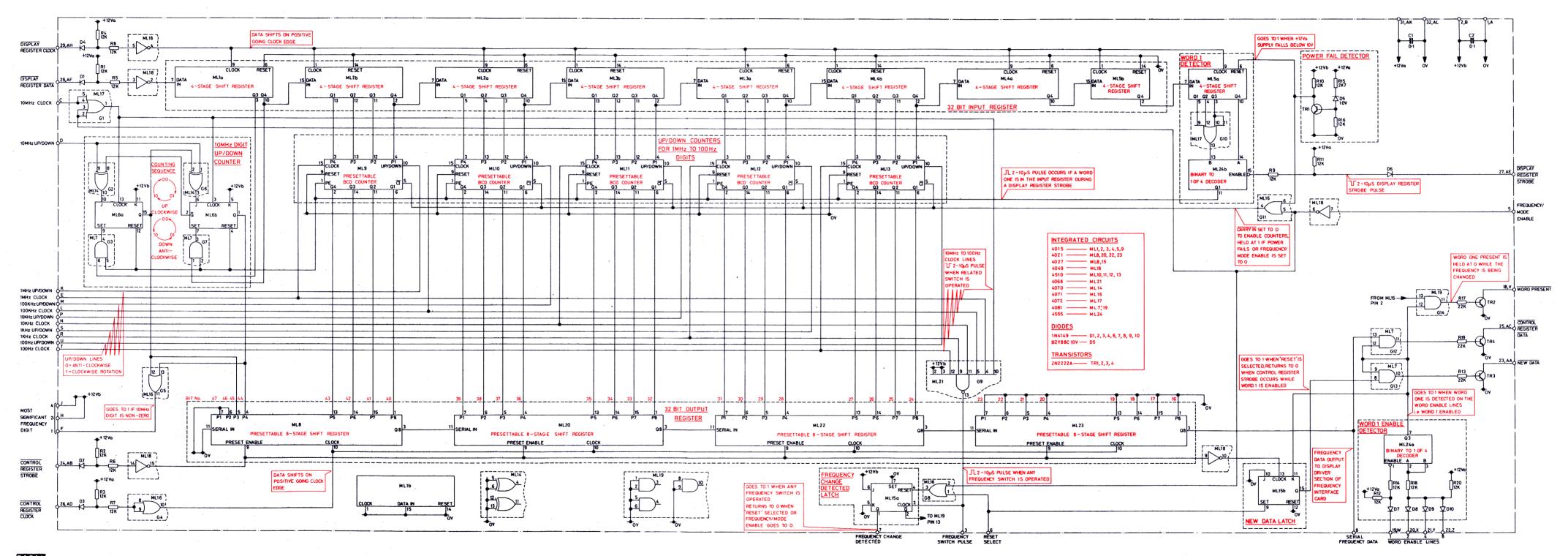

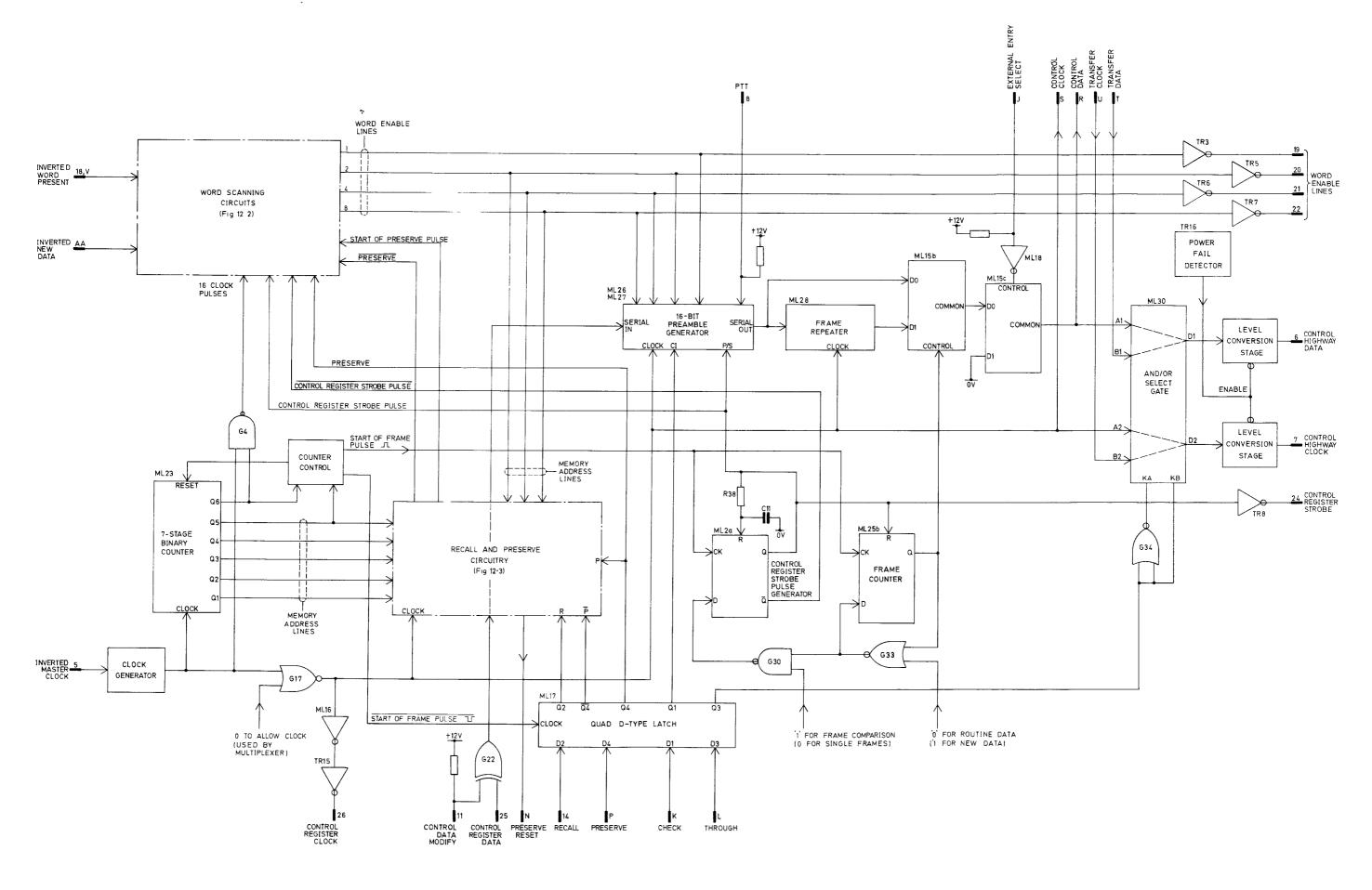

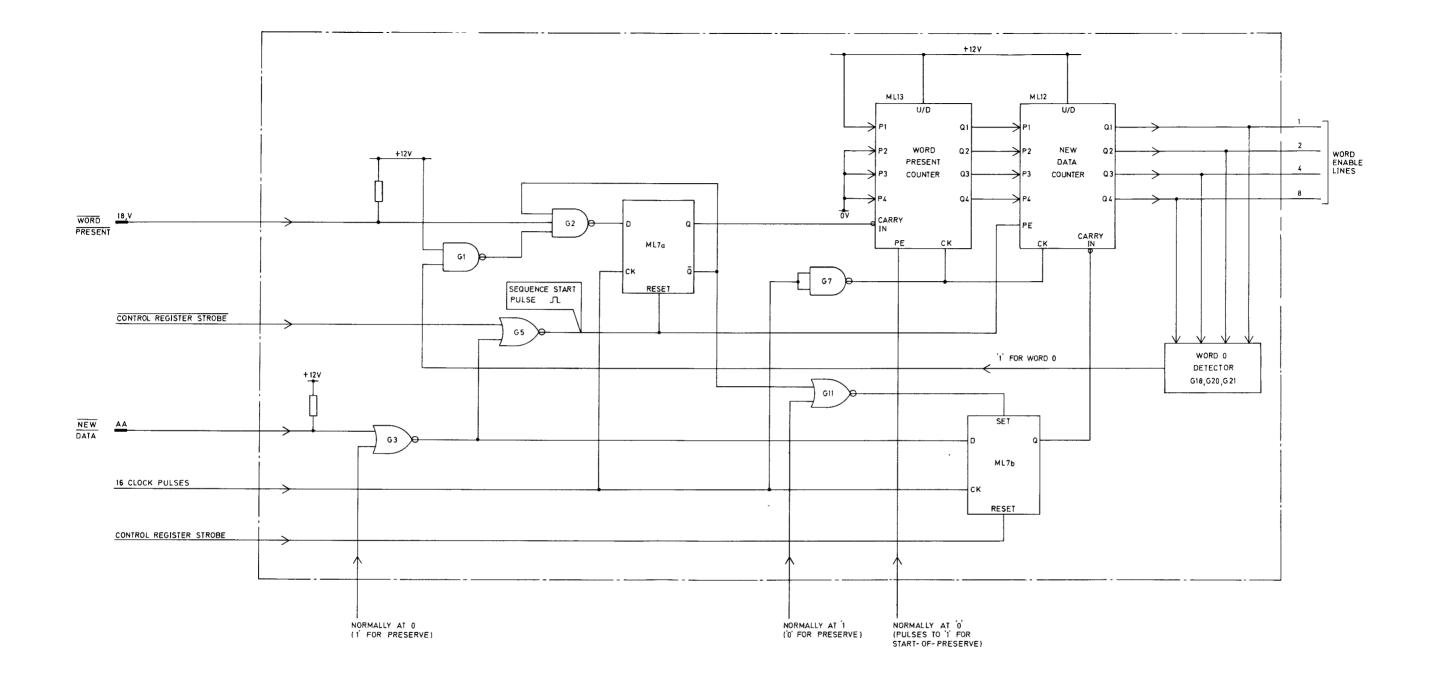

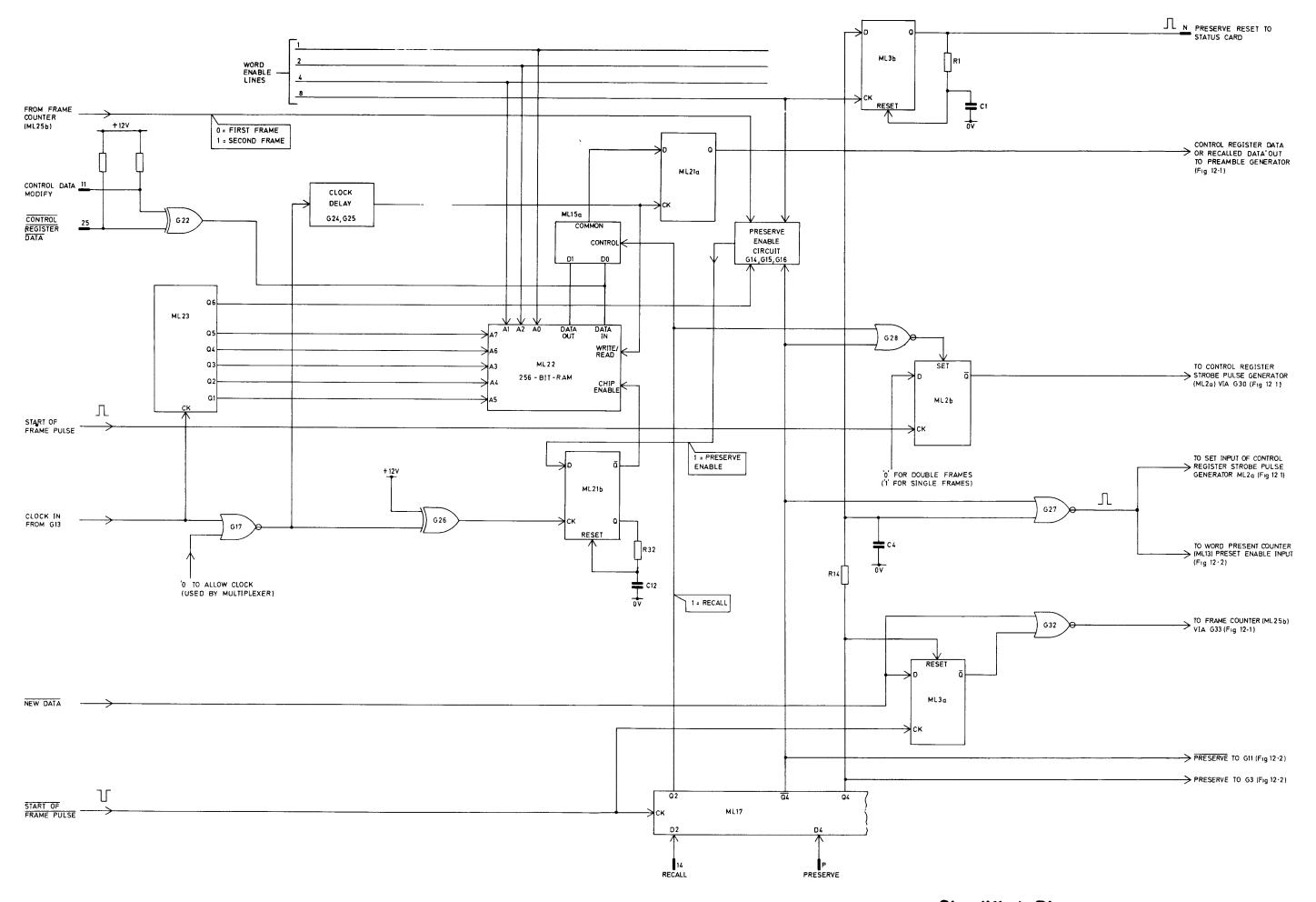

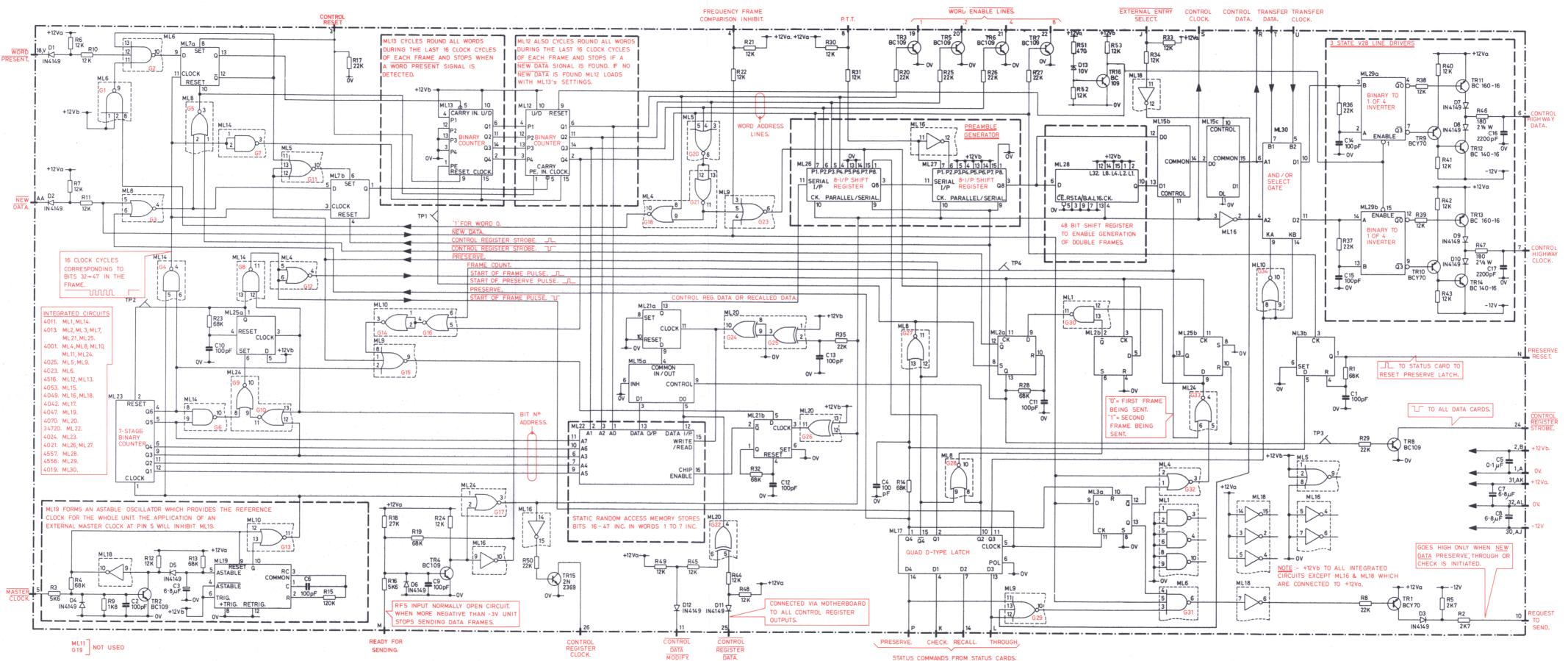

| Simplified Block Diagram: Control Word Generation | 5.1  |

### <u>CHAPTER 5</u>

### SERIAL CONTROL SYSTEM

### INTRODUCTION

1. This chapter describes the SCORE (Serial Control Of Racal Equipment) format, the signal-to-line requirements, and also how the control words are generated.

### SCORE FORMAT

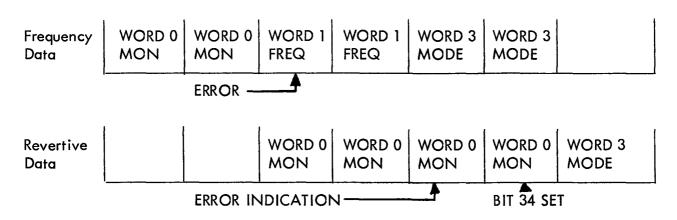

- The SCORE format for serial control is designed to cater for numerous applications and contains ample additional capacity for expansion. It is based on a number of 48-bit synchronous frames, each of which contain a 16-bit preamble (synchronisation, word number identification, etc.) followed by a 32-bit data word. The total capacity of the system is sixteen 32-bit data words, which is equivalent to approximately 400 separate lines. All sixteen words may be revertively checked.

- 3. Separate lines are used for both data and clock signals travelling in each direction. These comply with CCITT V28 and the relevant clauses of V24, and are thus capatible with a wide variety of data modems (see also para. 39).

- 4. The SCORE data format for the control words used by the MA.1090 (word numbers 0, 1 and 3) is given in Table 1. Although word 0 is sent as part of the control sequence, it does not contain any control information and is used only for revertive data. Words 1 to 7 inclusive may be preserved in the internal memory for recall purposes; words 8 to 15 cannot be recalled. Words 2, 4 and 5 have been designated for HF and VHF/UHF Receiver control purposes whilst words 8 and 9 have been designated for equipment and operator addressing purposes (computer assisted installations). This leaves eight undesignated words (6, 7 and 10 to 15), any or all of which are available for expansion of the control system (extra word capability).

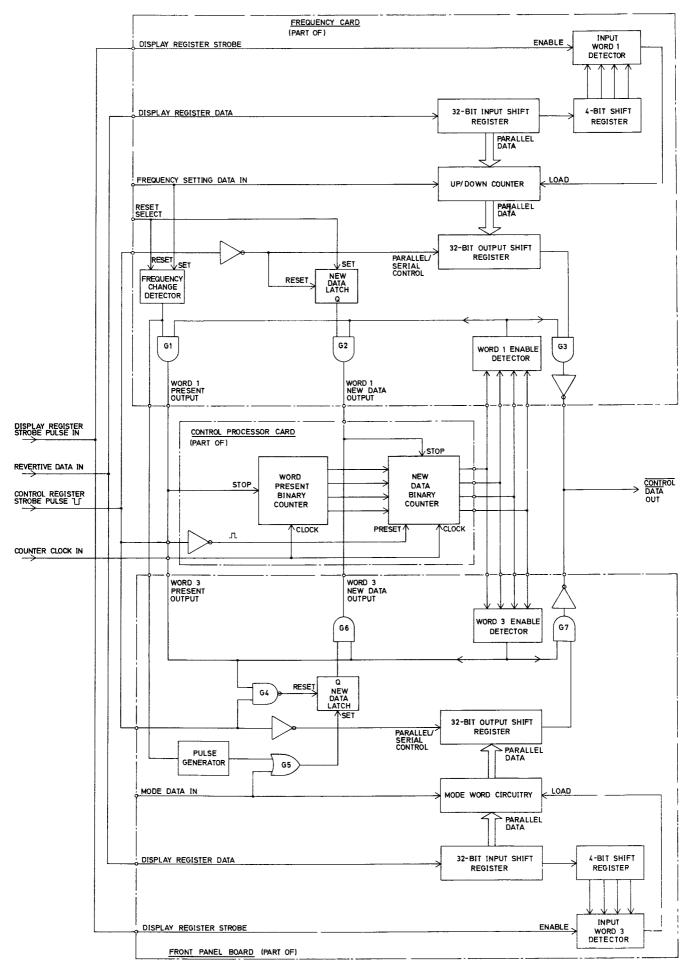

### ROUTINE AND NEW DATA

5. Under static conditions, i.e. when the control data being transferred does not include change-of-function information, 'routine data' frames are sent in a continuous numerical sequence, at a rate determined by the clock frequency. When a change of function is made however, instead of allowing the transfer of the full sequence of frames to occur before the change of function is executed at the transmitter, the next frame to be sent will contain the data word carrying the change-of-function information.' Thus the frames are sent out of numerical sequence and priority is given to those frames containing new data. This is achieved by the use of 'new-data' latches, where a latch is set every time a control setting is changed to indicate that the appropriate word requires transmission. The latch is reset when the new data word is transmitted.

### FRAME COMPARISON

6. Error detection is accomplished (at the transmitter) by the frame comparison technique, which means that two identical frames must be received at the transmitter before a change of function can occur.

### PREAMBLE

7. A 16-bit preamble is added to the front of each 32-bit data word to form one complete 48-bit frame. The preamble contains a 6-bit sync. code, a 2-bit transmit/receive (PTT) code, a control inhibit bit, a return monitor bit, a 2-bit address word security code and a 4-bit data word ident; these are described in the following paragraphs.

### Sync. Code

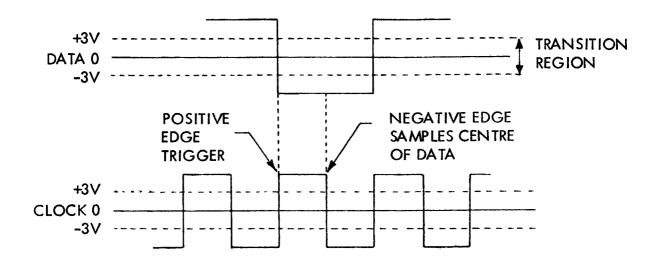

8. The sync. code (bits 0 to 5) consists of a '0' followed by five consecutive '1s'. The maximum number of consecutive '1s' which naturally occur in serial BCD data is four, e.g., BCD7 followed by BCD8; this then makes five '1s' a unique code. For added security, the next two bits of the preamble (used for PTT) may not consist of two consecutive '1s'; this is done to 'terminate' the sync. code and so prevent the generation of a false sync. code following a link break etc.

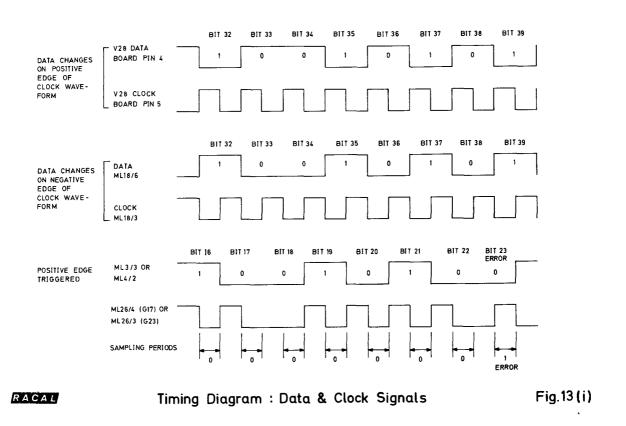

#### Transmit/Receive

9. Bits 6 and 7 of the preamble are used for transmit/receive switching (PTT) where the transmit state may mute a receiver and set the associated transmitter to the transmit condition. As stated in para. 8, these two bits must not consist of two consecutive 'ls'. For the transmit state bit 6 is set to a 'l' and bit 7 is set to '0', whilst for the receive state, bit 6 is set to a '0' and bit 7 is set to a 'l'.

#### Control Inhibit Bit

10. This bit of the preamble (bit 8) is used, as the name implies, to inhibit the control functions of the transmitter. When it is set to a '1', the control settings of the transmitter remain unchanged and further control instructions conveyed by the 32-bit data words are ignored. The revertive data however, is returned to the MA.1090 in the normal way. The control inhibit bit is set to a '1' in the CHECK status.

#### **Return Monitor Bit**

11. The return monitor bit is set to a '0' and is not normally used in transmitter control applications.

| BIT<br>No.                 | BIT FUNCTION (<br>FORCED STATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|