Texas Instruments

## **SBP9989**

# Advance 16 Bit I<sup>2</sup>L Microprocessor

**MICROPROCESSOR SERIES™**

**Data Manual**

Texas Instruments . . . the inventor of the integrated circuit, the microprocessor, and the microcomputer . . . is a leader in the technology that provides electronic sensing, control, computing, and even speech. For additional information on TI's high-technology products contact:

> Military Products Marketing Group Texas Instruments Incorporated P.O. Box 6448, MS 3030 Midland, Texas 79701 (915) 685-7142

> > or

Customer Response Center Texas Instruments Incorporated P.O. Box 225012, MS 57 Dallas, Texas 75265 (214) 995-6611

#### IMPORTANT NOTICES

Texas instruments reserves the right to make changes at any time in order to improve design and to supply the best product possible.

TI cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement

Copyright © 1982 by Texas Instruments Incorporated

## SBP9989 MICROPROCESSOR TABLE OF CONTENTS

| INTRODUCTION                                    | 3    |

|-------------------------------------------------|------|

| The 9900 Family                                 | 3    |

| The SBP9989                                     | 3    |

| KEY FEATURES                                    | 3    |

| DEVELOPMENT SUPPORT                             | 4    |

| AMPL System Advanced Microprocessor             |      |

| Prototyping Lab                                 | 4    |

| Transportable Assembler                         | 4    |

| 12L TECHNOLOGY                                  | 6    |

| COMPATIBILITY WITH SBP9900A SYSTEMS             | 8    |

| Hardware                                        | 8    |

| Software                                        | 8    |

| DEVICES FOR MILITARY TEMPERATURE                |      |

| APPLICATIONS                                    | 8    |

| PIN ASSIGNMENTS AND FUNCTIONS                   | 12   |

| ARCHITECTURE AND TIMING                         | 16   |

| FUNCTIONAL DESCRIPTION                          | 16   |

| Block Diagram                                   | 16   |

| Arithmetic Logic Unit                           | 16   |

| Internal Registers                              | 17   |

| Program Counter                                 | 17   |

| Status Register                                 | 18   |

| Workspace .                                     | 18   |

| Workspace Pointer                               | 18   |

| Context Switching                               | 18   |

| INTERFACES .                                    | 20   |

| Memory Interfaces                               | 20   |

| HOLD, DMA Interfaces                            | 22   |

| Extended Instruction Processor Interface        | 23   |

| Multiprocessor Interlock                        | 25   |

| INTERRUPTS                                      | 26   |

| Interrupt Level 0 — RESET                       | 28   |

| Interrupt Level 2                               | 28   |

| Undefined Op-Code Trap                          | 29   |

| Communication Register Unit Interface           | . 29 |

| Single-Bit CRU Operation                        | 31   |

| Multiple-Bit CRU Operation                      | 32   |

| External Instructions                           | 33   |

| LOAD Function                                   | 33   |

| STANDARD INSTRUCTION SET                        | 34   |

| Terms and Definitions                           | 34   |

| ADDRESSING MODES                                | 35   |

| STATUS REGISTER MANIPULATION                    | 38   |

| INSTRUCTIONS                                    | 40   |

| Dual-Operand Instructions with Multiple Address | sina |

| for Source and Destination Operands             | 40   |

| Dual-Operand Instructions with Multiple Address | sina |

| for Source Operand and Workspace Register       |      |

| Addressing for the Destination                  | . 41 |

| Signed Multiply and Divide Instructions         | 42   |

| Single-Operand Instructions                     | 43   |

| CRU Multiple-Bit Instructions                   | . 44 |

| CRU Single-Bit Instructions                     | . 44 |

| Jump Instructions                               | 45   |

|                                                 |      |

| INSTRUCTIONS (continued                       |      |

|-----------------------------------------------|------|

| Shift Instructions                            | 46   |

| Immediate Register Instructions               | 46   |

| Internal Register Load Immediate Instructions | 47   |

| Internal Register Load and Store Instructions | 47   |

| Extended Operation Instruction                | 47   |

| Return vVorkspace Pointer Instructions        | 48   |

| External Instructions                         | 48   |

| Microinstruction Cycl                         | 48   |

| Instruction Execution Times                   | 49   |

| MACHINE CYCLES                                | 52   |

| ALU Cycle                                     | 52   |

| Memory Cycle                                  | 52   |

| CRU Cycle                                     | 52   |

| 9989 MACHINE CYCLE SEQUENCES                  | 53   |

| Data Derivation Sequence                      | 53   |

| Workspace Register                            | 53   |

| Workspace Register Indirect                   | 53   |

| Workspace Register Indirect Auto-Increment    | 53   |

| Symbolic                                      | 53   |

| Indexed                                       | 53   |

| INSTRUCTION EXECUTION SEQUENCE                | 54   |

| A AB MOVB S SB SOC SOCB SZC SZCB              | 54   |

| ABS                                           | 54   |

| ALANDI ORI                                    | . 54 |

| 8 .                                           | 54   |

| BL                                            | 54   |

| BLWP                                          | 54   |

| C CB COC CZC                                  | 54   |

| CI                                            | 54   |

| CKOF CKIR LREX IDLE RSET                      | 54   |

| CLR · ·                                       | 54   |

| DEC, DECT INC INCA SWPB                       | 54   |

| DIV, DIVS .                                   | 55   |

| ILLOP JUMPS                                   | 55   |

| LDCR,LI,LIMI,LWPI                             | . 55 |

| LOAD INTERRUPT CONTEXT SWITCH                 | 56   |

| LST,LWP                                       | 56   |

| MDV                                           | 56   |

| MPY(signed) .                                 | 56   |

| NEG.,                                         | 56   |

| RESET RTWP                                    | 56   |

| SBO,SBZ,TB                                    | 56   |

| SETO, SHIFTS                                  | 57   |

| STCR                                          | 57   |

| STST,STWP                                     | 57   |

| X .                                           | 57   |

| XOR                                           | 57   |

| XOP .                                         | 57   |

| Leaving a Hold State                          | 58   |

| PROCESSING                                    | 55   |

| POWER SOURCE                                  | 59   |

| ELECTRICAL DATA                               | 60   |

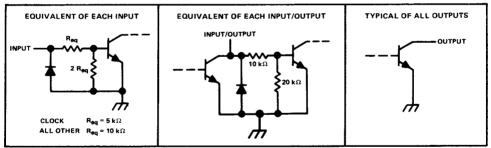

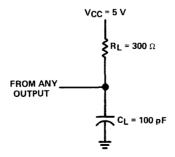

| Input 'Output Structure                       | 60   |

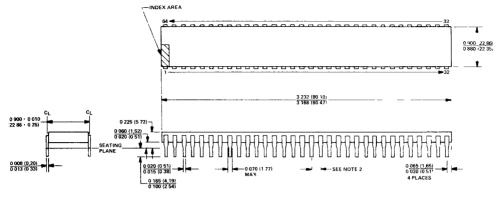

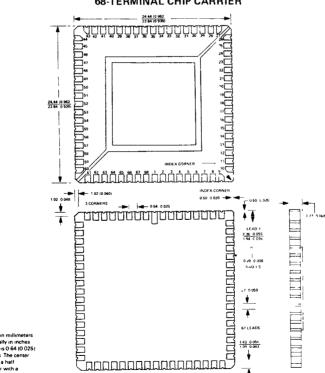

| MECHANICAL DATA                               | 63   |

| MEGHANICAL PATA                               |      |

## INTRODUCTION

#### The 9900 Family

The 9900 Family is a compatible set of microprocessors, microcomputers, microcomputer modules, and minicomputers. It is supported with peripheral devices, development systems, and software and provides the designer with a system solution that has built-in protection against technological obsolescence. The family features true software compatibility, I/O bus compatibility and price/performance ratios which encompass a wide range of applications. The family is designed with a unique flexible architecture to allow technological changes to be easily incorporated while minimizing the impact these changes have on an overall system design

#### The SBP9989 I<sup>2</sup>L 16-Bit Microprocessor

The SBP9989 is a second-generation, bipolar 16 bit microprocessor offering twice the performance of the original SBP9900A. Implemented in TI's Advanced I<sup>2</sup>L Technology, the SBP9989 combines environmental ruggedness and inherent reliability with a 16-bit word length, an advanced memory-to-memory architecture, and a full minicomputer instruction set to extend the end application reach of the Texas Instruments 9900 microprocessor family into those applications requiring efficient, stable, reliable performance in severe operating conditions.

The instruction set of the SBP9989 includes the capabilities offered by full minicomputers and is a superset of the 9900 instruction repertoire. The SBP9989 can be used to upgrade existing SBP9900A systems or to implement new system designs requiring the increased through-put and doubled memory capability.

## **KEY FEATURES**

The SBP9989 is downward-compatible with all of TI's existing microcomputer and minicomputer products and employs the advanced, memory-to-memory architecture that ensures optimal performance in the structured, I/O-intensive applications of the 80's.

- Memory-to-memory architecture

- <u>73 basic instructions</u> include all 69 instructions of the SBP9900A plus Signed Multiply, Signed Divide, Load WP, and Load ST. The signed multiply and divide instructions allow significant improvements in system through-put in numerical applications, while load workspace register and load status register are essential to the efficient implementation of advanced operating systems.

- <u>User extension to the basic instruction</u> set allows undefined op codes to be assigned meanings during system

design. The processor detects undefined op codes in an instruction stream and allows either software interpretation

and execution of the code or hardware execution in special, user-designed "attached processors". Coordination

between the SBP9989 and its attached processor is achieved via a new input signal to the microprocessor

designated XIPP (External Instruction Processor Present).

- Direct access to 128 kilobytes of memory from the SBP9989 is provided by a new output signal designated MPEN (Memory Map Enable) which can be used directly as an additional address bit from the processor. This bit is represented in the processor Status Register as Status Bit 8, which may be manipulated by the user to allow access to two 64-kilobyte pages of memory. MPEN can also be used with the SN54LS610 Memory Mapper to allow access to as much as 16 megabytes of memory. All traps cause Status Bit 8 to be forced to zero during a context switch, ensuring consistent interrupt operation and full software and hardware compatibility with other TI products.

- <u>Multiprocessor system features</u> allow coordination between several processing elements that must share memory and other resources. These features include:

MPILCK (Multiprocessor Interlock), a new output signal that allows a processor to secure and hold a system resource against possible access contention with other processing elements.

INTACK (Interrupt Acknowledge), a new output signal which allows the SBP9989 to acknowledge the presence of an interrupt during those times when it may not have control of the system resources.

XIPP (Extended Instruction Processor Present), a new input signal that establishes a protocol for orderly transfer of bus control between host and slave processors that share memory resources.

LOAD WP and LOAD ST (Load Workspace Pointer and Load Status Register) instructions that allow the SBP9989 to capture a complete software context from an external source.

- Fully static design allows the SBP9989 to be clocked up to 4.4 MHz, or single stepped. The TTL-compatible I/O permits any standard logic and memory devices to be used.

- Simplified clock requirements consist of a single-phase clock with a 50% duty cycle

- Improved microcode within the processor enhances the efficiency of the SBP9989 over its predecessors. Micro

cycles were removed from more than half of the instructions, resulting in a 15% to 20% improvement in operating efficiency.

- Fully implemented 16-bit status register with Arithmetic Overflow Interrupt trap.

- Improved external instruction, utilizing five address lines, provides a total of 160 forms available to the user.

- Improved HOLD and WAIT interfaces.

- Implemented in Advanced I<sup>2</sup>L... a proven bipolar technology for high-reliability applications.

The single most important feature of the SBP9989, and all of TI's microprocessors, is its memory-to-memory concept. The user has access to an unlimited number of effective registers, and may completely change register context (an operation equivalent to sixteen push and sixteen pop stack operations in a conventional registered architecture) in just five memory cycle times. The ability to change register context rapidly becomes of prime importance in systems that rely on multiprocessor architectures and high-level languages for efficient software. Trends which will gain momentum as embedded computer applications become increasingly more complex.

#### DEVELOPMENT SUPPORT

#### AMPL System Advanced Microprocessor Prototyping Lab

The AMPL System is a complete set of software and hardware tools that maximize software productivity for the 9900 family. It includes a video display terminal, multiuser hard disk or floppy diskette options, and extensive software Programs can be edited, assembled, loaded, and executed with easy self-prompting commands.

The AMPL System supports software development as well as in-circuit emulation for existing 9900 family CPU's. The logic state trace capability features interactive on-line control and analysis to provide fast data reduction, and programmable emulation control based on the result of this analysis. The high-level language has designed-in features to simplify orientation for the new user while providing extensive flexibility and support for the experienced user.

PROM programming implements target-system memory in PROM and EPROM while the AMPL interactive process makes it easy to identify and implement needed design changes.

#### Transportable Assembler

The SBP9989 is supported by a transportable general assembler (TI part numberTMAM4015). This assembler allows the use of symbolic instructions and assembler directives supporting the full instruction set. The 9900 family instruction set is composed of a base set of 69 instructions plus extensions peculiar to each CPU which provide the input and output manipulation comparison of words and bytes, and ASCII-character data This product can be executed in TI 990, IBM, or DEC environments

## **12L TECHNOLOGY**

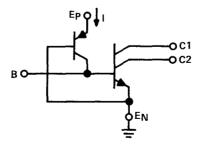

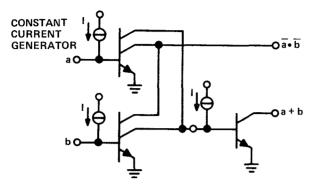

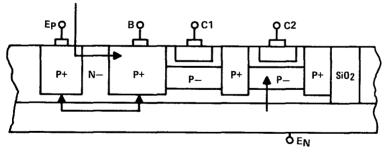

$1^{2}L$  is an integrated-injection circuit logic where current steering is used to control gate switching levels. A lateral PNP transistor is used as an injector to supply base current to the vertical NPN transistor as shown in the figure. The NPN actually serves as the gate that is controlled by placing either a high or low voltage on the base that steers the injector current into or out of the NPN base.

I<sup>2</sup>L technology provides inherent advantages to the user when compared to other technologies.

## o -55°C to +125°C Temperature Range

Circuits are designed to operate over the full military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C rather than just being selected by screening. This provides added design margin that enhances system reliability.

#### o Low Power Consumption

The SBP9989 dissipates less than 0.75 watts, depending upon the state of the I/O's.

#### o Radiation Hardness

Also inherent with  $I^{2}L$  as used on the SBP9989 is tolerance to radiation. Its tolerance to transient upset is among the best observed on LSI parts while the simplicity of the process eliminates latch-up.

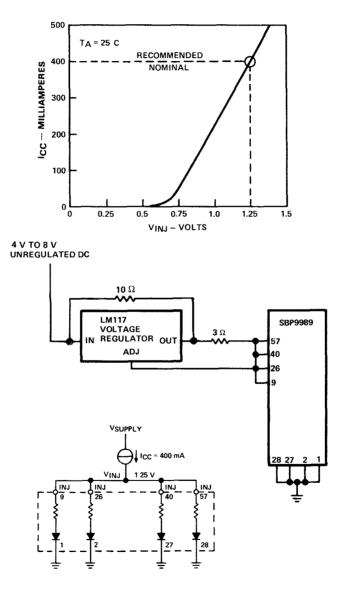

#### o Low Internal Stress Voltage

High internal voltages have been eliminated with  $I^{2}L$ , thereby assuring further gains in reliability. The 5,000 internal gates of the SBP9989 are stressed only with the VINJ, which is typically 1.2 volts. Only the inputs and outputs are exposed to high stress voltages.

## o High Reliability

The SBP9989 has been designed, fabricated and 100% screened with processes to assure the highest levels of reliability. Each part is individually identified to assure traceability

I<sup>2</sup>L CIRCUIT SCHEMATIC

I<sup>2</sup>L LOGIC GATES

,

~

#### COMPATIBILITY WITH SBP9900A SYSTEMS

The SBP9989 is pin for pin compatible with the SBP9900A except for 4 new I/O controls ( $\overline{(MPEN)}$ , INTACK, MPILCK and  $\overline{XIPP}$ ) assigned to pins that were not used on the original device. The modifications required to plug an SBP9989 into an existing SBP9900A socket are listed below.

#### Hardware

- o Deactivating XIPP (tie Pin 58 to VCC through a pull up resistor)

- Provision for an increase in injector voltage to 1 25 V and a reduction in injector current to 400 mA

- o Verifying that Pin 25 (MPEN), Pin 37 (INTACK), and Pin 39 (MPILCK) are open or grounded

- o Interrupt lines sampled during hold and non hold states

- Verifying fan out compatibility (IOI = 20 mA for SBP9900A, IOL = 16 mA for SBP9989)

- o The READY input signal (pin 62) needs to be active during CRU transactions to avoid wait states

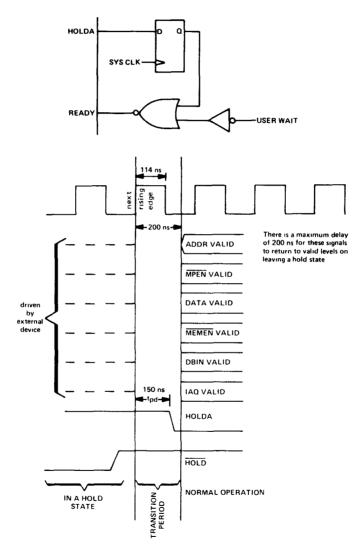

- Automatic wait states are typically generated with the SBP9900A by tying the wait output signal back into the READY input. However, unlike the SBP9900A, the SBP9989 will continue to generate wait signals during a HOLD operation. To eliminate the unwanted wait signals during HOLD operations, the HOLDA and WAIT output signal lines can be OR-ed to drive the READY input line.

#### Software

- Although software written for the SBP9900A can be executed by the SBP9989, a reduction of 15% to 20% in execution time should be anticipated. Software timing loops will need new time constants to compensate for the reduced execution times.

- Any unused op codes used as NOP's in the SBP9900A software will cause the SBP9989 to execute a level 2 interrupt trap

- o Status bit 10 set to 1 will enable the arithmetic overflow detection trap

#### DEVICES FOR MILITARY TEMPERATURE APPLICATIONS

The SBP9989 is a member of the ever growing family of military microprocessor components

| SBP9989    | 16 Bit Advanced Hi Rel Microprocessor               |

|------------|-----------------------------------------------------|

| SBP9900A   | 16-Bit Hi-Rel Microprocessor                        |

| SBP9965    | Peripheral Interface Adapter                        |

| SBP9901    | Programmable Systems Interface (in design)          |

| SNJ54LS244 | Octal Buffer Line Driver/Line Receiver              |

| SNJ54LS373 | Octal D-Type Transparent Latch                      |

| SNJ54LS374 | Octal D Type Edge-Triggered Flip-Flop               |

| SNJ54LS610 | Memory Mapper (future product)                      |

| SNJ54LS629 | Dual Voltage Controlled Oscillator                  |

| SNJ54LS630 | 16-Bit Parallel Error Detection and Correction Unit |

| SNJ54LS644 | Octal Bus Transceiver                               |

| SNJ54LS645 | Octal Bus Transceiver                               |

| SNJ54LS673 | 16-Bit Shift Register                               |

| SNJ54LS674 | 16 Bit Shift Register                               |

| SNJ54S189  | 64 Bit (16 x 4) RAM                                 |

| JBP24S10   | 1024-Bit (256 x 4) PROM                             |

| JBP18S030  | 256 Bit (32 x 8) PROM                               |

| JBP28S46   | 4096 Bit (512 x 8) PROM                             |

| JBP28L86   | 8192-Bit (1024 x 8) PROM                            |

| JBP28S86   | 8192-Bit (1024 x 8) PROM                            |

|            |                                                     |

## **BLOCK DIAGRAM**

GND 1

INTREO 32

33 6 103

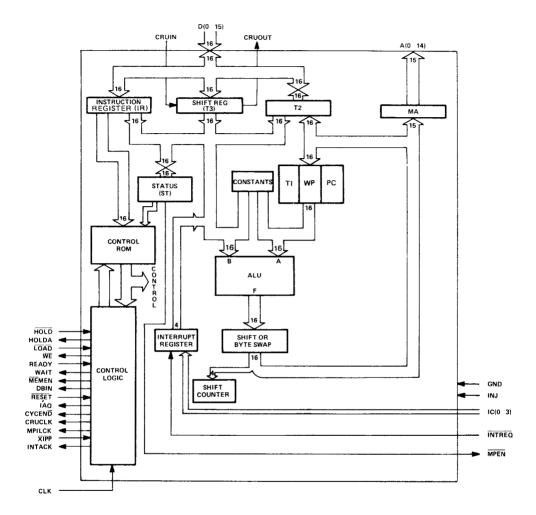

## PIN ASSIGNMENTS AND FUNCTIONS (PIN NUMBERS ARE FOR 64-PIN DIP)

| SIGNATURE             | PIN#          | 1/0  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       |               |      | ADDRESS BUS                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| A0 (MSB)<br>A14 (LSB) | 24<br>↓<br>10 | OUT* | A0-A14 comprise the address bus. This open-collector bus provides the memory address to the memory system when $\overline{\text{MEMEN}}$ is active and CRU I/O bit addresses to the I/O system when $\overline{\text{MEMEN}}$ is inactive and DBIN is active                                                                                                                                                                  |  |

| MPEN                  | 25            | OUT* | MEMORY MAP ENABLE MPEN represents the inverted value of Status Register<br>Bit 8 (ST8) MPEN can be changed by any instruction (i.e., LST, etc.) affecting ST8<br>and will be set to 1 during SBP989 trap addressing, namely interrupts, LOAD,<br>RESET, XOP and ILLOP, MPEN may be used to allow memory expansion to<br>64 kilowords                                                                                          |  |

|                       |               |      | DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| D0 (MSB)              | 41<br>↓<br>56 | 1/0* | D0-D15 comprise the bidirectional, open-collector data bus This bus transfers<br>memory data to (when writing) and from (when reading) the external memory<br>system when MEMEN is active                                                                                                                                                                                                                                     |  |

|                       |               |      | POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| LNI<br>LNI<br>LNI     | 9<br>26<br>40 |      | Injector-Supply Current<br>Injector-Supply Current<br>Injector-Supply Current                                                                                                                                                                                                                                                                                                                                                 |  |

| INJ                   | 57            |      | Injector-Supply Current                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| GND                   | 1             |      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| GND                   | 2             |      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| GND<br>GND            | 27 28         |      | Ground<br>Ground                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                       |               |      | CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| CLK                   | 8             | IN   | Single-phase clock input                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                       |               |      | BUS CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| MEMEN                 | 63            | OUT* | MEMORY ENABLE. When active (low), MEMEN indicates that the address bus contains a valid memory address.                                                                                                                                                                                                                                                                                                                       |  |

| DBIN                  | 29            | OUT* | DATA BUS IN When activated (high) by the SBP9989 during MEMEN, DF<br>indicates that the SBP9989 has disabled its output buffers to allow the mem<br>system to place memory read data on the bus. The SBP9989 will also activ<br>DBIN during all CRU operations and during the execution of the five exter<br>instructions. In all other cases except when HOLDA is active, the SBP9989<br>maintain DBIN at a low logic level. |  |

| WE                    | 61            | ουτ• | WRITE ENABLE When active (low), $\overline{WE}$ indicates that the SBP9989 data bus is outputting data to be written into memory                                                                                                                                                                                                                                                                                              |  |

.

\*When HOLDA is active, these terminals are high

| SIGNATURE | PIN#          | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |               |     | COMMUNICATION REGISTER UNIT (CRU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CRUCLK    | 60            | Ουτ | CRU CLOCK When active (high), CRUCLK indicates to the external logic the<br>presence of output data on CRUOUT or the presence of an encoded external<br>instruction on A0 A2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CRUIN     | 31            | IN  | CRU DATA IN CRUIN receives input data from the external interface logic<br>When the SBP9989 executes a STCR or TB instruction, it samples CRUIN for<br>the level of the CRU bit specified by the address bus (A3 A14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CRUOUT    | 30            | ουτ | CRU DATA OUT CRUOUT outputs serial data when the SBP9989 executes a LDCR, SBZ, or SB0 instruction. The data on CRUOUT should be sampled by the external interface logic when CRUCLK goes active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |               |     | INTERRUPT CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ÎNTREQ    | 32            | IN  | INTERRUPT REQUEST When active (Iow), INTREQ indicates that an external interrupt is requesting service. If INTREQ is active the SBP9989 loads the data on the interrupt code input lines ICO IC3 into the interrupt mask bits of the status register. If the interrupt code is equal to or less than Status Register Bits 12.15 (equal or higher priority than the previous enabled interrupt level), the SBP9989 will continue to sample ICO IC3 until the program enables a sufficiently low interrupt level to accept the requesting interrupt.                                                                                                                                                                                                                                                                                                                                          |

| ICO (MSB) | 36<br>4<br>33 | IN  | INTERRUPT CODES ICO (MSB) IC3 (LSB), indicating an interrupt identity code,<br>are sampled by the SBP9989 when INTREQ is active (Iow) When ICO-IC3 are<br>LLLL, the highest-priority external interrupt is requesting service, when HHHH, the<br>lowest-priority external interrupt is requesting service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTACK    | 37            | OUT | INTERRUPT ACKNOWLEDGE When active (high) during non-hold states, INTACK indicates the SBP9989 has initiated a trap sequence caused by the receipt of a valid interrupt, $\overline{LOAD}$ or $\overline{RESET}$ INTACK shall be activated in the trap sequence while the SBP9989 is obtaining the new WP value from memory An external device may determine which function or interrupt level is being serviced by monitoring the address bus during the INTACK time. When the SBP9989 is in a hold state (caused by activation of XIPP or $\overline{HOLD}$ ) INTACK indicates SBP9989 has received a valid interrupt (level is less than value of interrupt mask), a $\overline{LOAD}$ or $\overline{RESET}$ INTACK will remain valid (high) until the SBP989 leaves a hold state ( $\overline{HOLD}$ or $\overline{XIPP}$ released) or until the signal requesting interrupt is released |

| SIGNATURE | PIN= | 1/0  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           |      |      | MEMORY CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| HOLD      | 64   | IN   | HOLD When active (Iow), HOLD indicates to the SBP9989 that an external controller (e.g., DMA device) desires to use the memory bus for direct memory data transfers. In response, the SBP9989 enters the hold state after completion of its present cycle (memory or nonmemory). The SBP9989 then asserts HOLDA and allows its address bus, MPEN, data bus, MEMEN, WE, DBIN, IAQ and CYCEND to be pulled to the high logic state. When HOLD is deactivated, the SBP9989 reassumes bus control and continues operation by resuming execution of the suspended instruction.                                                                                                         |  |

| HOLDA     | 5    | оит  | HOLD ACKNOWLEDGE When active (high) HOLDA indicates that the SBP9989<br>is in a hold state and that its address bus, $\overline{\text{MPEN}}$ , data bus, $\overline{\text{MEMEN}}$ , $\overline{\text{WE}}$ , DBIN,<br>IAQ, and $\overline{\text{CYCEND}}$ are pulled to the high state. The SBP9989 will enter a hold<br>state in response to the activation of $\overline{\text{HOLD}}$ or $\overline{\text{XIPP}}$ (during the execution of an<br>ILLOP or XOP instruction)                                                                                                                                                                                                   |  |

| READY     | 62   | IN   | READY When active (high) READY indicates that the memory (for mei<br>operations) or CRU device (for CRU operations) will be ready to read or<br>during the next clock cycle. When READY is not active (low), the SBP9989 e<br>a wait state and suspends internal operations until the memory system or<br>device activates READY.                                                                                                                                                                                                                                                                                                                                                 |  |

| WAIT      | 3    | ουτ  | WAIT When active (high), WAIT indicates the SBP9989 has entered a wait state in<br>response to a not READY condition from a memory system or a CRU device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|           |      |      | TIMING AND CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| IAQ       | 7    | OUT* | INSTRUCTION ACQUISITION IAQ is activated (high) by the SBP9989 during<br>any SBP9989 initiated instruction acquisition memory cycle. Consequently, IAQ<br>may be used by an external device as an indication of when to sample the memory<br>data bus to obtain instruction operations code data.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| CYCEND    | 59   | оυт* | END OF CYCLE When active (low), CYCEND indicates that the SBP9989 will initiate a new microinstruction cycle on the next low-to-high transition of the clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| MPILCK    | 39   | OUT  | MULTIPROCESSOR INTERLOCK When active (high) MPILCK indicates the SBP9988 is performing the operations associated with operand transfer and manipulation for the ABS instruction MPILCK shall be activated by the SBP9989 during any ABS instruction upon initiation of the operand read operation and remain active until the completion of the instruction (i.e., MPILCK remains active for the duration of the SBP9989 read-modify-write operation cycle for the ABS instruction). Consequently, MPILCK may be used in the implementation of a nonseparable test and set capability HOLD is sampled during MPILCK activation, so MPILCK cantral set on the instruction of HOLD. |  |

\*When HOLDA is active, these terminals are high

| SIGNATURE | PIN# | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIPP      | 58   | IN  | EXTENDED INSTRUCTION PROCESSOR PRESENT When activated (low) by an external device (an extended instruction processor, XIP) upon detection of the acquisition of an SBP9989 undefined op code $\overline{XIPP}$ indicates the XIP will execute the undefined instruction. Recognition of $\overline{XIPP}$ will cause the SBP989 to allow its memory bus signals to be pulled high, activate HOLDA and enter a hold state (i.e., suspend internal operation) after it has stored its WP, PC and ST in the workspace defined by the interrupt level 2 trap vector. Upon receipt of HOLDA, the XIP may then proceed to execute the undefined instruction. During the instruction, the XIP may utilize the WP, PC and ST previously stored in memory by the SBP9898 Upon completion of its instruction execution, the XIP releases $\overline{XIPP}$ and allows the SBP9989 to resume bus control and restart instruction execution. The SBP9989 will resume operation by reloading (from memory) its WP, PC and ST $\overline{XIPP}$ may also be used to initiate a trap to interrupt level 2 by going active during IAQ for any instruction. This is useful for implementing break points or maintenance panels. |

| LOAD      | 4    | IN  | LOAD When active (low), $\overline{LOAD}$ causes the SBP9989 to set $\overline{MPEN}$ high, issue INTACK, store old PC, WP, and ST, set Status Register Bits 715 low and execute a nonmaskable interrupt with unmapped memory addresses FFFC16 and FFFE16 containing the associated rap vectors (WP and PC). The load sequence is initiated after the instruction being executed is completed $\overline{LOAD}$ will also terminate an idle state. If $\overline{LOAD}$ is active at the end of a reset function, the $\overline{LOAD}$ trap will occur after the reset function is completed. If $\overline{LOAD}$ is activated during a hold state (caused by $\overline{XIPP}$ or $\overline{HOLD}$ ), the SBP9989 will activate INTACK to indicate a pending $\overline{LOAD}$ leaves the hold state and the above conditions are met $\overline{LOAD}$ may be used to implement bootstrap loaders. Additionally, front panel routines may be implemented using GRU bits as front panel interface signals, and software control routines to direct the panel operations.                                                                                                                                   |

| RESET     | 6    | IN  | RESET When active (Iow logic level), $\overrightarrow{\text{RESET}}$ causes the SBP9989 to reset itself,<br>and inhibit $\overrightarrow{\text{WE}}$ and CRUCLK When $\overrightarrow{\text{RESET}}$ is released, the SBP9989 goes through<br>a level zero interrupt sequence by causing $\overrightarrow{\text{MPEN}}$ to go to high, issuing INTACK,<br>storing old PC, WP and ST, setting all status register bits low, acquiring the WP and<br>PC trap vectors from memory locations 000016 and 000216, and then fetching the<br>first instruction of the reset program environment if LOAD is not active. The<br>SBP9989 continuously samples $\overrightarrow{\text{RESET}}$ on low-to high clock transitions $\overrightarrow{\text{RESET}}$<br>must be active for one low-to-high transition of the clock and satisfy the hold<br>time requirements of this signal                                                                                                                                                                                                                                                                                                                                     |

#### **ARCHITECTURE AND TIMING**

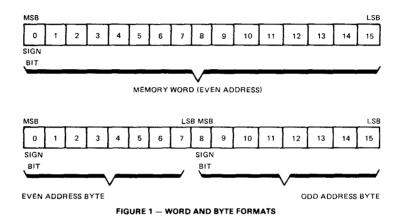

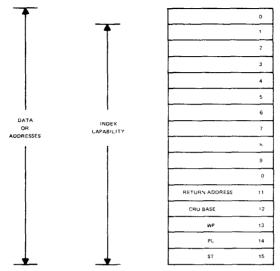

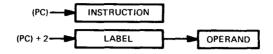

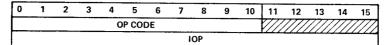

The memory word is 16-bits long as shown in Figure 1. Words are assigned even-numbered addresses in memori Each memory word contains two bytes of 8 bits each. The instruction set of the SBP9989 allows both word and byt, operations. Byte instructions may address either byte as necessary. Byte instructions that address a Workspace Register operate on the most significant byte (even address) of the Workspace Register and leave the least significant byte (odd address) unchanged. Since the workspace is also addressable as a memory address, the least significant byte may be addressed if desired.

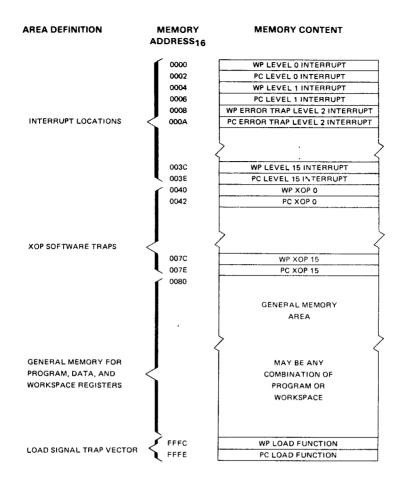

The SBP9989 memory map is shown in Figure 2. The first 32 words are used for interrupt trap vectors and the next contiguous block of 32 memory words is used by the XOP (Extended Operation) instruction for trap vectors. The last two unmapped memory words (FFFC16 and FFFE16) are used for the trap vector of the load signal. The remaining memory is then available for programs, data, and Workspace Registers.

#### **FUNCTIONAL DESCRIPTION**

#### **Block Diagram**

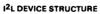

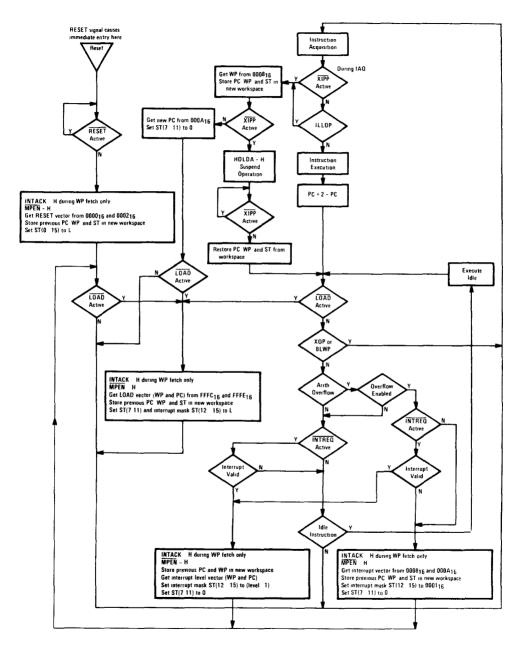

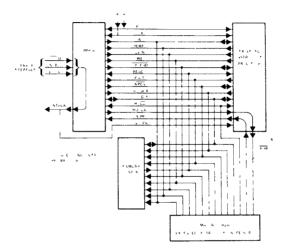

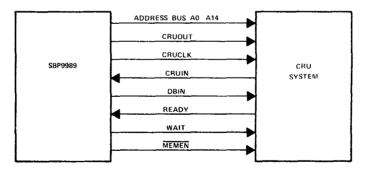

The block diagram is shown on page 10 A flow chart, representative of functional operation, is shown on page 9 Addresses are supplied to the Address Bus (AO-A14) by the Memory Address Register (MA) Instructions read from memory are loaded into the Instruction Register (IR) via the Data Bus (DO-D15)

Bit-oriented input/output operations are provided by the Communication Register Unit (CRU) interface whereby 1 to 16 bits may be transferred by a single instruction

#### Arithmetic Logic Unit (ALU)

The arithmetic logic unit (ALU) is the computational component of the SBP9989. It performs all arithmetic and logic functions required to execute instructions. The functions include addition, subtraction. AND, OR, exclusive OR, and complement.

The ALU is arranged in two 8-bit halves to accommodate byte operations. Each half of the ALU operates on one byte of the operand. During word operand operations, both halves of the ALU function in conjunction with each other. However, during byte operand processing, the least significant half of the ALU operates in a passive mode, performing no operation on the data that it handles. The most significant half of the ALU performs all operations on byte operands so that the status circuitry used in word operations is also used in byte operations.

#### FIGURE 2 - MAP OF THE MEMORY ARRANGEMENT

#### **Internal Registers**

The following three internal registers are accessible to the user (programmer).

- a. Program Counter (PC)

- b. Status Register (ST)

- c. Workspace Pointer (WP)

Other internal registers which are utilized during instruction acquisition or execution are inaccessible to the user.

#### **Program Counter (PC)**

The program counter is a 15-bit register (left justified with the LSB hardwired to 0) that contains the word address of the instruction currently executing. The SBP9989 increments this address to fetch the next instruction from memory

If the current instruction in the microprocessor alters the contents of the PC, then a program branch occurs to the location specified by the altered contents of PC. All context instructions affect the contents of the PC.

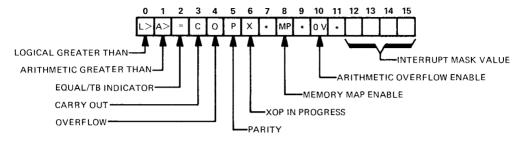

#### Status Register (ST)

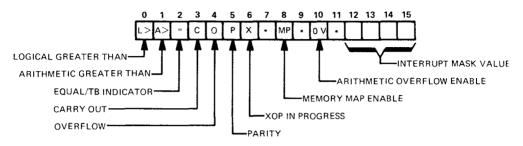

The status register is a fully implemented 16-bit register that reports the results of program comparisons, indicates program status conditions, supplies the arithmetic overflow enable and interrupt mask level to the interrupt priority circuits, and provides the external bit for memory expansion to 64K words and beyond. Each bit position in the register signifies a particular function or condition that exists in the SBP9989 as illustrated in Figure 3. Some instructions use the status register to check for a prerequisite condition, others affect the values of the bits in the register, and others load the entire status register with a new set of parameters. The description of the instruction set later in this document details the effect of each instruction on the status register.

\*These bits are functionally uncommitted and are available to the user

## FIGURE 3 - STATUS REGISTER BIT ASSIGNMENTS

#### Workspace

The SBP9989 uses blocks of memory words, called workspaces, for instruction operand manipulation (instead of internal hardware registers). A workspace occupies 16 contiguous memory words in any part of memory. The individual workspace registers may contain data or addresses, and function as operand registers, accumulators, address registers, or index registers. Some workspace registers take on special significance during execution of certain instructions. Figure 4 illustrates the workspace map A user-defined number of workspaces may exist in memory which provides a high degree of program flexibility.

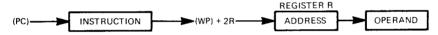

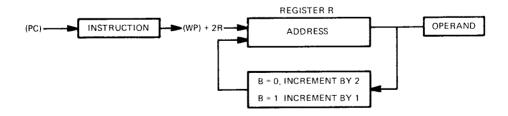

#### Workspace Pointer (WP)

To locate the workspace in memory, one hardware register called the Workspace Pointer (WP) is used. The Workspace Pointer is a 15-bit register (left justified with the LSB hardwired to 0) that contains the memory address of the first word in the workspace. The SBP9989 can then access any register in the workspace by adding two times the register number to the contents of the Workspace Pointer and initiating a memory request for that word. Figure 5 illustrates the relationship between the Workspace Pointer and its corresponding workspace in memory.

#### **Context Switching**

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another or to a subroutine as in the case of an interrupt. Such an operation using a conventional multi-register arrangement requires that at least part of the contents of the register file be stored and relocated using a memory cycle to store or fetch each word. This operation is accomplished by changing the Workspace Pointer: A complete context switch requires only three store cycles and three fetch cycles, exchanging the program counter, status register and Workspace Pointer. After the switch, the Workspace Pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresce the subroutine downkspace pointer (BLWP), return from subroutine (RTWP), and extended operation (XOP) instruming a context switch by forcing a trap to a service subroutine.

NOTE THE WP REGISTER CONTAINS THE ADDRESS OF WORKSPACE REGISTER ZERO

FIGURE 4 - WORK SPACE MAP

FIGURE 5 - WORKSPACE POINTER AND REGISTERS

In the case of a memory write cycle  $\overline{WE}$  becomes active (logic level low) with the first high to low transition of the clock after  $\overline{MEMEN}$  becomes active DBIN remains inactive (low). At the end of a memory write cycle  $\overline{WE}$  and  $\overline{MEMEN}$  become inactive ( $\overline{MEMEN}$  on the low to high transition of clock  $\overline{WE}$  on the preceding high to low transition of clock).

During either a memory read or a memory write operation READY may be used to extend the duration of the associated memory cycle such that the speed of the memory system may be coordinated with the speed of the SBP9989. If READY is inactive (logic level low) during the first low to high transition of the clock after  $\overline{\text{MEMEN}}$  becomes active the SBP9989 will enter a wait state suspending further progress of the memory cycle. The first low to high transition of the clock after READY becomes active terminates the wait state and allows normal completion of the memory cycle. The cycle end signal ( $\overline{\text{CYCEND}}$ ) will be activated (logic level low) for one clock period during each microinstruction cycle (i.e. memory operation non-memory internal operation etc.)  $\overline{\text{CYCEND}}$  will be activated on the low to high transition of the clock which initiates the last clock period of a microinstruction cycle and will be deactivated on the next low to high clock transition.

#### HOLD, DMA Interface

The SBP9989 hold facilities allow both the microprocessor and external devices to share a common memory. To gain memory bus control, an external device requiring direct memory access (DMA) sends a hold request (HOLD) to the SBP9989. When the next cycle (memory or non-memory) occurs, the microprocessor enters a hold state and signals its surrender of the memory bus to the external device via a hold acknowledge (HOLDA) signal.

Receiving the hold acknowledgement, the external device can proceed to utilize the common memory. After its memory requirements have been satisfied, the external device returns memory bus control by releasing HOLD.

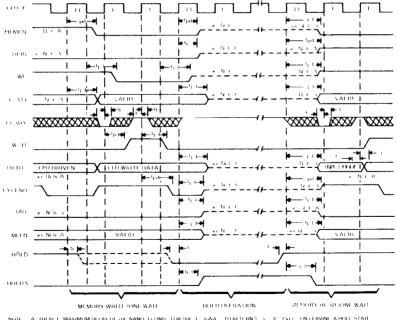

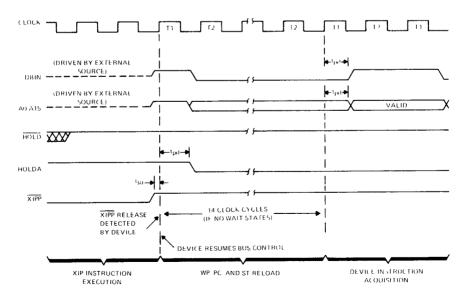

When HOLD becomes active (logic level low) the SBP9989 enters a hold state at the beginning of the next available cycle as shown in Figure 9. Upon entering a hold state. HOLDA becomes active (pulled to logic level high) with the following signals pulled to a high logic level by individual pullup resistors tied to each respective open collector output DBIN MEMEN TAQ. MPEN WE CYCEND AO through A14, and DO through D15. When HOLD becomes inactive the SBP9989 exits the hold state and regains memory bus control.

NOTE A THERET MAXIMUM DELAY OF JCENANO. FOR THE E-IGNA. TO KETERN 1.5. IF FVE ON LEAVING A HOLE STATE BE VALID MEMORY READ DATA. C. DRIVEN BY STELBARED BYTE

#### **xtended Instruction Processor Interface**

The extended instruction processor (XIP) interface provides for easy extension of the SBP9989 arithmetic logic processing functions by facilitating the addition of external hardware instruction processors while also permitting the usage of software interpretive implementations of extended instructions. The XIP interface provides user transparency regardless of the method of implementation (i.e. hardware or software) potentially eliminating software overhead. It allows true software transportability so that programs generated for systems based on the SBP9989 employing XIP s and those without XIP s can be identical.

The XIP interface utilizes the SBP9989 memory bus with direct memory access (DMA) capability and the extended instruction processor present ( $\overline{XIPP}$ ) signal as shown in Figure 10. The XIP interface requires the XIP to gain control of the SBP9989 memory bus during execution of any extended instructions encountered in the device program instruction stream. The extended instructions are assigned (by the user) operation codes (op codes) which are the illegal (undefined) operation codes NOP s (ILLOP s).

FIGURE 10 - EXTENDED-INSTRUCTION INTERFACE PROCESSOR

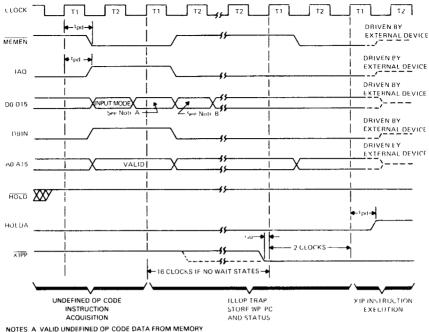

The sequence that characterizes a typical extended instruction execution is shown in Figures 11 and 12 As illustrated the SBP9989 fetches the instruction that contains the op code assigned to an extended instruction. The XIP detects the occurrence of the instruction fetch operation (IAQ active) and latches the instruction op-code data present on the memory data bus The XIP decodes the latched op-code as one of its instructions and asserts XIPP to the SBP9989 (non-extended instruction op codes would be ignored by the XIP). Recognition of the illegal op-code causes the SBP9989 to execute a program trap and store its context (i.e. WP PC and ST) in memory Storage will be in registers 13 14 and 15 of the workspace defined by the WP value contained in the SBP9989 Level 2 interrupt vector locations If XIPP is also active (logic level low) the SBP9989 allows its memory bus signals to be pulled to a logic level high issues HOLDA (Hold Acknowledge) and suspends internal operation. Having received HOLDA, the XIP assumes control of the memory bus and proceeds with execution of the extended instruction(s). During its instruction execution the XIP may access the PC\_WP and ST values (previously stored in memory), via the interrupt Level 2 workspace address as required to derive instruction operands and indicate execution results (status). After completing instruction execution the XIP releases XIPP Detecting the removal of XIPP causes the SBP9989 to remove HOLDA activate its memory bus drivers (i.e. resume bus control) restore its context (WP PC and ST) from memory and continue instruction processing. Where it resumes processing is determined by the PC value (updated by the XIP during execution) which it reacquires from memory after resuming control

B INPUT MODE

FIGURE 11 - EXTENDED INSTRUCTION PROCESSOR INTERFACE TIMING (ILLOP DETECTION)

FIGURE 12 - EXTENDED-INSTRUCTION PROCESSOR INTERFACE TIMING (WP,PC, ST RELOAD)

The XIP can be implemented with chaining capability, i.e., the ability to execute a sequence of extended instructions without returning control to the SBP9989. If an interrupt or LOAD occurs and the interrupt mask conditions are satisfied, the SBP9989 will activate INTACK (interrupt acknowledge) to indicate that an interrupt needs to be serviced Servicing of the interrupt will occur upon release of XIPP by the XIP and completion of the above context restore bus control resumption sequence.

As shown in Figure 10, the XIP interface provides for other Direct Memory Access (DMA) devices or more than one XIP device. However, it is the responsibility of the XIP device to receive, condition and transmit the required interface signals (i.e., HOLD, HOLDA, and XIPP) to satisfy additional DMA or XIP requirements.

For configurations not containing external XIP hardware, the  $\overline{XIPP}$  signal will not be activated. Therefore, the SBP9989 completes the context switch operations by loading PC data from the interrupt Level 2 trap vector. Software starting at this PC location then executes the intended function(s)

#### **Multiprocessor Interlock**

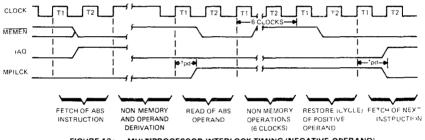

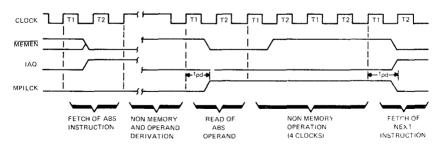

The Multiprocessor Interlock (MPILCK) signal permits the implementation of an indivisible test and set-semaphore mechanism for use in multiprocessor applications. The SBP9989 activates the MPILCK signal (logic level high.) during the execution of the Absolute Value (ABS) instruction as shown in Figure 13. MPILCK is activated on the low-to-high clock transition, initiates the first ABS operand memory access and remains active until the completion of the ABS instruction (i.e., occurrence of next IAQ or servicing of an interrupt, ICAD or RESET). HOLD is sampled during this time, so MPILCK can be used to control the assertion of HOLD.

FIGURE 13a - MULTIPROCESSOR INTERLOCK TIMING (NEGATIVE-OPERAND)

FIGURE 13b - MULTIPROCESSOR INTERLOCK TIMING (POSITIVE-OPERAND)

## INTERRUPTS

The SBP9989 employs 16 interrupt levels with the highest priority Level 0 and lowest priority Level 15 Level 0 is reserved for the RESET function. Level 2 is reserved at the user's option for the arithmetic overflow interrupt and/or an illegal op-code trap. Interrupt Levels 1 through 15 may be used for external device interrupts.

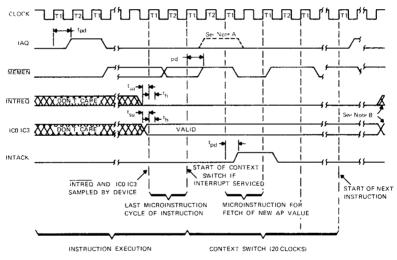

External device interrupts are input via the interrupt request (INTREQ) signal line and the four interrupt code lines (ICO IC3) Figure 14 shows the timing for the sampling of these inputs and their effect on SBP9989 operation. Activation of the INTREQ input causes a comparison with the interrupt code (ICO-IC3) with the interrupt mask contained in status register bits ST12 through ST15. When the level of the pending interrupt is less than or equal to the enabling mask level (higher or equal priority interrupt), the SBP9989 recognizes the interrupt and initiates a context switch following completion of the currently executing instruction. The new context (WP and PC) is fetched from the interrupt vector locations and the SBP9989 sets MPEN to one, activates the INTACK (interrupt acknowledge) signal line. Then the previous context (WP, PC and ST) is stored in workspace registers 13, 14 and 15, respectively, of the new workspace. Bits 7 through 11 of the status register are forced to zero and sets the interrupt mask to a value that is one less than the level of higher priority interrupt a service routine. The SBP9989 also inhibits interrupts until the first instruction of the device service routine has been executed. All interrupt requests should remain active until recognized in the device service routine. The individual service routines must reset the interrupt requests before the routine is completed.

NOTES A NEXT IAQ IF INTERRUPT NOT SERVICED

B INTRED AND ICO IC3 CHANGED BY INTERRUPT SERVICE ROUTING

C THIS DIAGRAM ASSUMES VALID IC IS OF HIGHER PRIORITY THAN CODE IN STATUS REGISTER

FIGURE 14 - INTERRUPT TIMING

If a higher-priority occurs, a second context switch occurs to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the routine parameters to complete processing of the lower priority interrupt All interrupt subroutines should terminate with the return instruction to restore original program parameters. The interrupt vector locations, device assignments enabling mask value, and the interrupt codes are shown in Table 1.

During a SBP9989 hold state resulting from the activation of HOLD or XIPP, the SBP9989 will continue to sample the interrupt code lines. Upon activation of INTREQ if the code is less than or equal to the device interrupt mask level, the SBP9989 will activate the INTACK signal to indicate a pending interrupt needs servicing. The INTACK signal will then remain active until HOLD or XIPP is released.

| INTERRUPT LEVEL       |        | VECTOR LOCATION<br>(MEMORY ADDRESS<br>IN HEX) | DEVICE<br>ASSIGNMENT            | ENABLING MASK<br>VALUES<br>(ST12 THRU ST15) | INTERRUPT<br>CODES<br>(IC0 THRU IC3) |  |

|-----------------------|--------|-----------------------------------------------|---------------------------------|---------------------------------------------|--------------------------------------|--|

| (Highest<br>priority) | 0      | 00                                            | Reset                           | 0 through F<br>(see Note 1)                 | 0000                                 |  |

| phoney/               | 1      | 04                                            | External<br>Device              | 1 through F                                 | 0001                                 |  |

|                       | 2      | 08                                            | Arithmetic<br>Overflow          | 2 through F<br>(see Note 2)                 | See Note 2                           |  |

|                       | 2      | 08                                            | or<br>Hlegal<br>op code         | 0 through F<br>(see Note 3)                 | See Note 3                           |  |

|                       | 2      | 08                                            | or<br>XIPP Active<br>during IAQ |                                             | See Note 4                           |  |

|                       | 2      | 08                                            | or<br>External<br>Device        | 2 through F                                 | 0010                                 |  |

|                       | 3      | oc                                            | ,<br>,                          | 3 through F                                 | 0011                                 |  |

|                       | 4<br>5 | 10<br>14                                      |                                 | 4 through F                                 | 0100                                 |  |

|                       | 6      | 14                                            |                                 | 5 through F<br>6 through F                  | 0101<br>0110                         |  |

|                       | 7      | 18<br>1C                                      |                                 | 7 through F                                 | 0110                                 |  |

|                       | 8      | 20                                            |                                 | 8 through F                                 | 1000                                 |  |

|                       | 9      | 24                                            |                                 | 9 through F                                 | 1000                                 |  |

|                       | 10     | 28                                            | "                               | A through F                                 | 1010                                 |  |

|                       | 11     | 2C                                            |                                 | B through F                                 | 1011                                 |  |

|                       | 12     | 30                                            |                                 | C through F                                 | 1100                                 |  |

|                       | 13     | 34                                            |                                 | D through F                                 | 1101                                 |  |

|                       | 14     | 38                                            |                                 | E and F                                     | 1110                                 |  |

| (Lowest               | 15     | 3C                                            | External                        | Fonly                                       | 1111                                 |  |

| priority)             |        |                                               | Device                          |                                             |                                      |  |

### TABLE 1 -- INTERRUPT LEVEL DATA

NOTES 1 Level 0 cannot be disabled

2 Arithmetic overflow interrupt is generated internal to the device and is enabled disabled by bit 10 of the status register.

3 Illegal op code trap is generated internal to the device and it cannot be disabled by the interrupt mask

4 XIPP (pin 58) is inactive at logic level high

#### Interrupt Level 0 - RESET

Interrupt Level 0 is reserved for the RESET input to the SBP9989 When asserted (logic level low), RESET causes the SBP9989 to reset itself and inhibit WE and CRUCLK

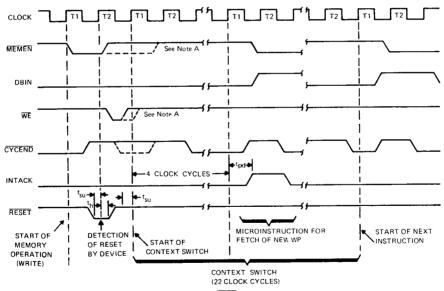

When RESET is released, a Level 0 interrupt sequence is initiated acquiring the WP and PC trap vectors from memory locations 000016 and 000216, INTACK is activated, all status register bits are set low, and the first instruction of the reset program environment is fetched. If LOAD is active, the LOAD trap occurs after the RESET function is completed The SBP9989 continuously samples RESET on low-to-high clock transitions as shown in Figure 15. To be recognized, RESET must be active for one low-to-high transition of clock and must satisfy the setup and hold time requirements

#### Interrupt Level 2

Interrupt Level 2 has two additional capabilities associated with its usage. Arithmetic overflow conditions, indicated by status register bit 4 (ST4) = 1, can cause a Level 2 interrupt to occur at the end of the instruction which generated the overflow condition. Servicing of this overflow interrupt can be enabled/disabled by status register bit 10 (ST10), the Arithmetic Overflow Enable Bit (i.e., ST10 = 1 enables overflow interrupt, ST10 = 0 disables overflow interrupt. The overflow interrupt can also be inhibited by the interrupt mask (ST12-ST15) or overridden by a pending Level 0 or Level 1 interrupt. If servicing the overflow interrupt is overridden by a higher priority (Level 0 or 1) interrupt, the overflow condition will be retained in the contents of the status register, which are saved by the higher-priority-interrupt context switch. Returning from the higher-priority-interrupt subroutine via an RTWP instruction causes the overflow condition to be reloaded into status register bit 4 (ST4) and the overflow interrupt to occur upon completion of the RTWP instruction. Servicing of a Level 2 arithmetic overflow interrupt forces the interrupt mask to 0001<sub>2</sub>. The arithmetic overflow interrupt service routine must reset ST4 to zero before the routine is complete

NOTES A DASHED LINES INDICATE SIGNAL WAVEFORMS IF RESET HAD NOT OCCURRED

B CASE SHOWN ASSUMES RESET IS DETECTED DURING MEMORY OPERATION

C SYNCHRONIZE RESET WITH IAO ON T1 TO PREVENT LOSS OF INSTRUCTION IN PROGRESS

D RESET MAY OCCUR ON ANY LOW TO HIGH CLOCK EDGE FOLLOWING DEACTIVATION OF RESET.

E CONTEXT SWITCH WILL START ON LOW TO HIGH CLOCK EDGE FOLLOWING DEACTIVATION OF RESET

FIGURE 15 - RESET TIMING

#### Undefined Op-code Trap

The acquisition and execution of illegal SBP9989 (undefined) op codes cause a trap operation to occur using the information stored in the Level 2 vectors. The op codes which cause the trap are 0000-007F-00A0-017F-0320-033F-0780-07FF-0C00-0FFF-As described earlier if the XIPP signal is activated during the undefined instruction, the SBP9989 will suspend operation and the instruction will be executed by the XIP-However if the XIPP signal remains inactive the undefined op-code will cause a trap and a context switch will occur. The occurrence of the trap is non-maskable (i.e. not controlled by the interrupt mask value) and the trap will override any level interrupt. Interrupts are inhibited until the first instruction of the trap subroutine is executed. The occurrence of the undefined op-code trap does not change the interrupt mask.

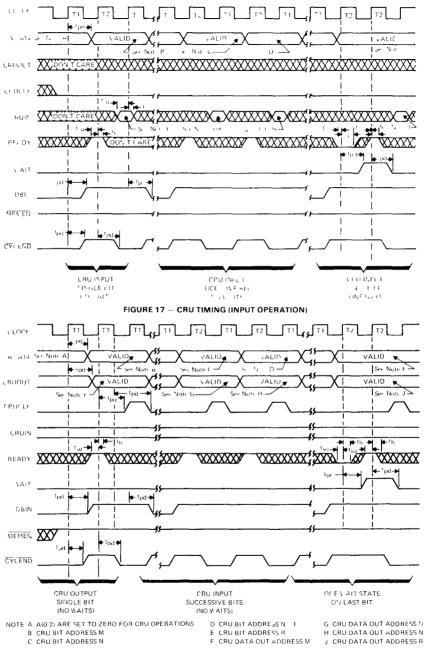

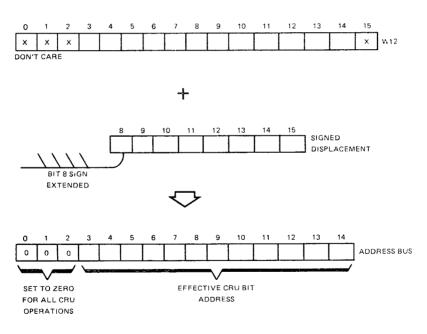

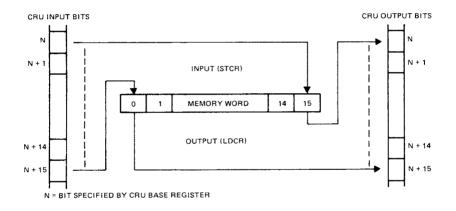

#### Communication Register Unit (CRU) Interface

The Communications Register Unit (CRU) is a direct command driven bit oriented LO interface. The CRU may directly address, in bit-fields of one to sixteen bits up to 4096 peripheral input bits, and up to 4096 peripheral output bits. The SBP9989 executes three single-bit and two multiple bit CRU instructions. The single bit instructions include test bit (TB), set bit to one (SBO) and set bit to zero (SBZ), the multiple bit instructions include load CRU (LDCR) and store CRU (STCR).

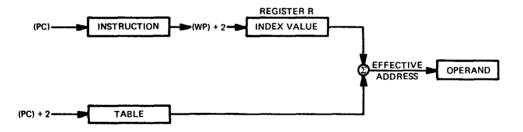

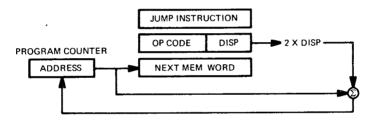

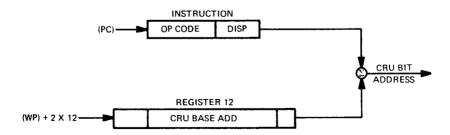

As shown in Figure 16, the SBP9989 utilizes three dedicated LO signals CRUIN\_CRUOUT\_CRUCLK, the least significant twelve bits of the address bus\_DBIN\_READY and WAIT to support the CRU interface. CRU interface timing is shown in Figures 17 and 18.