1 — The background

by Philip Darrington

### The first of a series of articles on the Teletext television information display system and the construction of a decoder for use with domestic television receivers.

In succeeding articles of this series we shall describe the design and construction of the Wireless World Teletext Decoder. But, before we do that, it seems only sensible to make sure that readers are up to date with current activity in the field and have an idea of other systems which have been proposed. We will also describe the basic operation of Teletext and mention the techniques used to decode the transmissions for display on a domestic television receiver.

In the early years of "wireless", the vision of millions of people being entertained by transmissions was just not credible. Television was thought to be sheer science fiction and wireless itself was for the transmission of vital information. Even if it had been possible to communicate phonically, that was not the idea at all – ships were the real users of radio and if amateurs could derive pleasure from listening to marine morse traffic or Eiffel Tower time signals, so much the better.

Then, of course, radio telephony was developed and the entertainment possibilities were recognized. It is now an extraordinary and rather depressing fact that out of the few thousand megahertz available for radio transmission, nearly 600MHz are taken up by broadcasting stations, most of which put out entertainment of one sort or another. Sound is reasonably restrained in its use of bandwidth, but television occupies 566MHz - a staggering figure, particularly as the television signal contains so much redundancy. Anything designed to make better use of this signal is to be welcomed and Teletext is one way of doing that, in that a previously unused part of the waveform is used to transmit more information.

Many ways of using television transmissions to better effect have been proposed<sup>1, 2</sup>. Since the early sixties, test signals inserted in the field blanking interval have been in common use, and have been supplemented by coded data transmitted on lines 16 and 329 of each frame<sup>3</sup>. It apparently did not, at the time, occur to ORTF, who originally used the system, that the technique could be developed to allow the transmission of visible information, but the system was used for switching remote transmitters, identification for remote supervision purposes, etc.

Other systems of transmission aimed at "still" display, with or without sound and in colour or monochrome depend on the exclusive use of a television or sound channel. For instance, the NHK "A" system<sup>4</sup> is able to carry over 50 channels of colour still pictures, with sound, in the bandwidth of one normal television channel. The pictures are transmitted at the rate of one still per frame, together with a code to enable a magnetic disc memory in the receiving equipment to record a selected frame, which is then continuously replayed. Sound is multiplexed with video information and transmitted in the frame intervals.

The NHK "B"<sup>4</sup> system falls into the multiplexed television channel category, using uncoded signals. Three unused lines per field are used to transmit three lines of a still picture, which is magnetically recorded at the receiver. Sound is transmitted by the use of additional sound carriers at low level, spaced further in the spectrum from the vision channel than the original sound carrier.

In 1971, W. D. Houghton of RCA described the Homefax<sup>5</sup> system in which additional information was multiplexed with a broadcast television waveform to produce "hard copy" from an electro-optical printer, using a cathode-ray tube to produce the "printing" on Electrofax paper. The information, uncoded, was carried in an unused vertical interval line and transmitted in the normal way – each of these lines producing part of one line of a row of print on the receiver paper. Transmission tests of this system had been carried out in 1967, and improve-

ments were being carried out in 1970. A method of data transmission not using the vertical blanking interval<sup>6</sup> was described by P. T. King of Hazeltine Research, Inc., at the SMPTE Technical Conference in 1973. In this system, known as an "add-on" type, a low-level subcarrier was inserted on the vision signal at an odd multiple of half the line frequency, a method which is well known in colour television circles as a method of avoiding interference between two signals in a common waveform. The added signal is shifted in phase from line to line and the visible effects are reduced. The actual frequency is chosen to be between 2 and 3MHz in the NTSC standard. because radiated energy at is a minimum in that region in a typical picture. The data signal is biphase modulated at 21 kilobits per second and at the receiver is synchronously detected, the data decoded and used to operate a character generator, which can, for example, produce subtitles in languages using the characters available.

These two techniques – the use of previously blank lines in the vertical blanking interval and the provision of a character generator at the receiving end – paved the way for Teletext. A system of this kind is able to carry more information, more flexibly, by leaving the receiver to do rather more of the work than an analogue or uncoded digital system. If the transmitted signal is made to carry instructions to the receiver on what to do, the receiver can then hold much of the information in store, releasing it when commanded to do so.

Peter Hutt of the IBA described an embodiment of this principle in a paper read to the IPC, 1972<sup>7</sup>. The system was named SLICE and was primarily intended for the labelling of programmes with a source identification. The information was carried on lines 16 and 329 in the form of 112 binary digits per line and, at the receiver, was read into a memory where a complete message was assembled. SLICE was the fore-runner of ORACLE and CEEFAX. (Hutt mentioned the possibility of a domestic information service in his paper.)

#### Teletext

ORACLE was developed by the Independent Broadcasting Authority in the light of its experience with SLICE and the BBC announced their own system, which was very similar and bore the name CEEFAX. (ORACLE is an acronym - Optional Reception of Announcements by Coded Line Electronics - CEEFAX is See Facts as pronounced by an adenoidal dyslexic.) There is little profit in trying to decide which organization hit upon the idea first, or which was on the air first, as the two were quickly and sensibly to agree on a common standard of transmission, in conjunction with BREMA<sup>8</sup>. Both names will probably continue to be used for each organization's broadcasts, but the generic term "Teletext" is now common, and will be used henceforth. Teletext has been broadcast on the present standard since September 1974 - the beginning of a two-year experimental period. The system uses a multiplex-with-vision type of transmission and uses lines 17 and 18/330 and 331 to carry coded information. There is no accompanying Teletext sound.

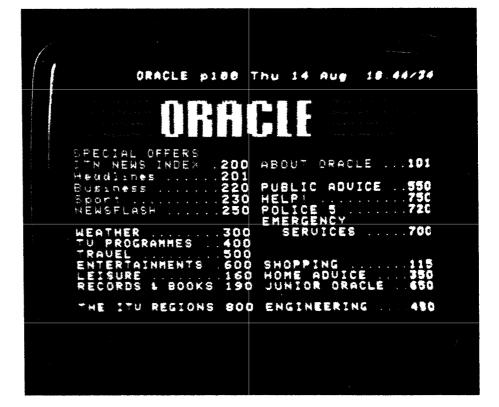

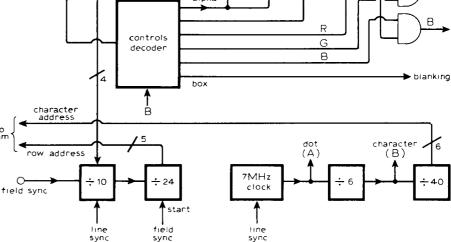

Before proceeding further, a look at the facilities offered by a Teletext transmission and a résumé of some of the specification will be a help when considering the equipment needed in the receiver. Briefly, the Teletext page consists of 23 rows of 40 characters each, plus a page header, which is only partly displayed. As seen in Fig. 1, the header gives the name of the service (Ceefax or Oracle), the page number, the date and the time. The time display is continually changing and is always visible.

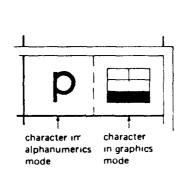

Visible characters are either capitals or lower-case letters assembled on a  $7 \times$ 5 dot matrix and in one of six colours or white: diagrams or low-resolution "pictures" can be assembled by the use of a block of cells on a  $3 \times 2$  pattern, each of which can be "on" or "off", in colour. A variety of other symbols (commas, brackets, @, £, etc.) can also be shown, and the set of characters is known as the ISO-7 code, which is a version of the ASCII code with some of the "National usage" characters substituted. Characters can be made to flash on and off, though our own feeling is that this will be used rather less when the service is finally in use than it is now, if it infuriates other people as it does the writer.

The Teletext editing teams can use the pages in three different ways, the norm being single pages which appear when selected by the viewer at any time and which are up-dated perhaps once or twice a day. A second type is one of a group of, perhaps, four such pages which change at about one minute intervals. They will usually be on a related topic, such as sport, and are identified by the letters A B C or D, the relevant letter being in a different colour so that the viewer knows which point in the set of pages has been reached. This type is really the same as the first variety, but pages are changed

Fig. 1. The main index page (p. 100) of

ORACLE for August 14, 1975, produced

by the W.W. decoder on a Thorn colour

receiver.

automatically at minute intervals. The third kind of page can be selected by the time-code on the header, so that it can be received, placed in store and read out at a convenient time.

The data to be displayed can be presented as a complete page or, in the case of news flashes or subtitles, can be inserted in a blank rectangle on the screen, leaving the rest of the picture visible. The full page can be superimposed on the picture, but in our experience this is a good way to ruin one's evesight.

A typical magazine has the capacity of 100 pages. Four lines are transmitted per television frame and there are 24 lines per Teletext page. A full magazine would therefore take 600 frames or 24 seconds to cycle. The BBC and IBA appear to differ on what they consider acceptable access times; the BBC suggest a typical time of 12 seconds (for an unspecified number of pages) while a recent check on Oracle gave an access time of 28 seconds for well over 100 pages. The theoretical time can be reduced considerably by not transmitting blank lines, a practice which is already followed by the IBA and which the BBC intend to change to shortly (they already omit blank lines at the bottom of a page).

To select a Teletext page, one first switches the signal path through the decoder, selects a page by means of thumbwheel switches or a set of pushbuttons and waits for the selected page to be assembled.

#### **Teletext signal**

The method of transmission of the Teletext data is of interest at this point. As has been said, the data signals are carried by lines 17 and 18 and the corresponding lines in the alternate field, 330 and 331. The choice of lines is influenced by the need to avoid the early part of the vertical blanking interval and the few lines near the start of the video signal (lines 23 and 336). If early lines were used, it is possible that data would appear on the field flyback on some receivers and if lines later than 18/331 carried the information, receivers with incorrect picture height adjustment or with a downward-shifted picture might show the data as an extremely "busy" pattern of dots at the top of the screen - this sometimes occurs even with the present line allocations. A further reason for avoiding lines 19/332, 20/333 is that they are currently used for insertion test signals, which are often visible but, being static, are not obtrusive.

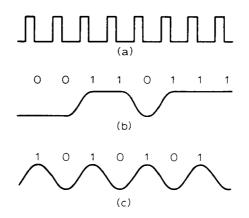

A form of binary code is used for the data, known as non-return-to-zero, which possesses the advantage over a complemented-element code of a reduced bandwidth requirement. As its name suggests, the resulting waveform is not a continuous train of pulses, but rather a series of voltage levels. A

499

typical sequence is shown in Fig. 2(b), where it is seen that a "1" level does not automatically return to zero at the end of the pulse and if the succeeding level is also 1, the voltage merely stays up similarly with a succession of "0". One result of this is seen in Fig. 2(c) where a train of the form  $0 \, 1 \, 0 \, 1 \, 0 \, 1 \, \text{etc.}$  turns out to be a square wave at half the repetition frequency of the clokc. As transmitted the pulses are "raised-cosine" in form and the square wave becomes a half-clock-frequency sinusoid.

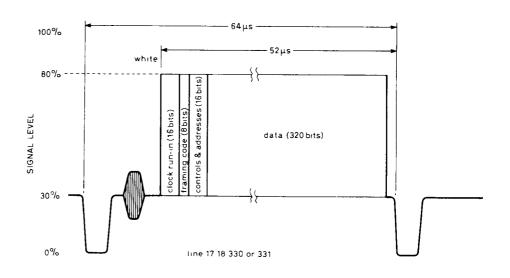

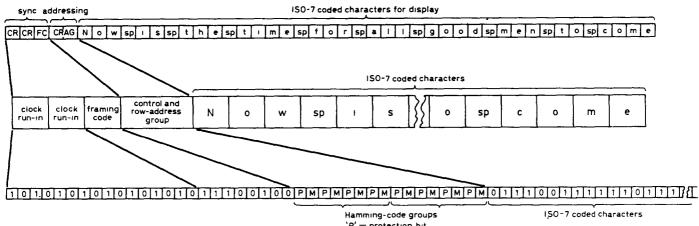

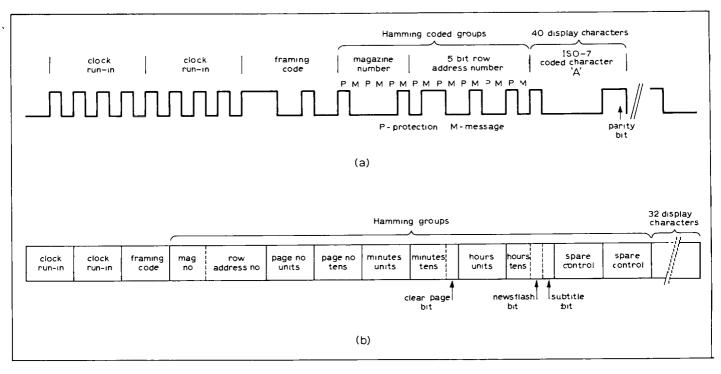

The diagram in Fig. 3 shows one line of the complete picture frame. A complete line occupies  $64\mu$ s, of which about  $12\mu$ s are taken up with the synchronizing pulse, back porch with colour burst and front porch. The first 40 of the 360 bits are concerned with clock synchronization (in a manner similar to that of the colour burst), a series of bits which constitute a "start" sequence and 16 bits for control and row address information. The rest of the line contains 320 bits for display and control. Figure 4 shows the layout of information in the line.

#### Coding

All transmission paths are subject to errors, and television has its share. Noise can be a problem, but the type of distortion caused by multipath propagation is perhaps the deadliest source of error. Both BBC and IBA have done work on this in the U.K., Sweden and Germany, and have come to the conclusion that Teletext transmissions are fairly robust, but require a good performance in the receiver. This relative invulnerability to attack is assisted by the application of code protection additional bits of information transmitted with the data.

Code protection is applied in two levels. Data bits which are intended for addressing and control are heavily protected, while those used to produce the displayed characters are protected rather less. The transmitting authorities consider that the occasional error in, or rejection of, a character is not serious as it will quite probably be corrected on the succeeding transmission of the page, but that an error in an address would lead to complete nonsense and must be avoided in the presence of the average amount of noise and ghosting.

The character code is basically 7-bit ISO-7 and is protected quite simply by means of a parity bit, giving odd parity. This means that if the total of "1s" in the basic 7 bits is odd, the parity bit is "0". An even total of "1"s in the 7 bits dictates a "1" parity bit to maintain an odd overall total. On examination at the receiver, any byte (the name for a "word" of 8 bits) with an even number of "1"s is seen to contain one error and is rejected. Previously-correct words in a display will not, therefore, be overwritten by an incorrect one and the effect is a reduction in errors in succeeding pages. Double errors, preserving odd parity, are not rejected and will be written.

Address data bits, on the other hand, are more heavily protected by being transmitted in a type of code which will detect 2, 4 or 6 errors in the byte and will detect and correct a single error. This type of code was described by R. W. Hamming in a classic paper<sup>9</sup> in 1950, and is known as the Hamming code. It takes the form of four parity bits in positions 1, 3, 5 and 7 of the eight-bit byte (the addresses are in a four-bit code). Three of the parity checks are associated with groups of three of the four message bits and the overall parity check covers all message and parity bits. Failure of the overall parity indicates an error and the position of the error is identified by the checks on the groups of three bits. If the overall parity appears true, but the individual checks show that a correction is required, there will have been a double error and the byte will be rejected as unusable.

Figs. 3 and 4 indicate that the bits at

Fig. 2. The non-return-to-zero method of transmitting binary information is at (b) with the attendant clock at (a). A succession of 101010 etc. gives a half-clock frequency waveform and, if the pulse shape is a raised cosine, as used in Teletext, the result is a sinusoid at 3.5 MHz.

Fig. 3. A line of Teletext data. Sync. pulses are the 30% pulses and the colour burst is on the back porch.

the beginning of the line are not concerned with the displayed message. Three groups of bits are transmitted, of which one is two bytes (16 bits) designed to lock the receiver's clock in frequency and phase with the transmission, in a similar manner to the way in which the colour burst dictates phase in a colour receiver. The 16 bits are termed the clock run-in and consist of a train of 1 0 1 0 1s. It is a penalty of the n.r.z. code used that this run-in is necessary, as it entails a code which is not self-clocking. In other words, unless the data are of the 101010 variety, which conveys no information, the transitions do not occur at every interval, and the data pulses themselves could not be used as a clock source, if it were not for the choice of odd parity for the protection code, ensuring at least one transition per character, which can be used to refresh the clock generator. The 16-bit burst of 3.5MHz is also detected and used to identify the transmission as Teletext and not some other data system such as SLICE (IBA), ICE (BBC) or insertion test signals.

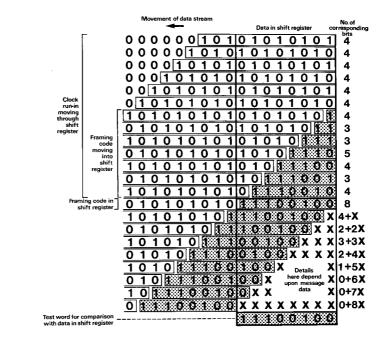

The second group of 8 bits forms the framing code, which is always the same and is used to indicate the start of the first 8-bit word. The order of bits used is 11100100 - an arrangement which is designed to avoid errors. A common way to detect the framing code is to pass all data through an 8-bit shift register and to examine the parallel outputs of the register. There will be only one step, when the register contains all eight bits of the framing code, when the above order of bits is present at the outputs of the shift register and gives a positive comparison with the "permanent" word used for detection. The framing code is shown in progress through the shift register in Fig. 6, which indicates that, even in the presence of bits from the clock run-in (c.r.i.) and succeeding information, a maximum of 5 bits "look like" the framing code. By means of more or less extensive circuitry, the framing code detector can be made to recognize the code in the presence of one error.

Row addressing. The 16 bits following the framing code are concerned with the identification of the following data. Each of the 24 rows of characters must be identified and this is done by numbering each with a row number from 0-23 and a magazine number (1 to 8). The bottom line of Fig. 4 shows the layout of bits in the 16-bit group and also indicates the fact that these are protected by being Hamming-coded. As, at the moment, we are not concerned with protection, the bits marked "P" can be ignored, and the groups become 4-bit words. In fact, this is an artificial distinction, because they form one word of three bits and one of five. The first group of three message bits (marked "M") identifies the magazine, and the remaining five contain the row address in a pure binary code (00001 is Row 1, 10111 is Row 23). The least significant bit is transmitted first.

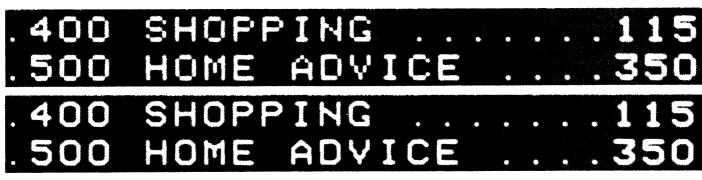

**Data.** The rest of the line is filled with data for display, the previous bits not, of course, being visible on the screen. Fig. 5 shows the complete set (in use until Sept. 1, 1975) of available characters and blocks for graphic displays, together with the address code (bits 1-7). Bit 8 is the parity bit and plays no part in the display. A slightly modified table will be used exclusively after September, 1976, and the system is now in transition between the two.

#### Decoding

The circuitry for decoding Teletext transmissions is extra to that in an ordinary receiver and is mainly digital in nature. When the services are established and commercial receivers are sold (several firms already have models), the decoders will be built in, but before that happens, many viewers will want to convert their existing receivers, an add-on unit being the obvious solution, with video signals into and out of the decoder. U.h.f. input and output will probably not be used, the cost of a colour modulator, for instance, being prohibitive.

The extra circuitry needed can be considered in three groups; data acquisition, storage and output processing.

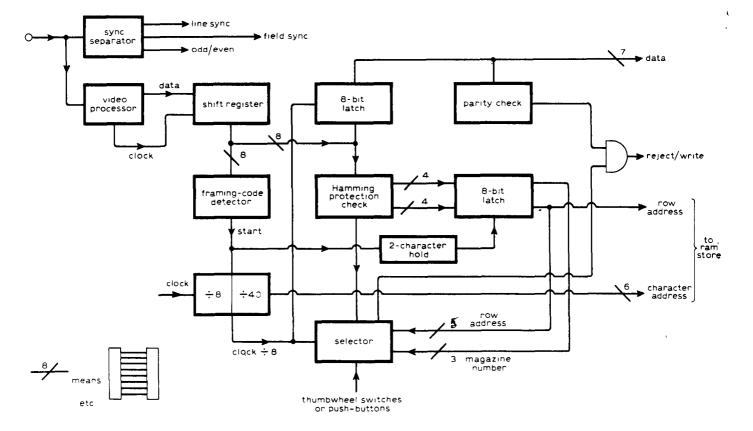

The detected vision signal is taken from the television receiver, having been disconnected from the video amplifier, and taken to the decoder, where clock regeneration, framing-code detection, parity checking, serial-to-parallel conversion and page selection are carried out. The selected and organized information is then passed to a store (either a multitude of shift registers or a random-access read/write memory) until the selected page is assembled. When this has been done, the store addresses the character generator in the output processor (a read-only memory containing the ISO-7 characters) which indirectly drives the guns of the display tube.

Input processor. This preliminary canter through the decoder is, of course, grossly over-simplified and a closer look at the sections is necessary, the first of these being the video processor which operates on the video signal to derive data and clock pulses. As has been said, the n.r.z. code in which data are transmitted, is not a self-clocking code and the decoder must contain its own clock. The clock run-in contained in the Teletext signal can operate as either a locking sequence for an oscillator which is continuously running, but which drifts out of phase with the Teletext clock between lines, or can be used to excite a passive oscillatory circuit which then rings for at least the duration of the Teletext line, being automatically in phase and frequency synchronization with the signal when the LC circuit is properly tuned. Each transition of the data "refreshes" the tuned circuit.

The diagrammatic input processor of Fig. 7 shows that the data is first passed through a serial-in, parallel-out store the shift register, which is clocked at data rate. The register is 8 bits long and can contain one word, complete with its parity bit (4 parity bits in the case of Hamming-protected words). The 8 bits, in parallel, are examined by the framing-code detector for coincidence with the 11100100 "start" sequence which, when detected. resets а "divide-by-eight" counter to zero. The

Fig. 4. A row of data It is seen that each group of 8 bits (1 byte) has a separate function. Clock run-in and Control and Row address each have two groups.

output of the counter is a pulse at one-eighth the rate of the clock and is used to identify correctly-framed words of 8-bit words in the shift register. In other words, framing-code detection indicates a reference point and the counter produces a pulse every eighth clock period which transfers the group of eight bits currently in the shift register, through latches, to the data lines. The output if the latch only changes when the counter indicates that the eight bits being presented to it are, in fact, a word. Complete characters are therefore presented on the eight, parallel data lines in serial form, reducing the 6.9375MHz rate to 867kHz.

The parallel data presented to the latches are also examined by the Hamming-code checker which, as was seen, can correct one error and detect 2, 4 or 6 errors in address and time information. Following this block, an 8-bit latch finds and holds the 3-bit magazine address and 5-bit row address, referred to in Fig. 4, after a two-character holding time, inserted to allow the two four-bit words (or one three-bit word and a five-bit word) to be assembled.

Parity checks on character words are performed by the parity block, operating from the main data line, its output determining the acceptability or otherwise of a word.

The rest of the input processor is concerned with the selection of a page by the viewer, who will be provided with three thumbwheel switches or a keyboard with ten number keys and keys for several other functions. A page having been "dialled in", the row address latch block examines the row address words until row zero is detected — the page header — when the selector will examine the following address information to compare it with the required page keyed in by the viewer. On detection of the required page code,

|         | Bits    | 67-<br>5 | 6       |                 | ° ° °       | 0 <sub>01</sub>               | 0   | 1 0 | 0 | 1 1 | 1 ( | ) 0            | 1 (                            | <sup>)</sup> 1   | 1 | 0 | 1 1  | 1   |

|---------|---------|----------|---------|-----------------|-------------|-------------------------------|-----|-----|---|-----|-----|----------------|--------------------------------|------------------|---|---|------|-----|

| b4<br>↓ | b3<br>↓ | ₽5<br>₽  | b1<br>↓ | Column<br>Row j | 0           | 1                             |     | 2   |   | 3   | 4   |                | Ę                              |                  | e | 5 | 7    | · ] |

| 0       | 0       | 0        | 0       | 0               |             |                               | SP  | 田   | 0 |     | @®  | 00             | Ρ                              | Р <sup>3</sup>   | ٢ |   | р    | Ħ   |

| 0       | 0       | 0        | 1       | 1               |             | Graphics<br>Red               | 1   |     | 1 |     | Α   | Α <sup>3</sup> | Q                              | Q <sup>(3)</sup> |   |   | q I  |     |

| 0       | 0       | 1        | 0       | 2               |             | Graphics<br>Green             | ti  |     | 2 |     | в   | в <sup>3</sup> | R                              | R <sup>3</sup>   |   |   | r    |     |

| 0       | 0       | 1        | 1       | 3               | /////////// | Graphics<br>Yet low           | £ 3 |     | 3 |     | С   | с 3            | S                              | S <sup>(3)</sup> | с |   | s    |     |

| 0       | 1       | 0        | 0       | 4               |             | Graphics<br>Blue              | \$  |     | 4 |     | D   | DÛ             | Т                              | €, T             | d |   | t    |     |

| 0       | 1       | 0        | 1       | 5               |             | Graphics<br>Magenta           | %   |     | 5 |     | E   | E <sup>3</sup> | U                              | UĴ               | е |   | u    | E   |

| 0       | 1       | 1        | 0       | 6               |             | Graphics<br>Cyan              | &   |     | 6 |     | F   | F <sup>ا</sup> | V                              | V D              | f |   | v    | 2   |

| 0       | 1       | 1        | 1       | 7               |             | Graphics<br>White             | •   |     | 7 |     | G   | G <sup>J</sup> | W                              | w <sup>3</sup>   | g |   | w    |     |

| 1       | 0       | 0        | 0       | 8               |             |                               | (   |     | 8 |     | н   | н Э            | Х                              | Х 3              | h |   | x    |     |

| 1       | 0       | 0        | 1       | 9               |             | Alpha <sup>n</sup><br>Red     | )   |     | 9 |     | 1   | 3              | Y                              | Y 3              | i |   | У    |     |

| 1       | 0       | 1        | 0       | 10              |             | Alpha <sup>n</sup><br>Green   | ×   |     | : |     | J   | J ③            | Z                              | Z <sup>3</sup>   | J |   | z    |     |

| 1       | 0       | 1        | 1       | 11              |             | Alpha <sup>n</sup><br>Yellow  | +   |     | ; |     | κ   | к 3            | ۵                              | , [ 3            | k |   | { ②  |     |

| 1       | 1       | 0        | 0       | 12              | Flash       | Alpha <sup>n</sup><br>Blue    | ,   |     | < |     | L   | L <sup>③</sup> | $\backslash^{\textcircled{2}}$ | \<br>€/          | I |   |      |     |

| 1       | 1       | 0        | 1       | 13              | Steady      | Alpha <sup>n</sup><br>Magenta | -   |     | = |     | м   | м <sup>3</sup> | ] ②                            | ] ()             | m |   | } ®' |     |

| 1       | 1       | 1        | 0       | 14              | End Box     | Alpha <sup>n</sup><br>Cyan    | •   |     | > |     | N   | N <sup>③</sup> | 1                              | <b>▲</b> ②<br>①  | n |   |      |     |

| 1       | 1       | 1        | 1       | 15              | Start Box   | Alpha <sup>n</sup> White      | 1   |     | ? |     | 0   | 0 3            | _                              | _                | 0 |   | DEL  |     |

rectangle showing numbers to the individual cells

Notes

- ① This character code (position 0/3) is reserved for internal use by broadcasters.

- O UK version of national use character in the ISO-7 code

- 3 In the graphics mode when bit 6 = 0 the corresponding alphanumerics mode character should be displayed

- (4) All character rows start in the 'Steady', 'Alphanumeric White' and 'unboxed' condition, without control characters

Fig. 5. Characters possible in a Teletext display. Graphics are not in the ROM, being produced directly by the data bits.

the data which follows is written into the store, assuming that the parity checker is in agreement.

The outputs of the input processor are taken to the store and are (a) the 7-bit data (b) the "write" or "reject" command to the store (c) the row address and (d) the character address.

Store. Storage can take many forms, but the most convenient way to store the data while the page is assembled is the random-access memory, which is an array of semiconductor devices, often bistable circuits, set to "1" or "0" by input signals and which can be interrogated non-destructively when required by examining any desired location in the memory. No "order" is entailed: data can be lodged at any part of the memory.

Data are stored in 7-bit code as received from the 7-bit latch driving the data line in Fig. 7.

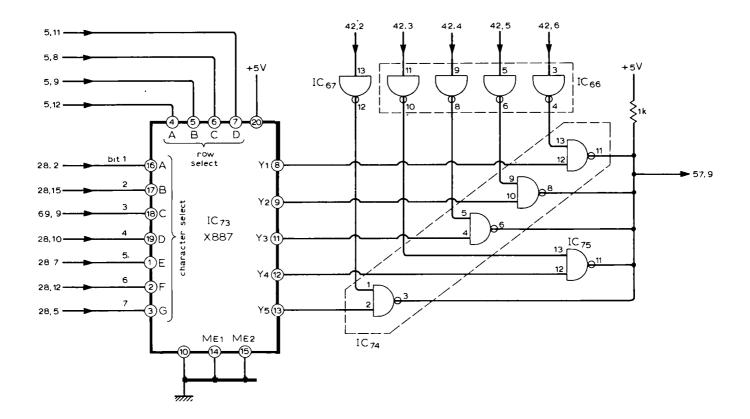

Display. The display of characters depends on the use of a large-scale integrated circuit - another form of store called a read-only memory. This is again an array of memory cells, but this time the pattern of bits read out of a given address in the memory is not under the control of the user. The form of the data is decided at the time of manufacture to perform a variety of functions, but the one in a Teletext decoder is a character generator, arranged to contain the characters shown in Fig. 5. Bits 1-7 in the configurations shown on the left, control the selection of display at the output. Bits 1-4 determine which row of character bits should be read out, while bits 5-7 indicate the column. For example, if the seven bits from the store were 0011010, bits 7, 6 and 5 (001) indicate that one of the undisplayed control characters in column 1 should be generated and bits 4, 3, 2 and 1 show that ROW 10 - alphanumerics, green - is required. The use of this invisible control character means that the visible, succeeding character shall be a green alphanumeric one, as opposed to the graphics alternative in columns 2, 3, 6 and 7. The next group of bits could be 1101001, in which case the result would be a green, lower-case "i" on the screen. A control character is not displayed, so that whenever the mode is changed — from alphanumerics to graphics or from picture to insert or from white to red — a space must appear.

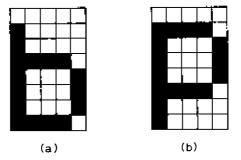

There is one exception to this, and the space can be avoided when an alphanumeric character is needed close to graphics, with no control character space. Although the graphics characters are shown in Fig. 5, it is not meant to imply that they are contained in the ROM. Only the alphanumeric characters are held in the memory, the graphics being generated directly by the 7-bit code as received, as shown in Fig. 5. The area occupied by a character and its surrounding space can be separated into six "cells" which each have a bit of data allocated to them. All codes intended for display as graphics have a 1 as bit 6. However, if, while in the graphics mode, a code occurs with a 0 as bit 6, then those characters in columns 4 and 5 of Fig. 5 will be displayed - a limited selection of alphanumerics, termed "blast-through" alphanumerics.

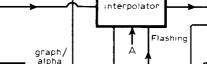

Fig. 8 shows the output processor, complete with character generator and timing circuits, synchronized by line and field sync pulses. Characters are built up from dots at the 7MHz clock frequency and a dot clock is therefore required. The number of elements or dots in the width of a character is six (5 in the character and a space) and a

Fig. 7. The input processor block diagram.

6-counter produces an output at each character. These two outputs are used to serialize the outputs of the ROM, and a 40-counter with a 6-line output is applied to the store, instructing it to provide successive character codes to the ROM which generates the pattern for each new character.

Line sync is also applied to a "divide-by-10" counter, which ensures that the store addresses the ROM for 10 lines in each character, giving 7 scanning lines for the character and 3 scanning lines space between characters. A 24-counter addresses the 24 rows of data in the store.

A further block in the display circuitry is the controls decoder which recognizes the control characters in columns 0 and 1 of Fig. 6, to produce RGB drives, blanking to provide a box Fig. 6. The framing code in progress through the shift register, and in position on the 10th row down. At no time other than at coincidence are more than 5 bits in the register in correspondence with the reference word 11100100.

for inserts and a "flashing" instruction. Graphics are produced, under command from the controls decoder, by the graphics generator on the principle previously mentioned and illustrated in Fig. 5.

Finally, the interpolator can be used to obtain a slightly improved appearance to characters which include a diagonal (Y, Z, K, etc.). The principle is to take advantage of the fact that interlacing effectively provides 14 lines

in a character, not 7, and to "fill in" the steps produced by the 7 stored lines. An odd/even field command can be derived and used to synchronize the interpolator, which is also used to make the flashing signal effective.

That is the principle of the decoder, very briefly. In a short article, it is not possible to cover all aspects and it was not the intention. Forthcoming articles will describe the circuit in detail and provide complete information on the construction of a decoder that will differ from this general picture in several respects. Many savings in cost have been found possible by circuit changes which have also made possible a unit which is much smaller than envisaged.

(To be continued)

#### References

1. Gassman, G.-G. "Twelve Sound Channels during the Vertical Sync Interval of the Television Signal", ITT Chicago Spring Conference, June 1970.

2. Ball, J. D & Wells, D. R. "Encoded captioning of television for the deaf". International Television Symposium, Montreux, 1973.

3. Guillermin, J., Dumont, J. & Guinet, Y. "Transmission of remote control and identification signals within audio and video channels in radio and television broadcasting", I.E.E. Conference Publication No. 25, November, 1966.

4 Numaguchi, Yasutaka. "Still Picture Broadcasting System", NHK Laboratories Note No. 174, January 1974.

5. Houghton, W. D. "Homefax – a consumer information system", *RCA Engineer*, Vol. 16, No. 5, Feb / Mar., 1971

6. King, Patrick T. "A Novel Television Add-On Data Communication System", Journal of the S.M.P T.E., Vol. 83, January 1974.

7. Hutt, P R. "A system of Data Transmission in the Vertical Interval of the Television Signal. IBC 1972 Conference Publication No. 88, pp. 131-140.

8. "Specification of standards for information transmission by digitally-coded signals in the field-blanking interval of 625-line television systems". Published jointly by BBC, IBA and BREMA. October 1974.

9. Hamming, R. W. 'Error Detecting and Error Correcting Codes," Bell System Technical Journal, Vol. XXVI, 2 April, 1950.

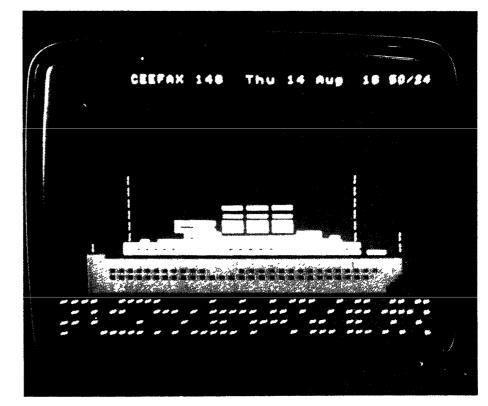

Fig. 10. Extracts from an Oracle index page, showing the normal appearance at (top) and the effect of character rounding (bottom). This is an IBA photograph taken from the screen of a studio monitor. On a domestic receiver, the effect is not as pronounced.

odd /even

graphics

В

1

character

generator

(ROM)

A B

Fig. 8. A typical output processor.

to ram

Fig. 9 An example of the use of graphics.

2—The decoder system

by J. F. Daniels\*

# This article describes the facilities offered by the Wireless World decoder and also covers, in general terms, the methods of installation in a commercial colour receiver. The problems likely to be encountered with such a project are also discussed.

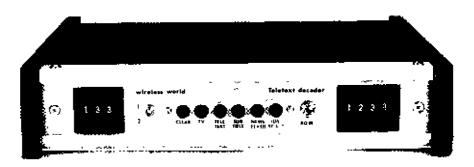

When contemplating the design of a project as complex as this one, there are many factors which have to be considered. For instance, to build a single Teletext decoder with cost and size virtually no object and expensive test equipment available is comparatively easy, but this is of little interest to the home constructor. What is needed is something which can be built relatively cheaply, can be mounted in a small, attractive cabinet, and can be installed and made to work with only the minimum of adjustments, preferably requiring only a cheap multimeter.

This design will fulfil these requirements. This does assume, however, that the unit is constructed without any wiring errors and with no faulty components — in a unit using around 85 i.cs and their interconnexions, there is some room for error!

Not to be too discouraging at such an early stage, however, it should be pointed out that printed circuit boards will be made available, from normal sources, which should eliminate most wiring error problems. Further, digital i.cs tend to be very reliable, in my experience anyway, as long as they are not obtained from one of the sources of unmarked, untested devices. The use of such i.cs in this project must be strongly discouraged, as even if they appear satisfactory on a d.c. test, they may well be out of tolerance on delay time or fan-out, which could have disastrous effects in some parts of the circuit, where correct delay time through i.cs is an important factor.

For the constructor who has access to an oscilloscope, waveform diagrams will be given at various points in the circuit to help those wishing fully to understand the circuit operation.

It is not intended, in this series of articles, to give full constructional details, and the choice of suitable box, and method of mounting p.c.bs etc. is left to the individual constructor. Details of how the unit may be connected into various types of commercial colour receiver will, however, be fully covered and this should leave only problems of a mechanical nature to the individual.

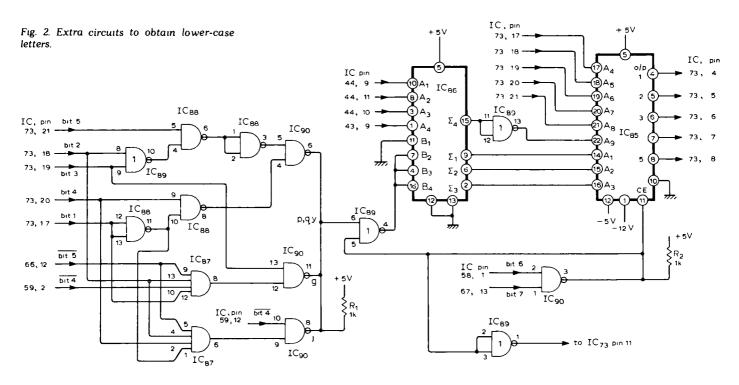

The cost of the decoder will be in the region of £85, and although this may seem a great deal of money to pay, people who have seen the resulting display of pages on the TV screen agree that the service is well worth while and has great potential for the future. The Wireless World decoder will be capable of utilising most of the features currently offered by the system, including display in six colours and white, alphanumeric characters, graphic characters, and flashing display. Two circuit options will be described; one which includes both upper and lower case characters, and another, slightly simpler circuit, with upper case characters only — a worthwhile option for cost conscious contructors. The circuit does not include any form of interpolation (character rounding) because it was thought that the extra cost of about £15-20 was not justified in a discretecomponent decoder of this type.

Before going on to describe some problems, which can be encountered when dealing with commercial TV receivers, it is necessary to describe in more detail the performance of the Teletext decoder.

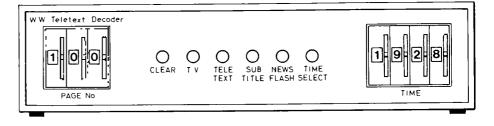

Fig. 1. Suggested front panel layout of the Wireless World Teletext decoder.

#### Operation

The decoder can be built into a box measuring about  $8.5 \times 10.5 \times 2in$ , which is a convenient size to rest on top of a normal domestic TV receiver. The power supply is not included in this box for a number of reasons, some electrical, but mainly to keep down the size and heat dissipation in the decoder unit. Space can usually be found in the cabinet of most domestic TV receivers to take the decoder power supply.

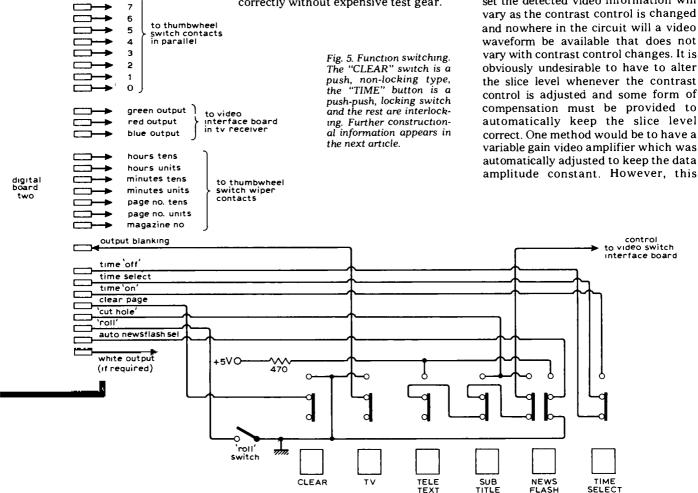

The front panel of the decoder carries two sets of thumbwheel switches, and various other function switches. In the latest version, the function switches take the form of a row of pushbuttons as shown in Fig. 1. The bank of three thumbwheel switches are for magazine and page number selection, the one on the left being for magazine number; the other two for page number tens and units. The bank of four thumbwheel switches are for the selection of timed pages. which may only be transmitted for a one-minute period during each day, and therefore require selection by means of time code and storing, for viewing later. The switches can be set to any given time during a 24-hour period, and in this mode of operation a page will only be written into the store at the time shown on the thumbwheel switches. It should be pointed out here that at the time of writing, no pages are being transmitted in this manner, although the operation of the circuitry can easily be checked, because all pages carry time coding information. However, a cost saving of the order of £6 could be made by omitting this facility.

The row of pushbutton switches mainly controls the form of display on the TV screen. The four in the centre are all interlocked, latching pushbuttons, the one of the left is an individuallyoperating, momentary-action type and the right-hand one is individually latching. The "TV" button merely selects the picture on the screen in the normal manner, although the decoder will still be operative and can store pages in the usual way, ready for instant viewing when the "Teletext" button is pushed. The latter merely replaces the picture with the video output of the decoder and, in this mode, all the normal features of Teletext display are available.

The page header contains a continuously changing time indication in the top right-hand corner, but a fixed page number display — the number of the page selected. When a different page is required on the display, the momentary-action, left-hand button marked "clear" is pushed. This clears all the information from the display except for the page header row, which then starts "rotating" i.e., reading out all the page headers as they are transmitted until the new page number selected is reached, whereupon the new page is read out into the screen.

The next button is marked "subtitle" and is used to select the "insert" mode of operation. When this button is selected, the TV picture is displayed on the screen until the subtitle page, the number of which has been selected on the thumbwheel switches, is detected, when the subtitle message will be read out in a box inserted in the picture. If a new subtitle, or indeed a continuous stream of different subtitles is transmitted, the displayed subtitles will automatically change as they are transmitted. This may be a very useful facility for the future, as subtitles take up very little transmission time in the Teletext waveform, consisting of only a few rows of information. However, at the present time they are only transmitted in test form.

The operation of the "newsflash" button is somewhat similar to the subtitle button, but with an added facility. After selecting the newsflash page number on the thumbwheel switches, the current newsflash which may have first been transmitted some time ago — is displayed in a box in the TV picture in the normal manner. If, however, the clear button is then pushed, the picture returns to normal. and no data are then displayed until a new newsflash is transmitted, whereupon this is displayed in the usual way in its box. If the current newsflash is required to be seen again, after pushing the clear button, the newsflash button is simply released and reselected.

The next button, marked "time" brings the time-select thumbwheel switches into operation, when the selected page will only be written into the decoder store during the one-minute period displayed on the thumbwheel switches. This page will then be held in the store until either the clear button is depressed or a different mode of operation is selected. This button is not

Fig. 2. Suggested method of connexion into a domestic colour receiver, using an interface board containing three simple electronic video switches.

interlocked with the other buttons so that time-selected pages can be written into the store while watching a TV programme — possibly for later reading during the commercials! The time selection facility is not operative when subtitle or newsflash buttons are selected.

No facility is provided for superimposing the complete Teletext display on the picture, as in the author's opinion this gives a meaningless display which makes both the picture and the Teletext display difficult to interpret.

These, then, are the basic facilities offered by the *Wireless World* decoder. Without doubt, as the Teletext system progresses, more facilities will be offered by the service, and it should not be difficult to add extra facilities to the decoder as required.

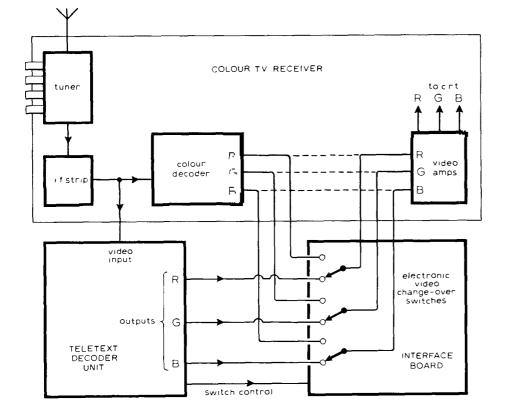

#### Installation

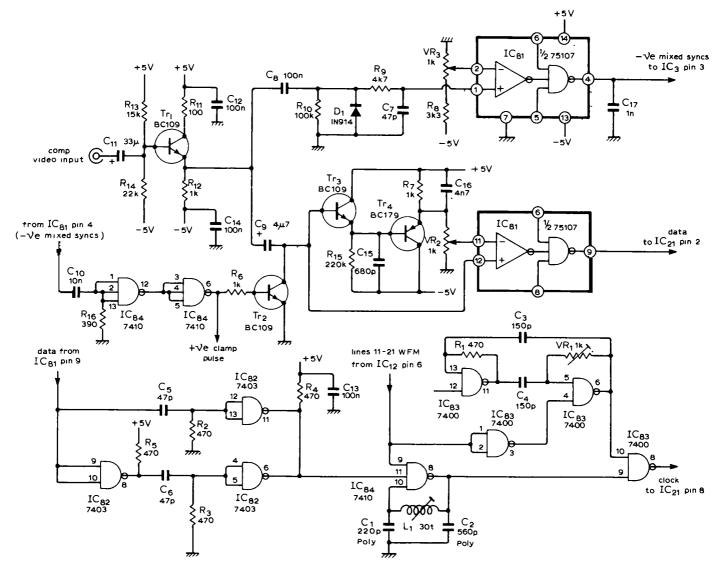

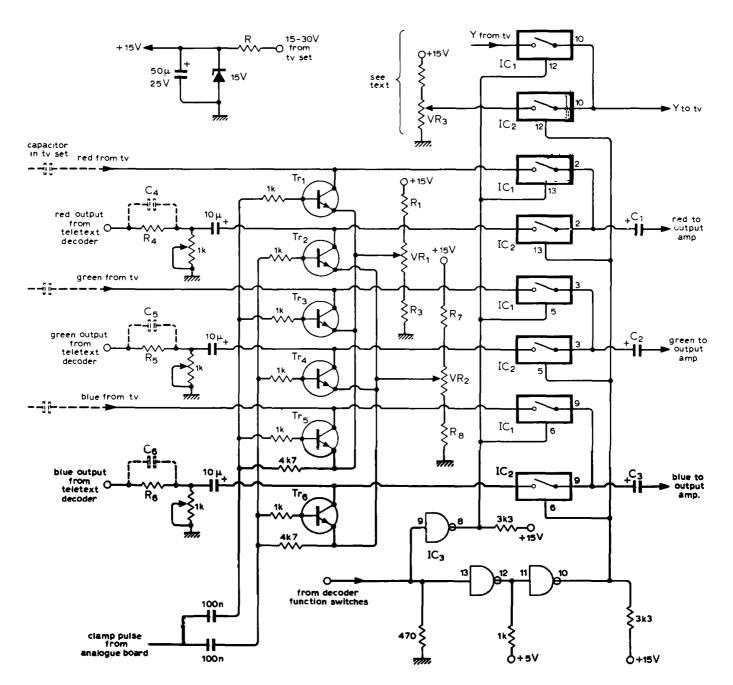

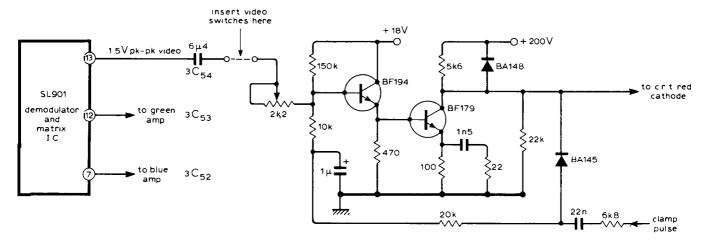

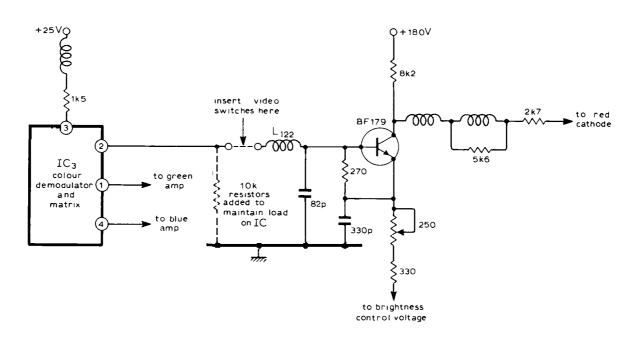

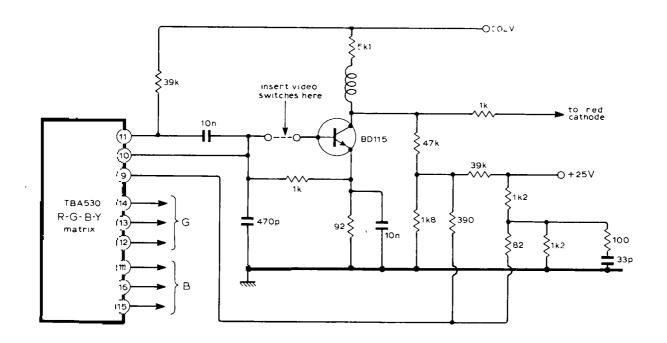

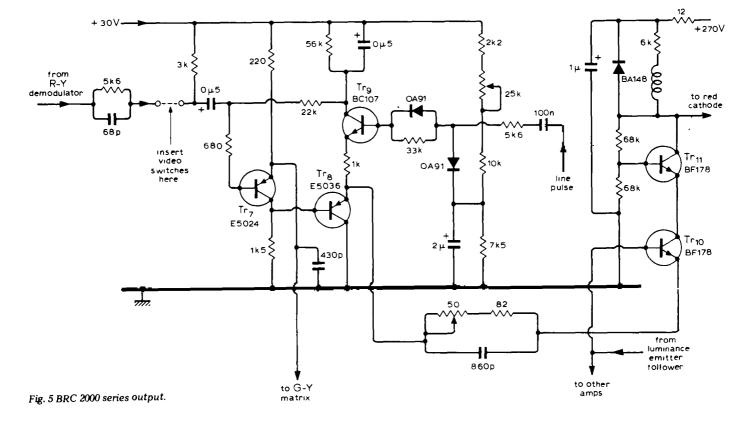

There is really only one satisfactory way to connect the decoder to a domestic colour receiver if all the facilities described earlier are required, and this is shown in Fig. 2. It can be seen from the diagram that there are only four points of connexion into the set: a feed of composite video from the output of the receiver 1.f. strip, and feeds of red, green and blue (or possible R-Y, G-Y and B-Y) to and from the inputs to the receiver video amplifiers. It is possible that a fifth connexion, from the set's flywheel oscillator, will be required if the set is in use in a low signal area and displays a noisy picture, as this can be used to remove horizontal jitter on the Teletext display caused by the noise on the video signal. However, this possibility will be considered later during the circuit description.

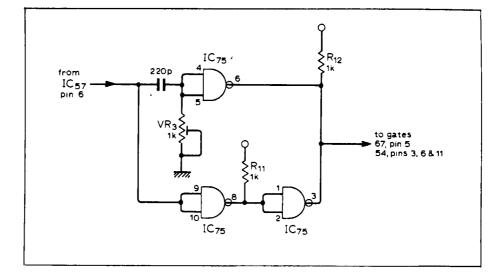

The interface board is a small video switch unit, mounted inside the receiver, fairly close to the video amplifiers, and serves to switch electronically between the picture and the Teletext display, when commanded by either the function switches, or by "hole-cutting information from the decoder. The design of this unit will vary slightly, depending on the type of receiver used, some sets having, R, G and B feeds to the video amplifiers and others using colour difference signals (R-Y, G-Y and B-Y). If the facility of putting newsflashes and subtitles in boxes is not required, then this unit could probably be replaced by a three pole change-over relay, controlled solely by the function switches.

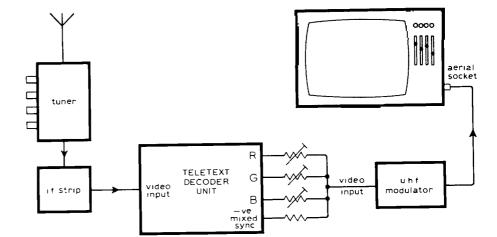

This, then, is the only practical way in which a decoder can be installed into an existing TV set, if a coloured display is required and this is the only method that will be described in detail in this series of articles. However, for those who rent a colour set, there is another, somewhat less attractive possibility, shown in Fig. 3. Here, a separate tuner and i.f. strip are used to provide video for the Teletext decoder. The R, G and B outputs of the decoder are then matrixed together, and fed to a u.h.f. modulator. This in turn feeds the aerial socket of the receiver, which is tuned in to the modulator on an unused channel. This will, of course, only give a monochrome display, but would at least have different shades of grey to represent different transmitted colours.

It is not practical to modulate the decoder display into PAL colour form, partly because of the high cost of a colour coder, but mainly because the results woule be unsatisfactory due to the fact that the bandwidth of the PAL system would be insufficient to cope with the Teletext display waveform.

#### Data signal

Before starting a description of the decoder block diagram, there are two more important points to be made to prospective constructors. Firstly, there is the question of obtaining a suitably undistorted data signal from the TV receiver.

Distortion of the data waveform can be caused in a number of ways; poor bandwidth or non-linear phase response in the receiver i.f. strip; reflections (ghosting) on the picture, caused either by external multipath interference or aerial mismatching; co-channel interference; and finally noise. All these can cause errors to be made in the data display and, in extreme cases, prevent operation of the decoder at all.

Generally speaking, however, satisfactory results can be expected from the majority of colour sets displaying a ghost-free picture. Noise on the picture, unless of sufficient amplitude to be objectionable, is unlikely to be a problem, as the decoder employs circuits capable of detection and correction of errors caused by noise spikes.

Secondly, the performance of the decoder in the presence of interference in various forms is determined almost solely by the performance of the front end, i.e., the circuitry which separates the data from the video waveform, and converts it into t.t.l.-compatible form. It is proposed to describe first a fairly simple data separator, which is extremely easy to set up and which will be adequate under good reception conditions. This will enable the rest of the digital circuitry to be tested and set up. In a later article a more complex form of data separator will be described which will give an improved performance under adverse signal conditions although it will be rather more difficult to set up initially.

#### Safety

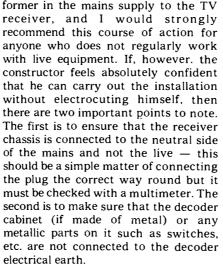

The most important problem of all is one of safety. If the decoder is to be installed in the manner to be described rather than by using a u.h.f. modulator, as mentioned earlier, then a direct connexion must be made to the receiver chassis, which could under some circumstances be live.

There is only one way to prevent the decoder itself from becoming live, and that is to use a mains isolating trans-

Fig. 3. Alternative arrangements for

rented television sets. This has the

white display will be obtained.

disadvantage that only a black and

A three core mains lead must be used, with the earth connexion taken to the decoder cabinet, if this is made of metal. Probably the best solution, though, is to use a wooden cabinet and ensure that the thumbwheel switches and pushbutton switches are suitably insulated from their electrical contacts. The earth connexion should only be made after the decoder has been tested and set up, as it could create a hazard while actually working on the decoder. Of course, after testing is finished, when the earth is connected, protection is ensured against the decoder box becoming live due to faulty insulation.

#### Construction

Prototype decoders were constructed on  $12 \times 7$ in pieces of ordinary Veroboard 0.1in matrix sheets. There is no reason why this method of construction should not be used, apart from the fact that it is very laborious, and wiring errors can easily be made.

For those who have less time to spare, printed circuits will be available in the form of two large p.c.bs for the digital circuitry, and a smaller p.c.b. for the analogue circuits. The overall size of the unit has been kept down by splitting up the boards in this way.

The large boards measure  $9\frac{1}{2} \times 5\frac{1}{2}$  in, and are arranged to mount one above the other, spaced about  $\frac{1}{2}$  in apart. The analogue board measures  $5\frac{1}{2} \times 3$  in and is spaced  $\frac{1}{2}$  in above the digital boards. This gives an overall size for the decoder electronics of about  $9\frac{1}{2} \times 5\frac{1}{2} \times$  $1\frac{1}{2}$  in. The digital boards, which each hold about 40 i.c.s, are double sided, but for cheapness do not have platedthrough holes. The "plating through" process is carried out by the constructor, using tinned copper wire soldered on both sides of the board.

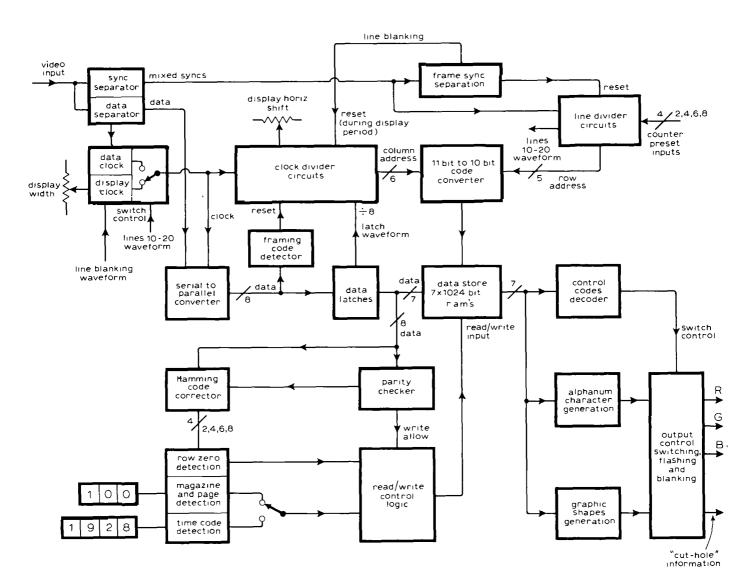

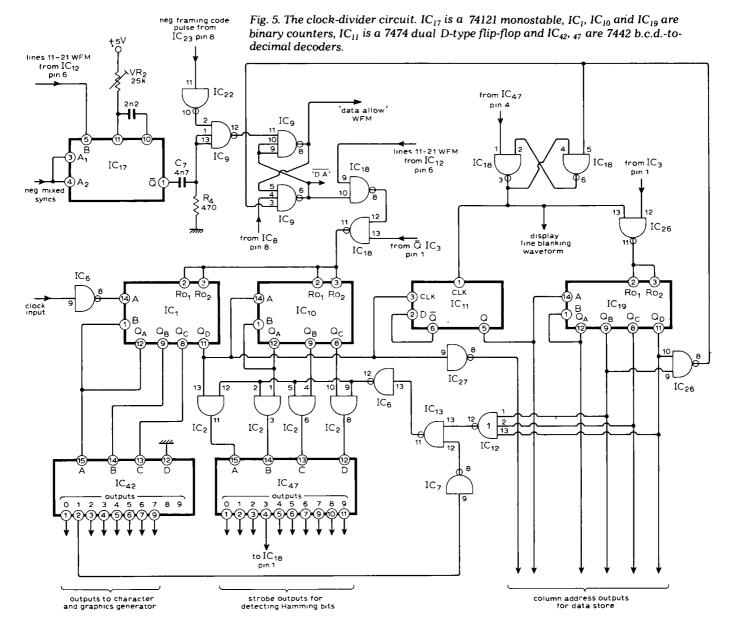

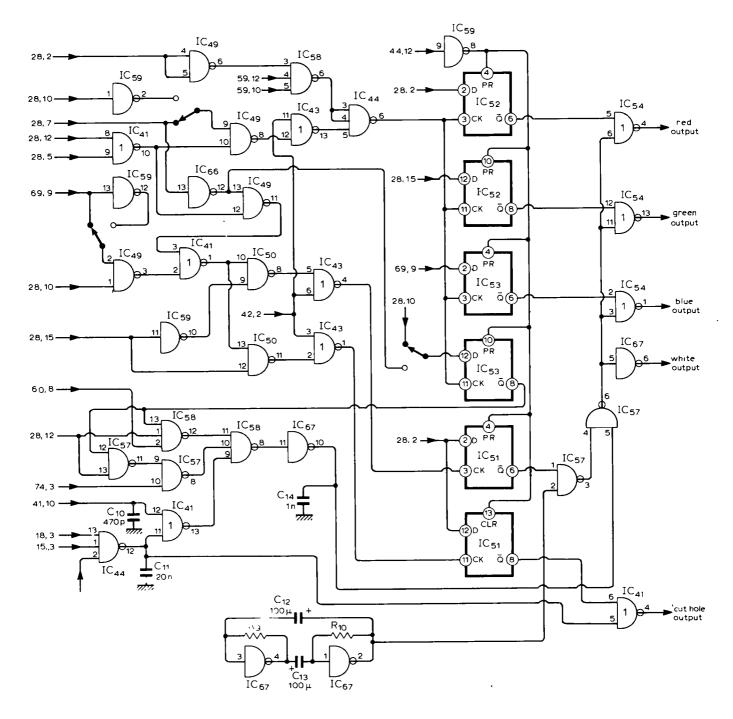

This simplified block diagram in Fig. 4 shows the main functions contained in the decoder, only the main data paths being shown for simplicity. The heart of the circuit is contained in the clock and line divider blocks, and there are many waveforms from these sources which are distributed to the rest of the circuit blocks. This initial description is only intended as a guide to circuit operation, so that an overall picture can be obtained, before starting a detailed description of each circuit block.

The function of the analogue board is to take the composite wide-band video signal from the receiver i.f. strip, and produce from it t.t.l.-compatible mixed syncs, data, and clock waveforms. The single clock line includes the outputs of two clock generators, one derived from the incoming data, and another freerunning oscillator used during the display time. Switching between the oscillators is achieved by using a waveform from the line divider circuits, which switches from the display oscillator to the "data locked" oscillator during part of the field blanking interval (between lines 10 and 20). The free-running oscillator has a preset frequency adjustment which controls the width of the Teletext display, and is also triggered by a line blanking wavefrom to ensure that it starts up in the same phase at the start of each television line.

Clock and data waveforms from the analogue board are fed to the serial-toparallel converter, which in turn feeds the data latches and the framing-code detector. The output of the framing code detector is used to reset the clock

dividers, and a  $\div 8$  clock waveform is in turn used to operate the data latches.

It should be explained at this point that the clock and line dividers perform the dual role of data aquisition and data display dividers, and this constitutes quite a saving in circuit components.

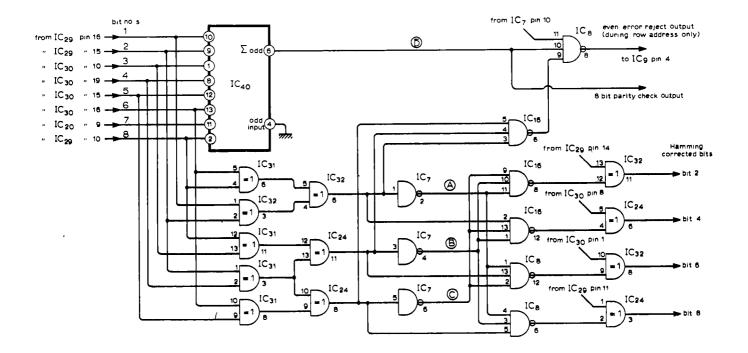

Bits 1-7 from the data latches are fed straight to the inputs of the data store, while all eight bits are fed to the parity checker and Hamming-code corrector. The output of the Hamming corrector consists of bits 2, 4, 6 and 8, suitably corrected in the case of a single error, and also an output which indicates an even number of errors. If an even error is detected during a row address group, then the even error output of the Hamming corrector is used to inhibit any data from being written into the store on this row.

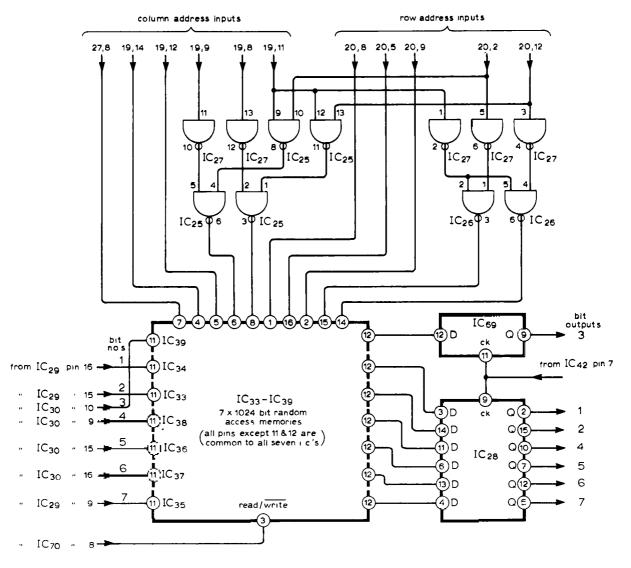

Bits 2, 4, 6 and 8 from the Hamming corrector are fed to the row and page recognition circuitry, and also to the line divider circuits. The line divider circuits count line syncs during the display period, but when data lines are detected during field blanking, the counters are preset to the correct row number, indicated by the Hammingcorrected bits. The five-bit row-address output of the line dividers is fed, together with the six-bit column-address output of the clock dividers, to the code convertor circuit. ("Column address" refers to the 40 vertical character columns and "row address" to the 24 horizontal character rows.)

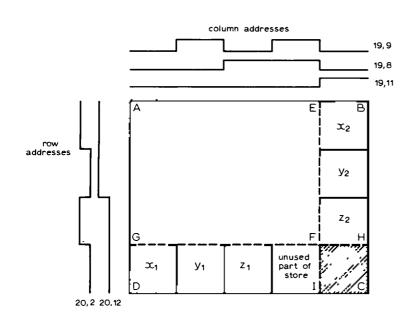

The divider circuits are both arranged so that the data on these eleven wires is correct during both data aquisition and data display, and this obviates the necessity of complicated switching in the address inputs to the store. The code convertor is required for the following reason' the 1024-bit random-access memories are arranged in a 32  $\times$  32 matrix which can, of course, be addressed in any of its store positions by a 10-bit address input. Our display matrix, though, is arranged in a  $40 \times 24$ pattern as previously described, and this requires an 11-bit (6 + 5) code to address each individual position. However, there are many unused positions which can be addressed by the 11-bit code and by a suitable rearrangement of the addresses, the 11-bit code can be reduced to 10 bits, without actually losing any of the 40  $\times$  24 matrix positions. A simple calculation showing that 40 multiplied by 24 comes to less than 1024 indicates this possibility.

Fig. 4. Teletext decoder simplified block schematic.

The data store consists of seven 1024-bit random-access memories, addressed in parallel – one for each of the seven bits of data. The other input to the store is the read/write input. This input is normally in the read condition, when data already in the store is read out onto the screen, but changes to the write condition during Teletext data lines 17 and 18, when instructed to do so by the read/write control logic.

The seven-bit output of the data store is fed in parallel to three circuit blocks, as shown. Alphanumeric characters and graphic characters are generated for each of the 960 display positions on the screen. The control codes decoder decides which will actually be displayed, what colour it should be, and whether or not it ought to be flashing or boxed. It does this by suitable switching in the output control unit, which also blanks control characters.

This, then, is a necessarily brief introduction to the Wireless World. Teletext decoder. In the following articles, detailed descriptions of each of the circuit blocks will be given, with waveform diagrams and explanations where these are relevant. Finally, circuits will be given for various types of "interface" board.

(To be continued)

3 — Line and clock dividers

by J. F. Daniels

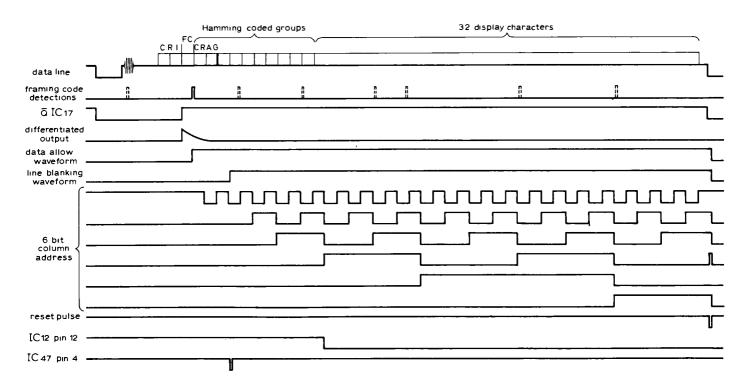

Last month we looked briefly at the overall operation of the decoder by considering a simplified block schematic diagram. I also mentioned that the heart of the circuit lay in the design and operation of the clock and line divider circuits. This month we shall look in greater detail at the operation of these two circuit blocks, as these together provide most of the waveforms used elsewhere in the decoder circuitry. We shall begin by looking at the operation of the line dividers.

The main function of this part of the circuit is to provide row-address information for the store during the operation of writing data into the store and when reading it; i.e., when the data is displayed as characters on the screen. Other outputs are also obtained from this part of the circuit, namely separated field syncs, line address information for the character generater read-only memory, the vertical component of the display blanking waveform and a field blanking waveform which goes to "1" during the period from lines 11 to 21 and 324 to 334. This latter waveform is used extensively elsewhere in the decoder to

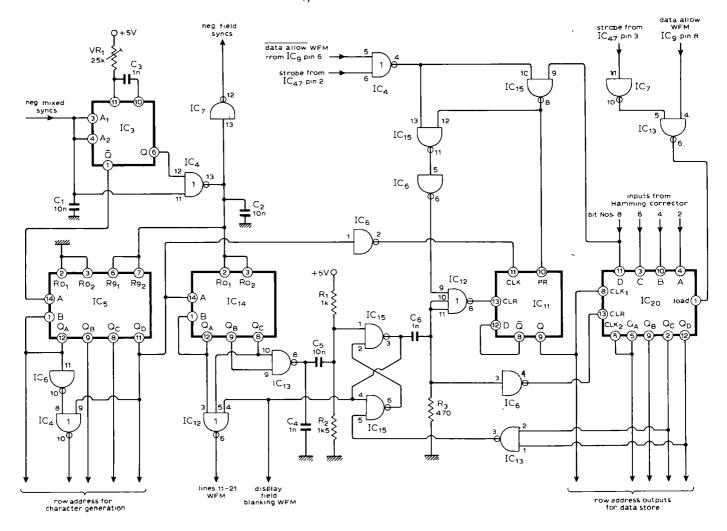

Fig. 1. The line divider circuitry.  $IC_3$  is a 74121 monostable,  $IC_5$  and  $IC_{14}$  are 7490 decimal counters,  $IC_{11}$  is a 7474 dual D-type edge-triggered flip-flop and  $IC_{20}$  is a 74177 / 74197 binary counter.

discriminate between data acquisition and data display: i.e., data is only "looked for" during the periods just mentioned. If all 625 lines' were examined for data, false framing codes would be detected at random during the video information, and cause lines of "rubbish" to be read into the store. It would of course be possible to look for data only on lines 17-18 and 330-331, but it is possible that broadcasters may change the positions, or increase the number, of data lines transmitted, and so the above method was adopted to avoid later modification in this respect.

It may appear, from a quick glance at the circuits, that the i.cs are numbered somewhat erratically, but this is

because they are designated according to their position on the p.c. boards –  $IC_{1.40}$  being on the uppermost board and  $IC_{41.80}$  on the lower circuit. During circuit descriptions, multigate i.cs will be referred to by their IC number, and output pin number. For example (7, 12.) indicates the inverter gate for field sync pulses in Fig. 1.

#### Line dividers

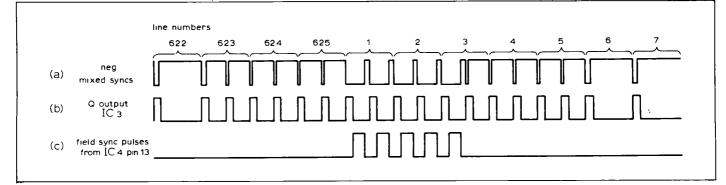

Negative-going mixed syncs from the analogue board trigger monostable 3, which is adjustable by means of a preset potentiometer. Elswhere in the circuit the variable width of the output pulse is used to shift the display horizontally, but for this part of the circuit the output pulse width is not critical, so long as the pulse is wider than the input sync pulse. By gating together the input and output waveforms of this i.c. in a NOR gate (4,13), the broad pulses during the field blanking interval are separated from the mixed sync waveform. Capacitor  $C_2$

Fig. 2. Waveforms from Fig. 1, showing the detection of broad pulses.

removes spikes which are caused by the delay through  $IC_3$ . The method by which the broad-pulse separation is achieved is more clearly shown by Fig. 2. waveforms (a), (b) and (c).

The broad pulses are used to reset the first part of the line-divider chain, which consists of two i.cs forming a divide-by-80 circuit. The first i.c., a divide-by-10 counter, provides lineaddress information for the character generater r.o.m. and sets the height of each "character box" at 10 lines per field.

In the "upper case only" version of the decoder, only seven of these lines

Fig. 3. Waveforms in the circuit of Fig. 1.

are used for the display of alphanumeric characters, and gates (6,10) and (4,10)serve to inhibit character generation during three of the ten lines. These gates are not required when the upper and lower case version is built, as the blanking of unused character lines is achieved in a later part of the decoder.

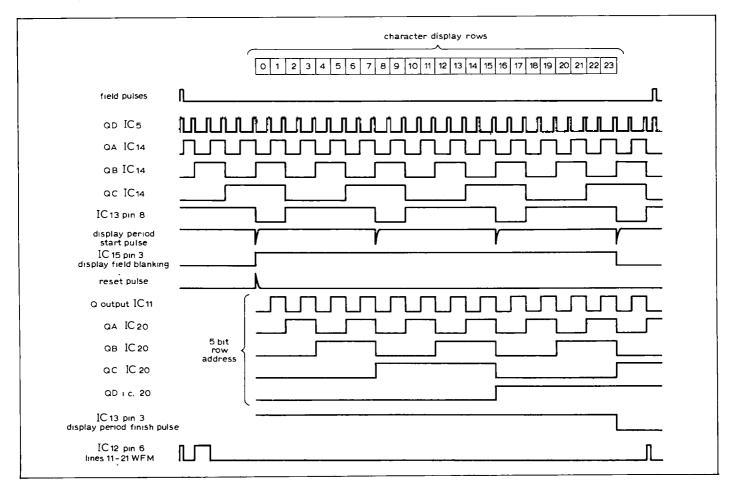

The operation of the rest of the circuit is best understood by referring to Fig.3, which shows some of the more important waveforms through the circuit. The divide-by-8 counter  $IC_{14}$  is fed with one pulse every 10 lines from IC<sub>5</sub> and its outputs  $Q_B$  and  $Q_C$  are gated in (13, 8) to provide a start pulse for the display period at line 51 (also 364).  $C_4$  removes any spikes caused by timing differences between the  $Q_{\!B}$  and  $Q_{\!C}$  outputs of the counter, and  $C_5$ ,  $R_1$  and  $R_2$  shorten the pulse into a narrow negative spike to set the vertical display-blanking flip-flop, formed from gates (15, 3) and (15, 6). The positive transition at the output of gate (15, 3) is coupled via  $C_6$  and  $R_3$  into gates (12, 8) and (6, 4), which has the

effect of setting the outputs of the 5-bit counter, formed from ICs 11 and 20, to zero. From this point onwards, the 5-bit counter counts through the characterdisplay rows until the counter reaches 24 (the end of the page display). This point is detected by gate (13, 3) and its output is used to reset the vertical display-blanking flip-flop.

During lines containing data the 5-bit counter is preset to the correct row number, which is available in binary form at the output of the Hamming corrector during the control and row address groups, at the start of each data line.

The time at which this data is entered into the presettable counter is controlled by gates (4, 4) and (13, 6). The least significant bit of the row address arrives first, and a strobe pulse from the clock divider circuits (to be described later in this article) set  $IC_{11}$  at the appropriate time. The next data group to arrive contains the remaining four bits of row address information and this is written into IC<sub>20</sub>, again at a time determined by a strobe pulse from the clock divider circuits. The other inputs to gates (4, 4) and (13, 6) are waveforms which only allow the strobe pulses to set the counters during lines which have been confirmed as containing valid information. These waveforms are used in a number of places in the decoder and we shall call them data allow (DA), for a waveform going to "1" when a framing code is detected and returning to "0" at the end of that line and DA for its inverse.

A 3-input NOR gate (12, 6), provides the field blanking waveforms which goes to "1" during lines 11 - 21 (324 – 334), by gating together the  $Q_A$  and  $Q_C$ outputs of IC<sub>14</sub> together with the vertical display-blanking waveform. It can be seen from the waveform diagram in Fig.3. that this waveform also goes to Fig. 4. Layouts of typical rows of data bits. A display row (row 5 of magazine 1) is shown at (a) and at (b) is a page-header row.

"1" during the equalizing and broad pulses. This is of little consequence, however, as no video is present on these lines so that no false framing codes could be detected here.

Before continuing with a description of the clock divider circuits, it would be as well to consider in greater detail how each of the data rows is made up.

#### **Data row format**

Display row. The data bits are transmitted in groups of eight, and each line of data contains 45 of these groups, or bytes. The first five groups have the same function on all rows and a typical row is shown in Fig. 4(a). The following 40 groups consist of 1S0-7 coded characters, the eighth bit in each group being used as an odd parity bit. The magazine number and row address information are coded in a different manner from the display data, being more heavily protected in a form of Hamming coded. Only four useful bits, of data can be extracted from each of these eight-bit groups, but a single error in the group can be corrected and an even number of errors i.e., 2, 4 or 6 bits in error, can be detected.

**Page header row.** The page-header row (row zero) contains eight more of these Hamming protected groups following the row address number, and only 32 groups of 1S0-7 coded data for display, as shown in Fig. 4(b). The two groups immediately following the row address number contain the page number units and tens respectively and these together with the three bits allocated to

the magazine number, enable any combination of page numbers between 100 and 899 to be selected.

The next four groups contain information indicating the time of day. The first group contains four bits of "minutes units" information and the second, three bits for the minutes tens. The spare bit in this second group is used as a "clear page" control, which goes to "1" whenever the following page contains new information and the old page must be erased from the store. The next group contains a 4-bit "hours units" message and the fourth group contains a 2-bit "hours tens" indication. There are two unused bits in this group, the first being used to indicate a newsflash page, and the second a subtitle page.

#### **Clock dividers**

There are two more groups of Hamming-protected data before the page header display starts, and these will eventually contain more control information.

The clock-divider circuit block provides a large number of pulses and waveforms for use elsewhere in the decoder, as follows: a display lineblanking waveform which goes to "1" during the 40-character-wide display period; the "data allow" waveform which goes "1" on detection of a framing code and returns to zero 42 bytes later; 6-bit column-address for addressing the store, which is used when writing data into the store, and when reading from display; strobe pulses which discriminate between the Hamming-coded words in normal rows and in the page header row and finally, groups of pulses used elsewhere for the formation of the vertical elements of the alphanumeric characters.

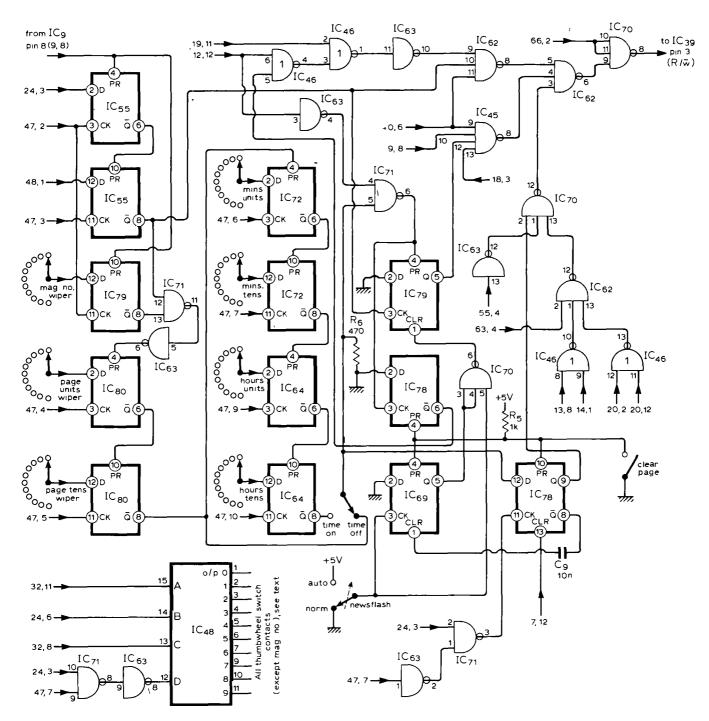

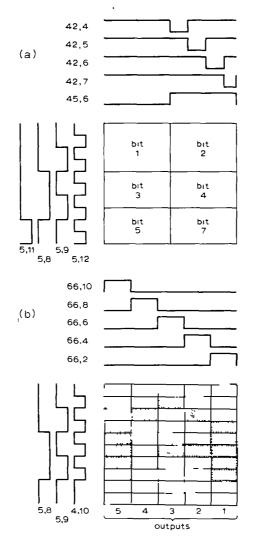

Figure 5 shows the clock-divider circuit diagram, and Fig. 6 the associated waveform diagrams.

Fig. 6. Waveforms seen in the circuit of Fig. 5 during data lines.

#### Wireless World, January 1976

Write mode. Detected framing code pulses, which are one clock pulse wide (144ns) and negative-going, are inverted in gate (22,10) and fed into gate (9,12)together with the differentiated output of monostable 17. This is the "framingcode allow" monostable and its differentiated output is about 2µs wide and timed to occur at the time of the frame code, ie, about 15µs after the start of line syncs. In this way, only valid framing codes are allowed through gate (9,12). This method was used to avoid allowing through random framing codes detected in the colour burst, which can occur with certain types of data-slicing circuit. The monostable triggering is inhibited by means of the B input on all except lines 11-21. The valid framing codes are then used to trigger the "data allow" flip-flop made up from gates (9,8) and (9,6). During lines 11-21, the first two clock-divider i.cs are held in the reset condition until the DA-waveform, goes to "1" (18,8 and 18,11) i.e., until the frame code occurs. It should be noted that i.cs of the 74H series are specified for gates 22 and 9. Although all the prototype decoders worked satisfactorily with ordinary gates here, it would be possible under worst-case conditions for the time delay between detecting the framing code and removing the reset from the dividers to exceed the maximum permissible time of 144ns. By using 74H series gates, the time delay will always be less than 144ns, even under worst-case conditions of supply voltage and gate delay.

A second binary-to-decimal decoder  $IC_{47}$  is connected to the outputs of the second clock-divider i.c. after they have passed through the four AND gates of  $IC_2$ . These gates serve to allow the outputs of IC47 only during the "allow" waveform at the output of gate (6,12). This waveform consists of narrow, positive-going pulses derived from decoder 42, gated with a waveform which only allows the pulses for the first 13 bytes of data. The output pulses of decoder 47 then become narrow, negative-going pulses, timed to occur one during each byte of data from byte 3 to byte 12: i.e., decoder 47 output 1 occurs during byte 4 - output 9 during byte 12. These pulses are used to time each group of Hamming coded bits in the row and page recognition circuitry, and for presetting the line divider i.cs as mentioned earlier.

**Read mode.** Resetting of the clock dividers in during the "read" mode is

The final prototype decoder, which measures about  $40 \times 22.5 \times 6$ cm. The ROLL switch enables pages to be viewed in rapid succession. We understand that a complete kit of parts for the decoder will be available from Catronics Ltd, 39 Pound Street, Carshalton, Surrey.

The newest character code, which is now in use Reference 1 indicates that these undefined control characters will be allocated in order of decreasing serial number. Codes referenced 2 are to assist compatibility with standard data codes All character rows start in the "steady, alphanumeric white" condition, unboxed and unconcealed unless control characters indicate the contrary.

|    | Bits |         | b7 ►<br>b6 ►<br>b5 ► | ° ° °           | ° <sub>0</sub>                | 0 <sub>1 0</sub>        |    | 0 1 1 |   | <sup>1</sup> <sup>0</sup> <sup>0</sup> |      | <sup>1</sup> 0 1 |                | <sup>1</sup> <sup>1</sup> 0 |   | <sup>1</sup> 1 1 |                |   |

|----|------|---------|----------------------|-----------------|-------------------------------|-------------------------|----|-------|---|----------------------------------------|------|------------------|----------------|-----------------------------|---|------------------|----------------|---|

| b4 | b3   | b2<br>↓ | b1                   | Column<br>Row ' | C                             | 1                       | ;  | 2     | : | 3                                      | 4    | <u>-</u>         | 5              | 5                           |   | 6                |                | 7 |

| 0  | 0    | 0       | 0                    | 0               | NUL                           | <u>DLE</u> <sup>®</sup> |    |       | 0 |                                        | 0    | @                | Р              | Ρ                           |   |                  | p              |   |

| 0  | Q    | 0       | 1                    | 1               | Alpha <sup>n</sup><br>Red     | Graphics<br>Red         | !  |       | 1 |                                        | Δ    | А                | Q              | Q                           | a |                  | q              |   |

| 0  | 0    | 1       | 0                    | 2               | Alpha <sup>n</sup><br>Green   | Graphics<br>Green       |    |       | 2 |                                        | В    | в                | R              | R                           | b |                  | r              |   |

| 0  | 0    | 1       | 1                    | 3               | Alpha <sup>n</sup><br>Yellow  | Graphics<br>Yellow      | £  |       | 3 |                                        | С    | С                | S              | S                           | с |                  | s              |   |

| 0  | 1    | 0       | 0                    | 4               | Alpha <sup>n</sup><br>Blue    | Graphics<br>Blue        | \$ |       | 4 |                                        | D    | D                | Т              | Т                           | d |                  | t              |   |

| 0  | 1    | 0       | 1                    | 5               | Alpha <sup>n</sup><br>Magenta | Graphics<br>Magenta     | %  |       | 5 |                                        | E    | E                | U              | U                           | е |                  | u              |   |

| 0  | 1    | 1       | 0                    | 6               | Alpha <sup>n</sup><br>Cyan    | Graphics<br>Cyan        | 8  |       | 6 |                                        | F    | r F              | V              | V                           | f |                  | v              |   |

| 0  | 1    | 1       | 1                    | 7               | Alpha <sup>n</sup><br>White   | Graphics<br>White       | '  |       | 7 |                                        | G    | G                | w              | w                           | g |                  | w              |   |

| 1  | 0    | 0       | 0                    | 8               | Flash                         | Concealed<br>Display    | (  |       | 8 |                                        | н    | Н                | x              | ×,                          | h |                  | x              |   |

| 1  | 0    | 0       | 1                    | 9               | Steady                        | Û                       | )  |       | 9 |                                        |      |                  | Y              | Y                           | I |                  | у              |   |

| 1  | 0    | 1       | 0                    | 10              | End Box                       | 0                       | ×  |       | : | 8                                      | J    | J                | z              | Z                           | J |                  | z              | F |

| 1  | 0    | 1       | 1                    | 11              | Start Box                     | ESC <sup>®</sup>        | +  |       | ; |                                        | к    | ĸ                | -              | -                           | ĸ |                  | <sup>1</sup> 4 |   |

| 1  | 1    | 0       | 0                    | 12              | 1)                            | 0                       | ,  |       | < |                                        | L    |                  | 1 <sub>2</sub> | 12                          |   |                  | =              |   |

| 1  | 1    | 0       | 1                    | 13              | 1`                            | 0                       | _  |       | = |                                        | м `, | М                | ->             |                             | m |                  | <sup>3</sup> 4 |   |

| 1  | 1    | 1       | 0                    | 14              | <u> </u>                      | ý                       |    |       | > |                                        | N    | N                | •              | <b>^</b>                    | n |                  | ÷              |   |

| 1  | 1    | 1       | 1                    | 15              | <u>SI</u> ?                   | 1                       | /  |       | 2 |                                        | 0    | 0                | #              | #                           | 0 |                  |                |   |

### 4 -- Framing code detector, error circuits and storage

by J. F. Daniels

Discussion of the serial-to-p'arallel convertor, framing code detector, data latches, Hamming corrector, data store and code converter completes the description of the circuitry contained on digital board one.

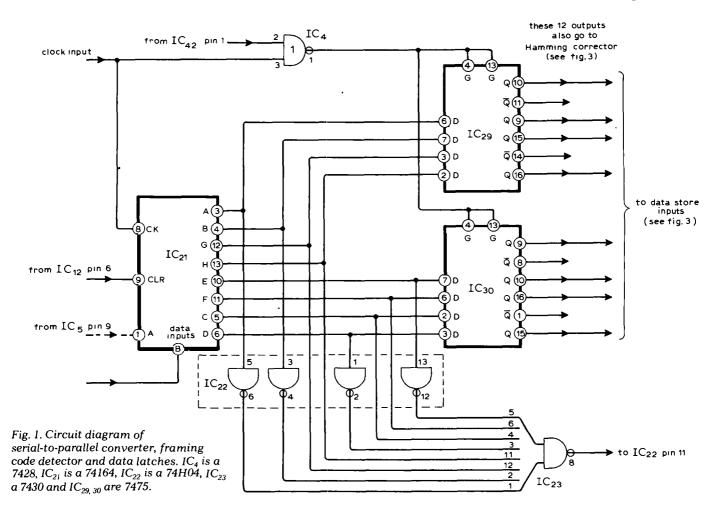

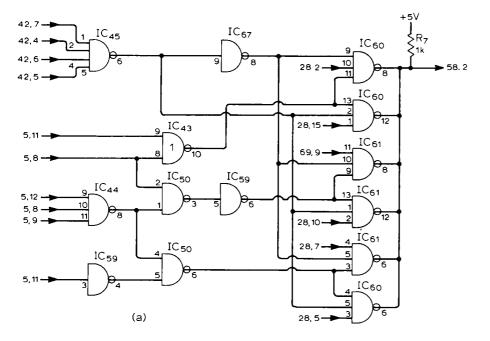

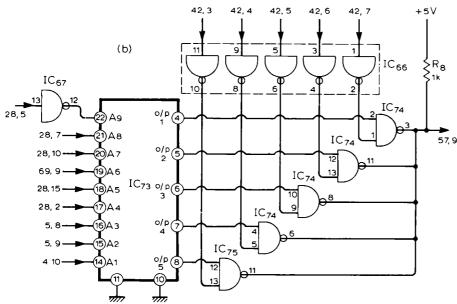

Fig. 1 shows the serial-to-parallel converter, data latches and framingcode detector.  $IC_{21}$  is an 8-bit, serial-in, parallel-out shift register, which presents all eight bits of data in one "byte" to the inputs of the data latches at the same time. A strobe pulse is applied to the data latches, which causes the eight bits of data to be stored in the latches until the next strobe pulse arrives, eight clock periods later. A 7428 buffer i.c. is used for driving the strobe inputs of the latches, as the fan-in requirement of 16 could not be met by the more common 7402, two-input NOR gate. The timing of the strobe pulse is quite critical and it must, of course, occur only when the eight bits of data in each byte are correctly positioned in the 74164 shift register. The detection of the framing-code pulse initially sets the timing of the latch strobe pulses, and subsequently they are derived from a  $\div 8$  output of the clock divider circuit (IC<sub>42</sub>, pin 1).

#### Framing code detection

The framing-code detection circuit consists of only four inverter gates and a single 8-input NAND gate (23, 8). The output of this gate goes to "0" only

when the eight outputs of the shift register are in a condition that causes all "1"s to be present at the gate input. It is possible, with the use of more complex circuitry, to detect the framing code in the presence of a single error, as was explained in the introductory article. However, this added complication will also increase the number of false framing code detections, and this can in some circumstances be more troublesome than the occasional missed framing code. This simple detector was found to be perfectly adequate.

#### Error detection and correction

Before continuing with a description of the parity and Hamming-code correc-

A,B,C & D are parity checks over the following bit no's

| А | checks                   | on | bits | 1 | 2 | 6  | 8   |     |    |   |   |

|---|--------------------------|----|------|---|---|----|-----|-----|----|---|---|

| В | H                        | n  | в    | 2 | з | 4  | 8   |     |    |   |   |

| С | h                        | μ  | н    | 2 | 4 | 5  | 6   |     |    |   |   |

| Ð | n                        | H  | H    | 1 | 2 | З  | 4   | 5   | 6  | 7 | 8 |

|   | 0 = parity check correct |    |      |   |   |    |     |     |    |   |   |