# Semiconductor Circuit Design

Edited by: Bryan Norris, Manager, Applications Laboratory, Texas Instruments Limited

#### Semiconductor Circuit Design

Bryan Norris, Texas Instruments Ltd.

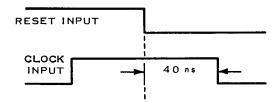

Applications Manager since 1967, and author of the well-remembered Norris Column, has carefully chosen and edited the contents of this book to have reader appeal over a wide range of industries and Electronics users.

The source material has been originated by members of the laboratory who are acknowledged experts in their particular speciality, and most of the subject matter has been recently written, but some older topics are included to provide useful background information.

The Application Laboratory at Bedford is now the largest and best-equipped in the Texas Instruments Corporation and provides a service to world-wide semi-conductor users, through the publishing of Application Reports and solving specific customer Electronic Application problems.

The principal authors contributing here are:

JUREK BUDEK

IAN HARDCASTLE

MICK MAYTUM BOB PARSONS KULDIP RUPRA

## Semiconductor Circuit Design

Edited by: Bryan Norris

Manager, Applications Laboratory,

Texas Instruments Limited

#### **Preface**

The chapters in this book have been chosen with a broad industrial bias to make it readily acceptable and of interest to a wide spectrum of engineers using semi-conductor devices. Each chapter has been written for engineers by a professional specialist engineer in the Texas Instruments Limited, Applications Laboratory in Bedford.

Even if the reader is not in the industrial field, he is likely sometime to be interested, for example, in Inverter design and Chapter X covers this extensively. Also I have yet to meet an engineer not interested in audio amplifier design—extensively covered for both the amateur and professional.

The chapters of the book group together readily to form four sections. The first covers power control with Triacs, Thyristors and Unijunction circuits. The first chapters of this section serve to give fundamentals, with constructions, characteristics and comparisons made between Triacs and Thyristors, followed by their applications in basic circuits. Chapters IV and V describe more specific applications, i.e. burst firing techniques and circuits and a reversible d.c. supply. Chapter VI gives extensive coverage of the theory, operation and circuits of Unijunction Transistors.

Section 2, Power Transistor Applications, concentrates on power supply designs, particularly of the switching mode type, and inverters. Although Chapter VIII talks specifically about a TV application, the regulator design procedure is applicable to all applications.

Section 3 is devoted to the design of audio amplifiers from 1 Watt to over 100 Watts, plus a high fidelity preamplifier.

The final section aims to show how the most widely used family of integrated circuits, i.e. Transistor-Transistor-Logic (TTL), can be applied. Basic descriptions and examples of how counters and registers may be used and connected are given (Chapter XIV), followed by assorted, fairly simple, circuit applications (Chapter XV). The final chapter (XVI) describes how TTL may be safely employed should it's proposed environment be an electrically noisy one.

**BRYAN NORRIS**

Applications and Contracts Manager Texas Instruments Limited April 1972

## **Contents**

## SECTION 1. POWER CONTROL WITH TRIACS, THYRISTORS, AND UNIJUNCTION TRANSISTORS

|             |                           |            |         |         |         |       |       |     | Page |

|-------------|---------------------------|------------|---------|---------|---------|-------|-------|-----|------|

| Chapter I   | TRIACS—THEORY A           | ND GE      | NERA    | L APP   | LICAT   | rions |       |     | 1    |

|             |                           | • •        |         |         | • •     |       |       |     | l    |

|             | Triac Electrical Characte | eristics   | • •     | • •     | • •     |       |       |     | 4    |

|             | TI Triacs                 |            |         |         | • •     |       |       | • • | 4    |

|             |                           |            |         |         | • •     |       |       |     | 6    |

|             |                           |            |         |         | • •     |       |       | • • | 9    |

|             | Cooling *                 | · · · ·    | • •     |         | • •     |       |       | • • | 11   |

|             | Terms and Symbols         | • •        | • •     | • •     | • •     |       | • •   | • • | 12   |

| Chapter II  | TRIACS WITH RESIST        | TIVE A     | ND IN   | DUCT    | IVE L   | OADS  |       |     | 13   |

|             | Triac Operated by a Tri   | gger Dic   | de (for | Resisti | ive Loa | ads)  |       |     | 13   |

|             | Triacs with Inductive Lo  | oads       |         |         |         |       |       |     | 16   |

| Chapter III | SOLID STATE SWITC         | HING I     | ISING   | TRIA    | S AN    | D TH  | YRIST | ORS | 17   |

| Chapter III | Simple Triac switch       |            |         |         |         |       |       |     | 17   |

| 1           | Triac Operated by a Lig   |            |         |         |         |       |       |     | 17   |

|             | Triac Switch Operated b   |            |         |         |         |       |       |     | 17   |

|             | Switching 3-phase Load    |            |         |         |         |       |       |     | 18   |

| 375 <       | Triggering Triacs from a  |            |         |         |         |       |       |     | 18   |

| )           | Using a Triac to Change   |            |         |         |         |       |       |     | 19   |

|             | Light Sensor/Thyristor (  |            |         |         |         |       |       |     | 20   |

| į           | Switching D.C. Solenoic   |            |         |         |         |       |       |     | 21   |

| Chapter IV  | BURST FIRING TECH         |            |         |         |         |       |       |     | 22   |

| Chapter IV  | Voltage and Power         |            |         |         |         |       | • •   | • • | 22   |

|             | Burst Firing using a Tra  |            |         |         |         |       | • •   | • • | 23   |

|             | Burst Firing by Mark Sp   |            |         |         |         |       | • •   | • • | 26   |

|             |                           |            |         |         |         | • •   | • •   | • • |      |

| Chapter V   | THYRISTOR REVERS          |            | .C. SU  | PPLY    | • •     |       |       |     | 29   |

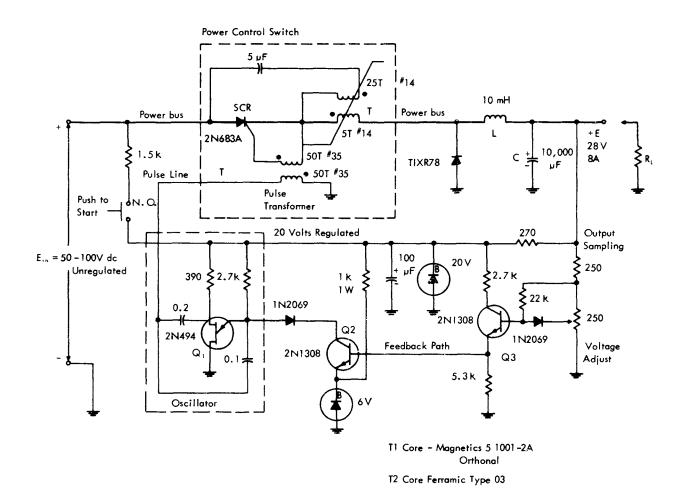

|             | Circuit Operation         | • • •      | • •     | • •     | • •     | • •   |       | • • | 29   |

|             | Cycloconverter            | • •        | • •     | • •     | • •     |       | • •   | • • | 31   |

| Chapter VI  | UNIJUNCTION TRAN          | ISISTO     | RS TH   | EORY,   | OPE     | RATIO | N ANI | D   |      |

| _           | CIRCUITS                  |            |         |         |         |       |       |     | 35   |

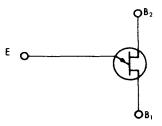

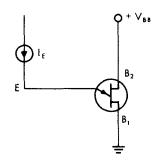

|             | Device Symbol and Cha     | racteristi | ics     |         |         |       |       |     | 35   |

|             | Equivalent Circuits       |            |         |         |         |       |       |     | 36   |

|             | Definition of Parameters  | s and Sy   | mbols   |         |         |       |       |     | 37   |

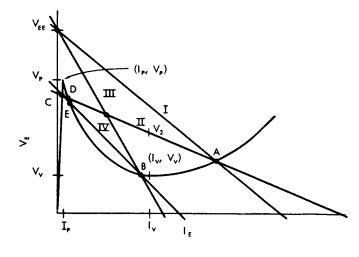

|             | Theory of Operation       |            |         |         |         |       |       |     | 37   |

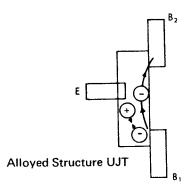

|             | Construction              |            |         |         |         |       |       |     | 38   |

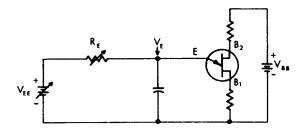

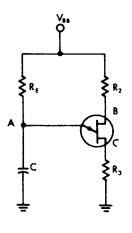

|             | Multivibrators            | • •        |         |         |         |       |       |     | 38   |

|             | Practical Circuits        |            |         |         |         |       |       |     | 43   |

| Appendix A  | Stabilising Vp against To | emperati   | ire Cha | anges   |         |       |       |     | 55   |

| Appendix B  | Unijunction Product Ra    |            |         |         |         |       |       |     | 57   |

| * F         | Triac Product Range       |            |         |         |         |       |       |     | 58   |

|             | Thyristor Product Rang    |            |         |         |         |       |       |     | 59   |

### **SECTION 2. POWER TRANSISTOR APPLICATIONS**

| Chapter VII  | SWITCHING MODE PO         | OWER     | SUPI   | PLIES   |        |       |        |        |     |

|--------------|---------------------------|----------|--------|---------|--------|-------|--------|--------|-----|

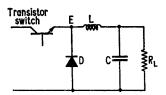

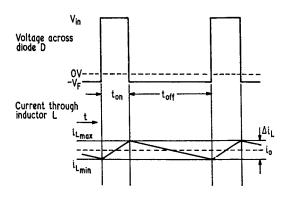

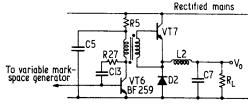

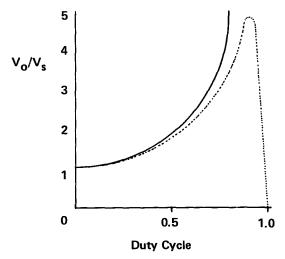

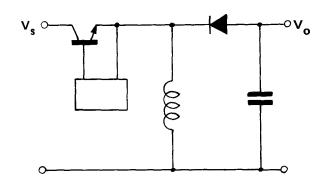

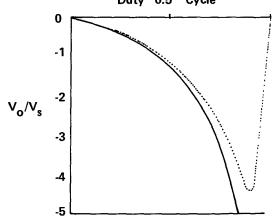

|              | Circuit Theory            |          |        |         |        |       |        |        |     |

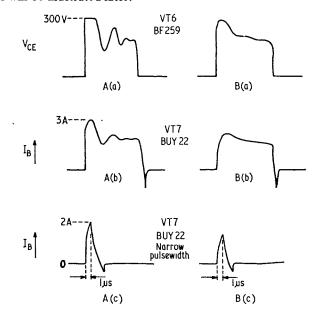

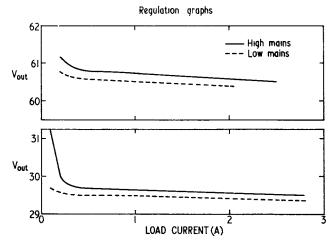

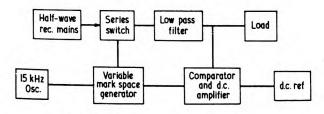

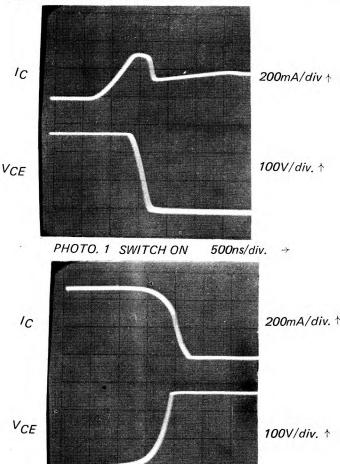

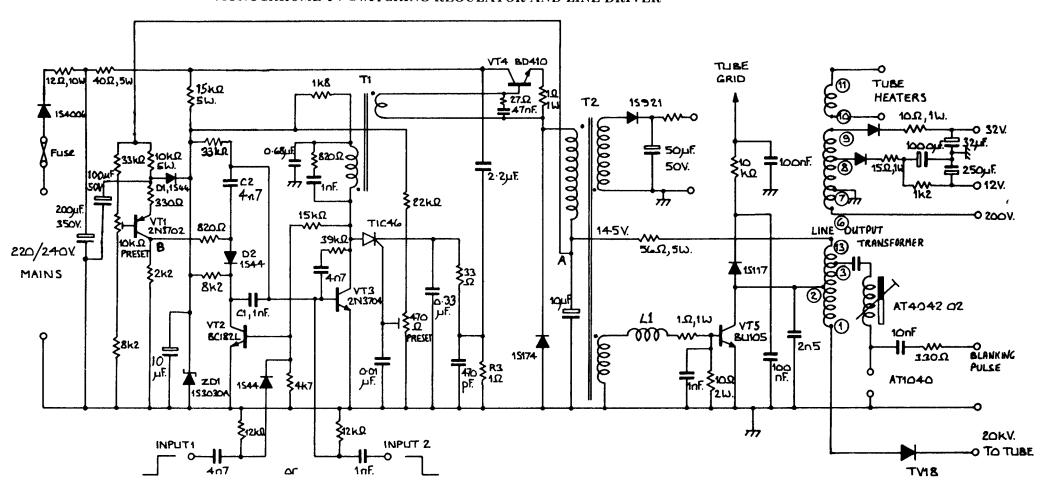

|              | The Circuit Performance   |          |        |         |        |       |        |        |     |

|              | Appendix                  |          |        |         |        |       |        |        |     |

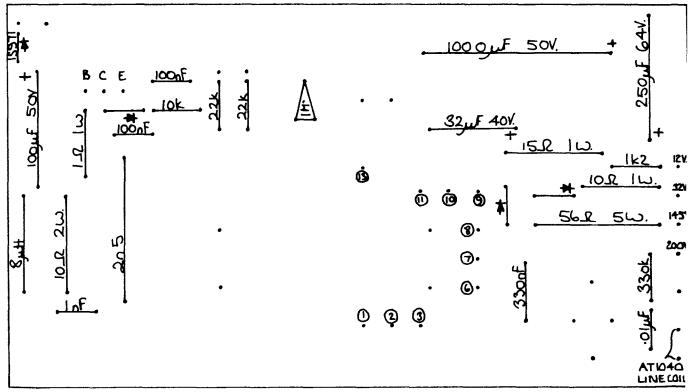

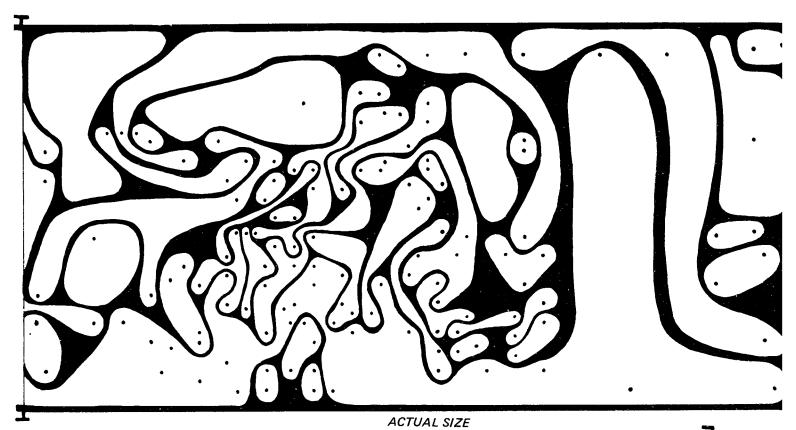

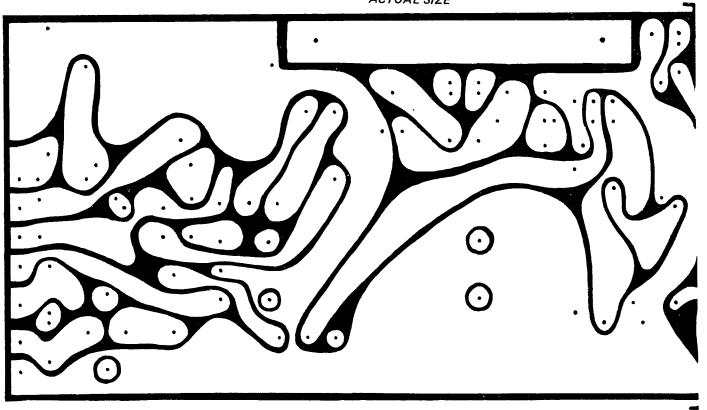

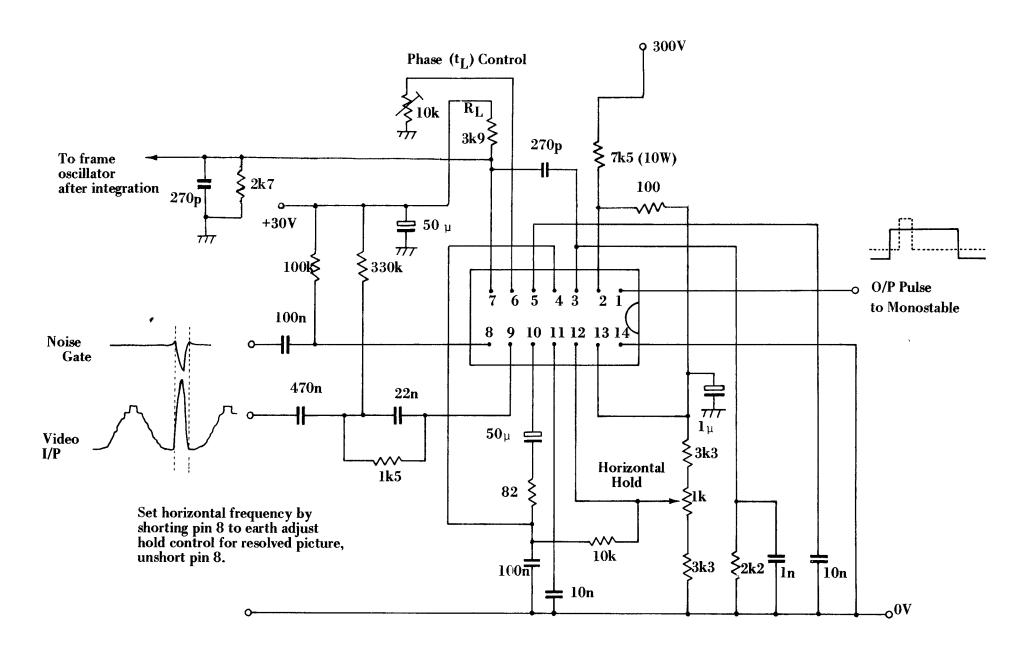

| Chapter VIII | MONOCHROME TV S           | WITCH    | IING   | REGU    | LATO   | R ANI | ) LINI | E DRIV | /ER |

|              | Circuit Description       |          |        |         |        |       |        |        |     |

|              | Results                   |          |        |         |        |       |        |        |     |

|              | Construction              |          |        |         |        |       |        |        |     |

| Chapter IX   | CHOPPER POWER SU          | PPLIE:   | s USI  | NG BU   | Y69/70 | HIGH  | l VOL  | TAGE   |     |

| •            | POWER TRANSISTOR          | S        |        |         |        |       |        |        |     |

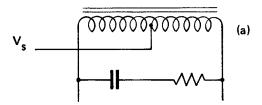

|              | General Principles        |          |        |         |        |       |        |        |     |

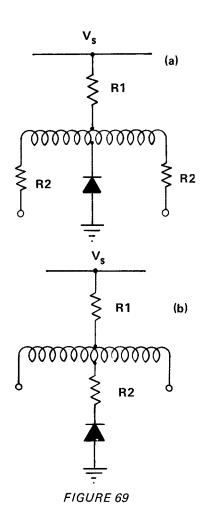

|              | Single Device Shunt Cho   | pper Po  | wer S  | Supply  |        |       |        |        |     |

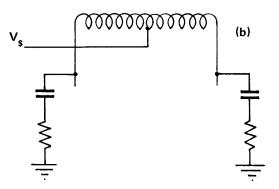

|              | Modified Circuit to Incre | ase Ou   | tput P | ower    |        |       |        |        |     |

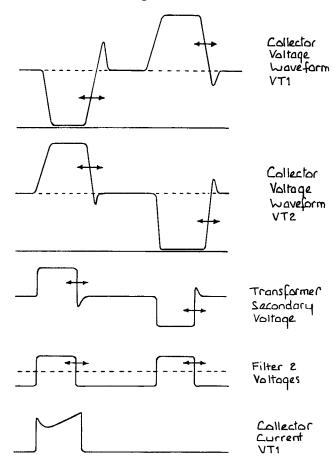

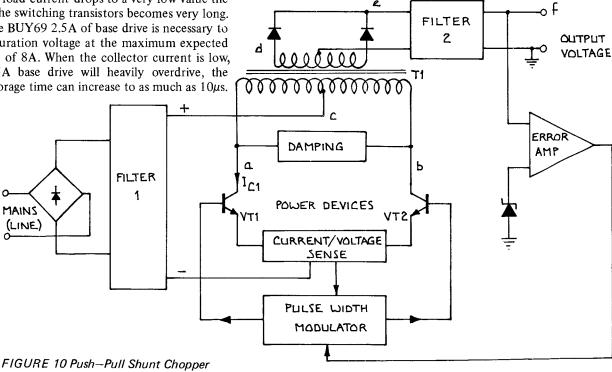

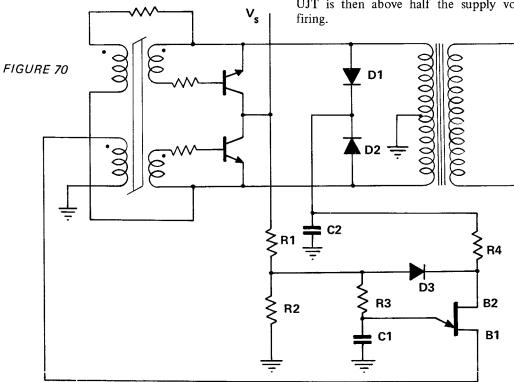

|              | Push-Pull Shunt Choppe    | r Power  | Supp   | olies   |        |       |        |        |     |

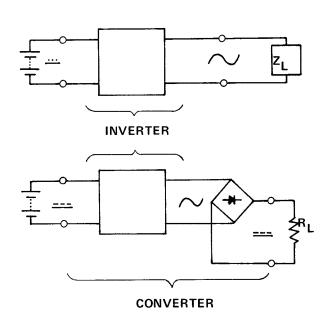

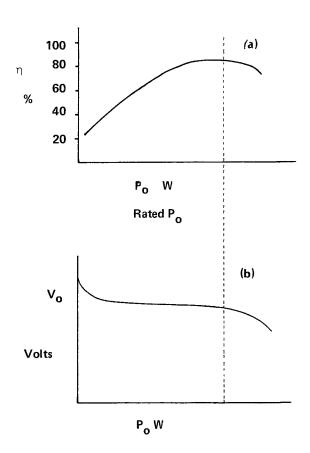

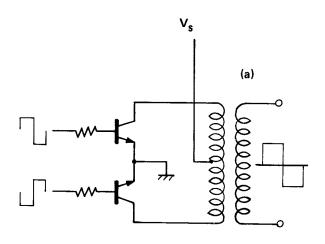

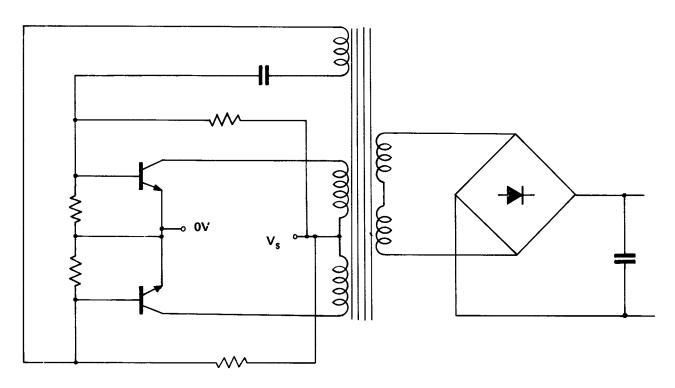

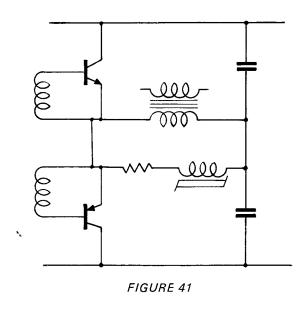

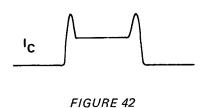

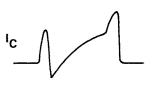

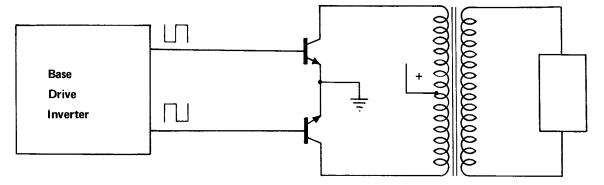

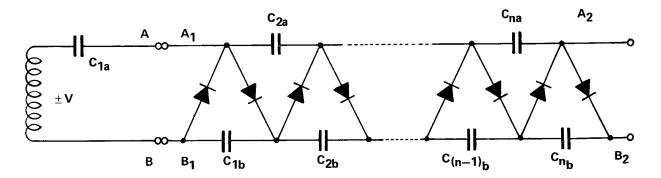

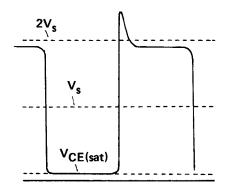

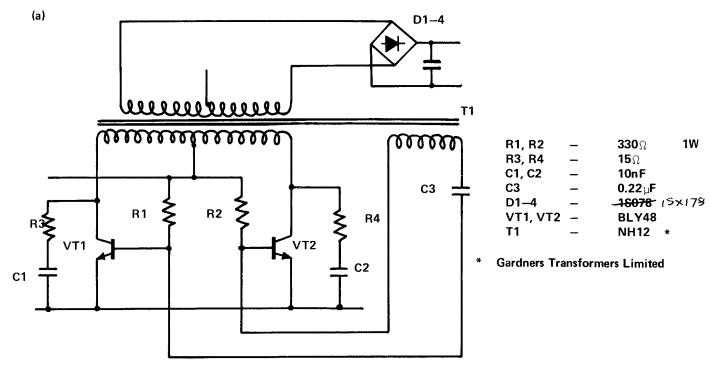

| Chapter X    | INVERTERS                 |          |        |         |        |       |        |        |     |

|              | Introduction              |          |        |         |        |       |        |        |     |

| /            | Power Sources             |          |        |         |        |       |        |        |     |

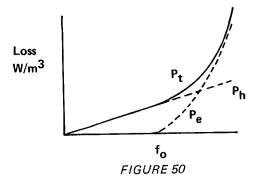

|              | Magnetic Properties       |          |        |         |        |       |        |        |     |

|              | Device Selection          |          |        |         |        |       |        |        |     |

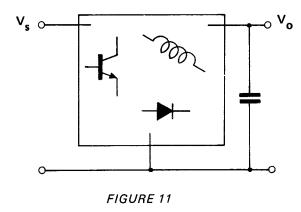

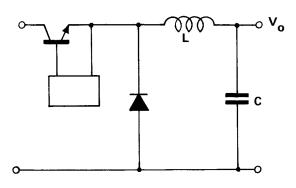

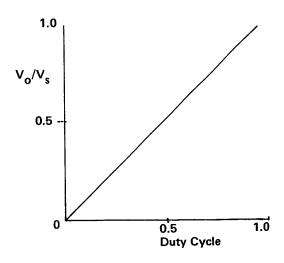

| 1            | Switching Regulators      |          |        | • • • • |        |       |        |        |     |

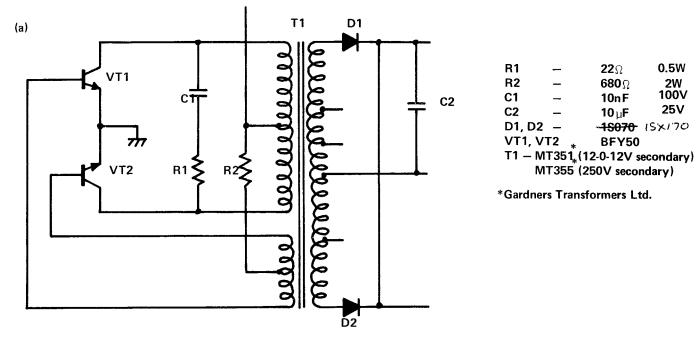

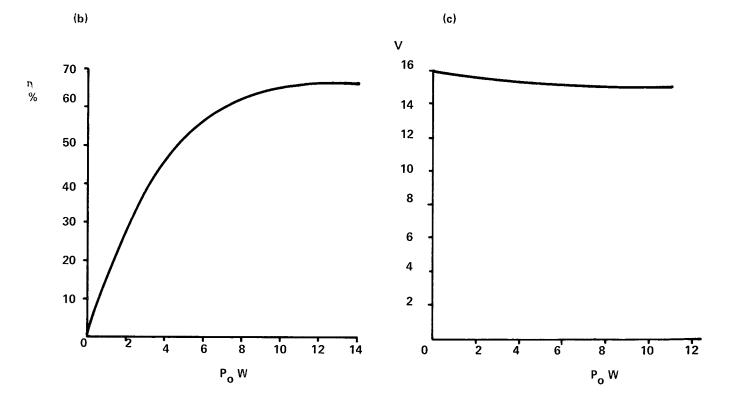

| 883 🗸        | Single Saturating Transf  | ormer (  | Conve  | rter    |        |       |        |        |     |

|              | Two Transformer (Satur    | ating) I | nverte | ers     |        |       |        |        |     |

| /            | CR Timed Inverters        |          |        |         |        |       |        |        |     |

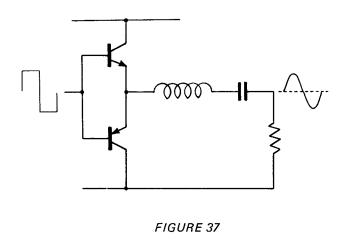

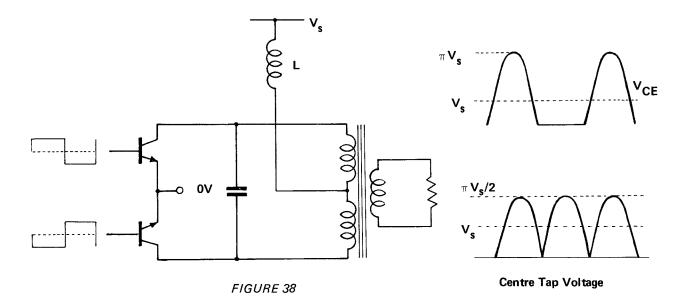

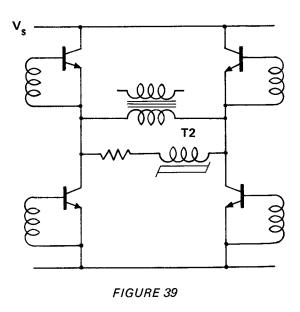

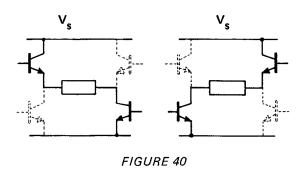

| /            | Sinewave, Bridge and Dr   | riven In | verter | ·s      |        |       |        |        |     |

|              | Transformer Design        |          |        |         |        |       |        |        |     |

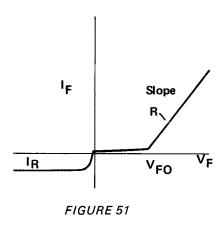

| i            | Power Diodes              |          |        |         |        |       |        |        |     |

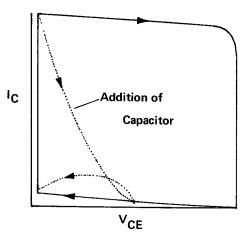

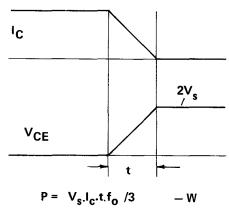

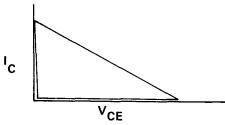

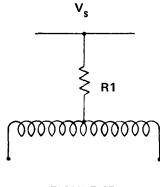

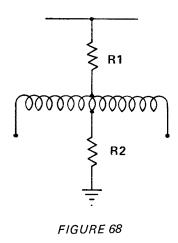

| ļ            | Spikes and Switching Lo   | sses     |        |         |        |       |        |        |     |

| 1            | Starting Circuits         |          |        |         |        |       |        |        |     |

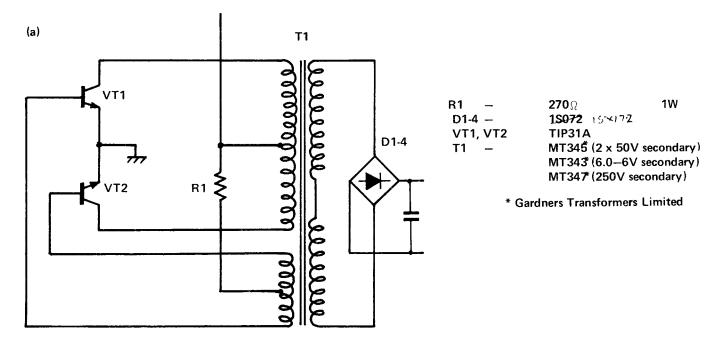

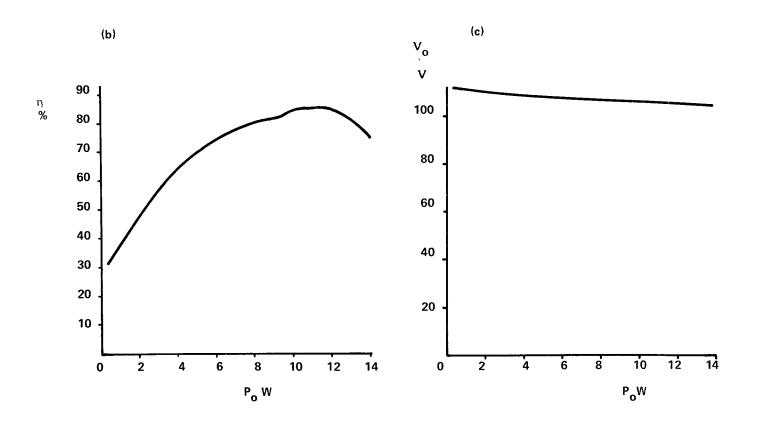

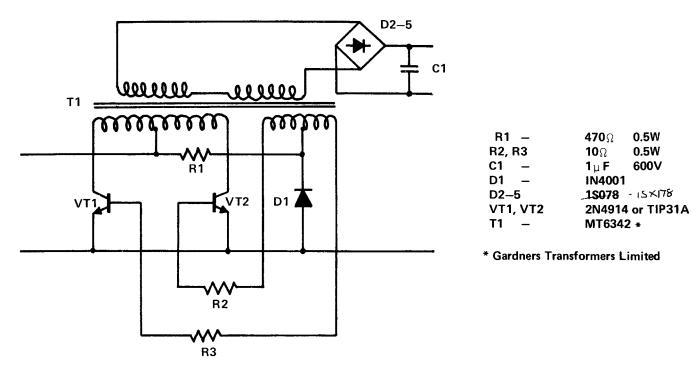

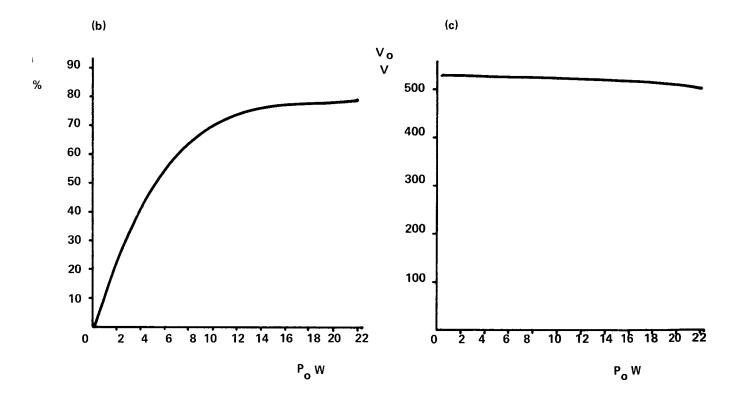

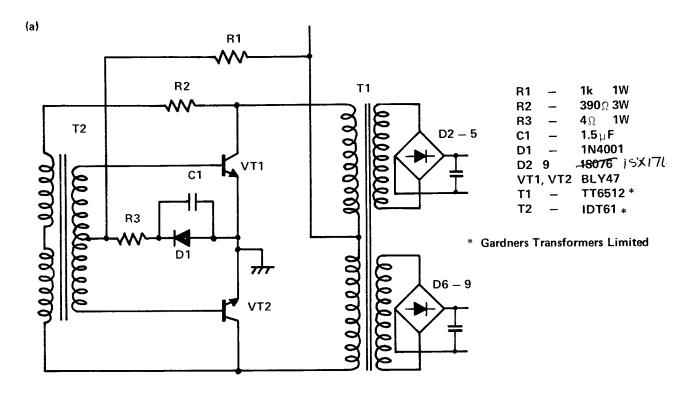

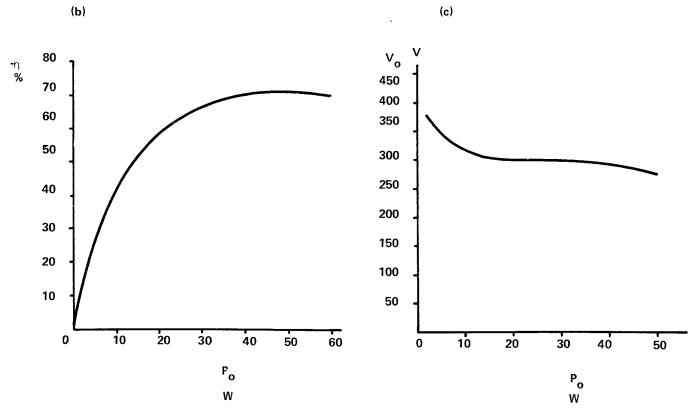

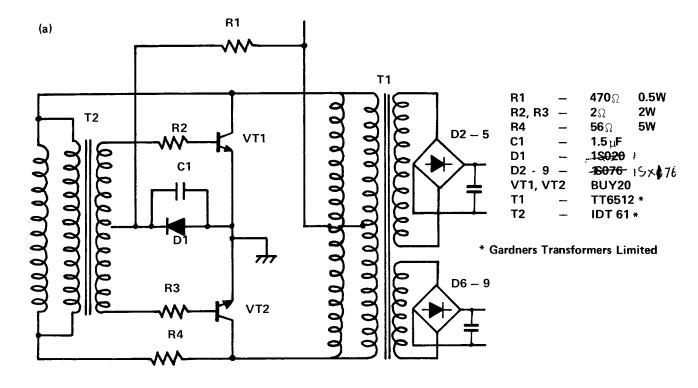

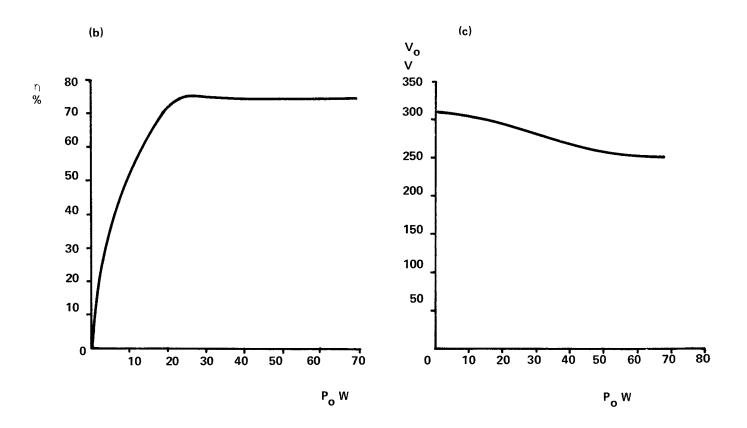

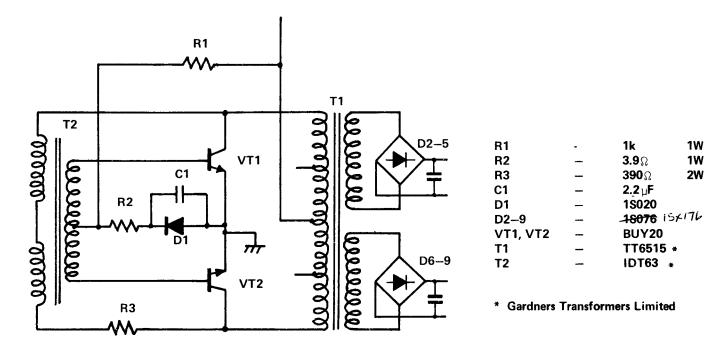

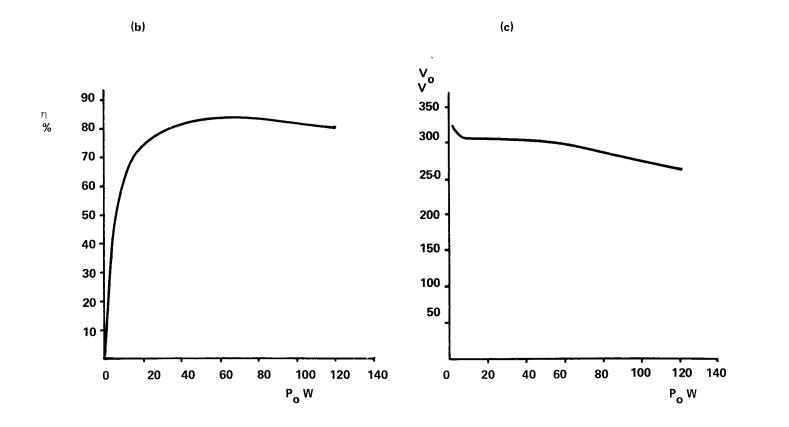

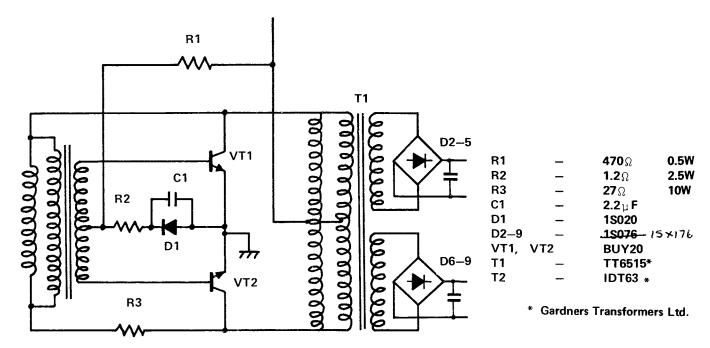

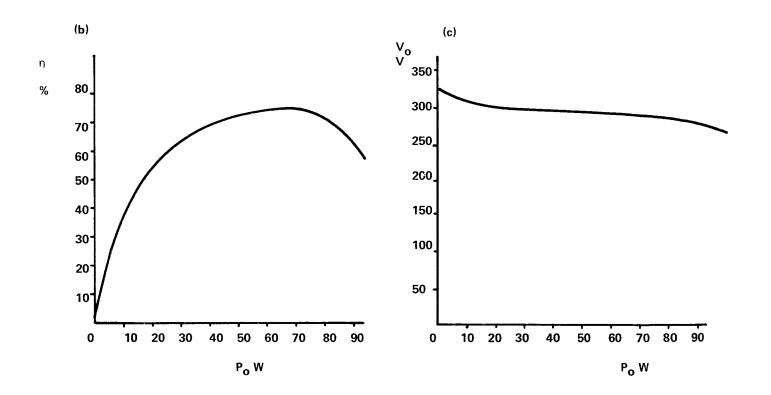

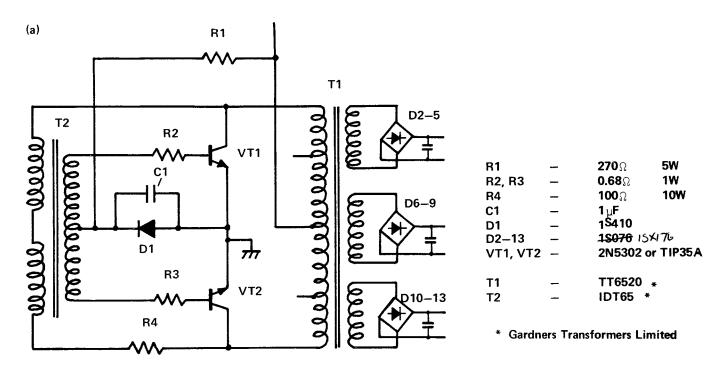

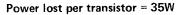

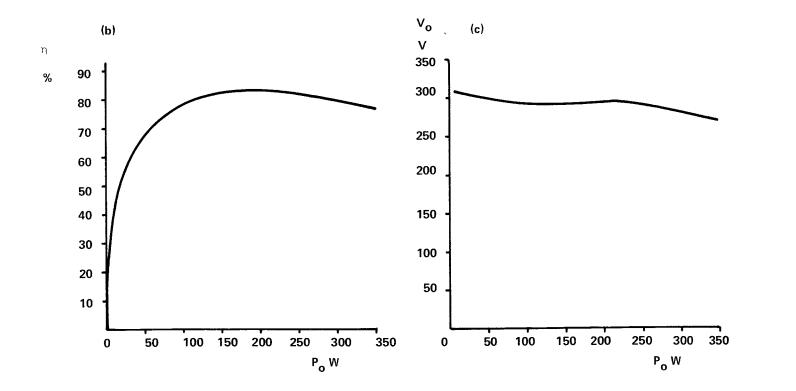

|              | Practical Circuits and Pe |          |        |         |        |       |        |        |     |

#### **SECTION 3. AUDIO CIRCUITS**

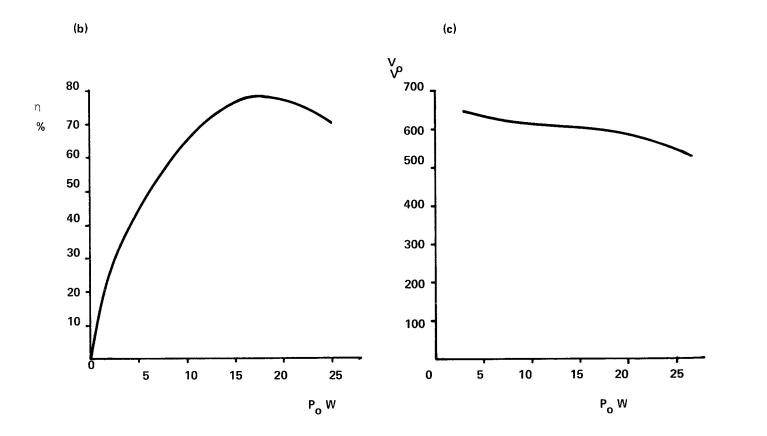

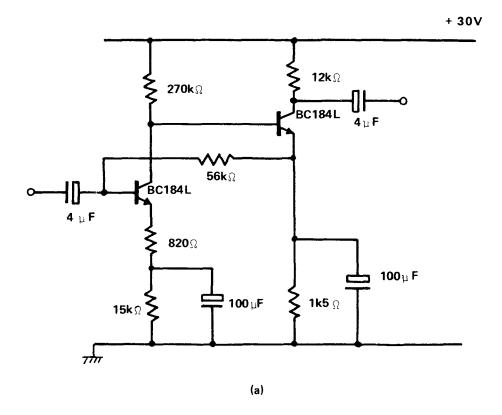

| Chapter XI   | A HIGH FIDELI        | TY PR    | EAMP   | LIFIE   | R    |      |       |     | <br> | 129 |

|--------------|----------------------|----------|--------|---------|------|------|-------|-----|------|-----|

|              | Specification        |          |        |         |      |      |       |     | <br> | 129 |

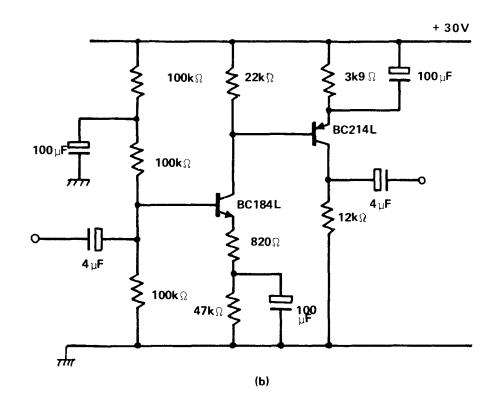

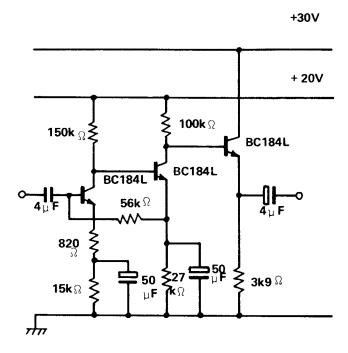

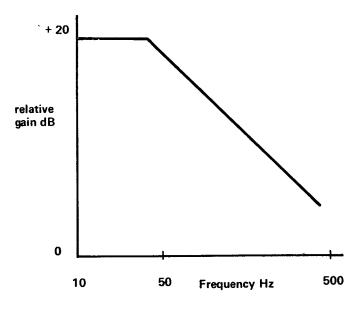

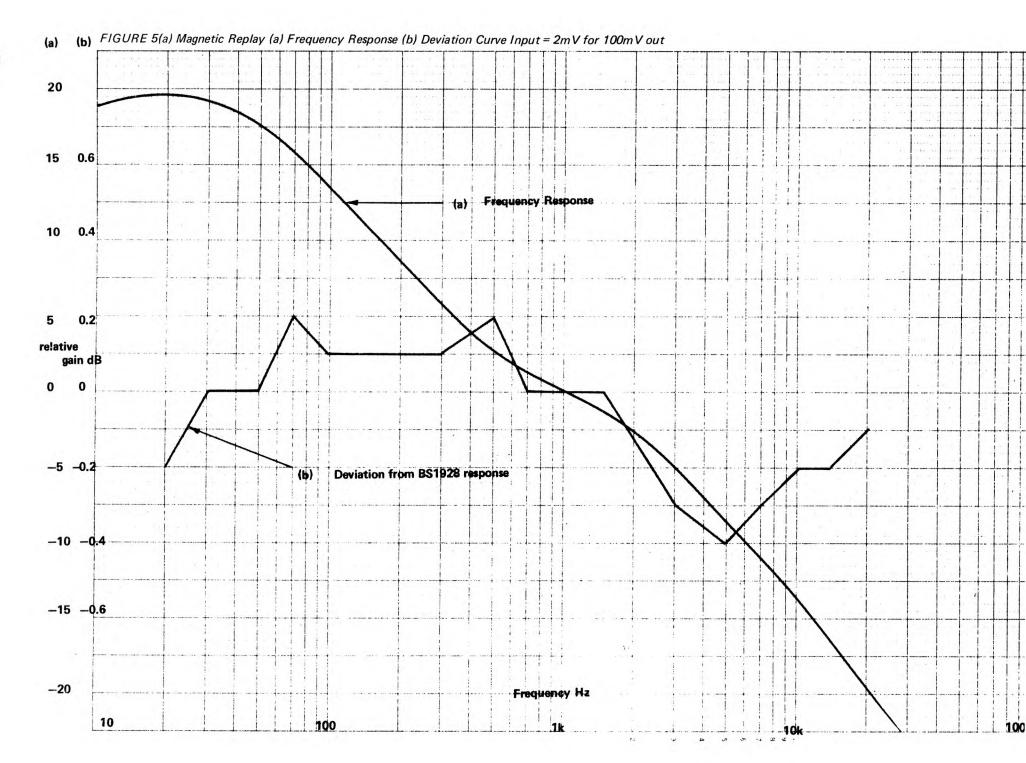

|              | The Circuit          |          |        |         |      |      |       |     | <br> | 129 |

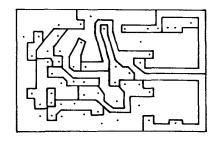

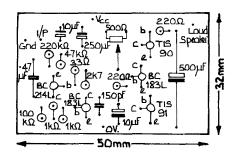

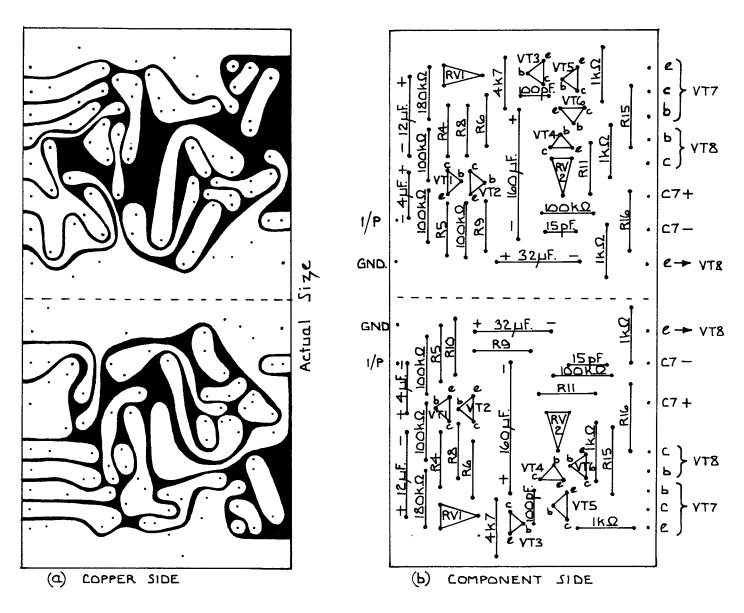

|              | Construction         |          |        |         |      |      |       |     | <br> | 150 |

|              | Checking Out         |          |        |         |      |      |       |     | <br> | 158 |

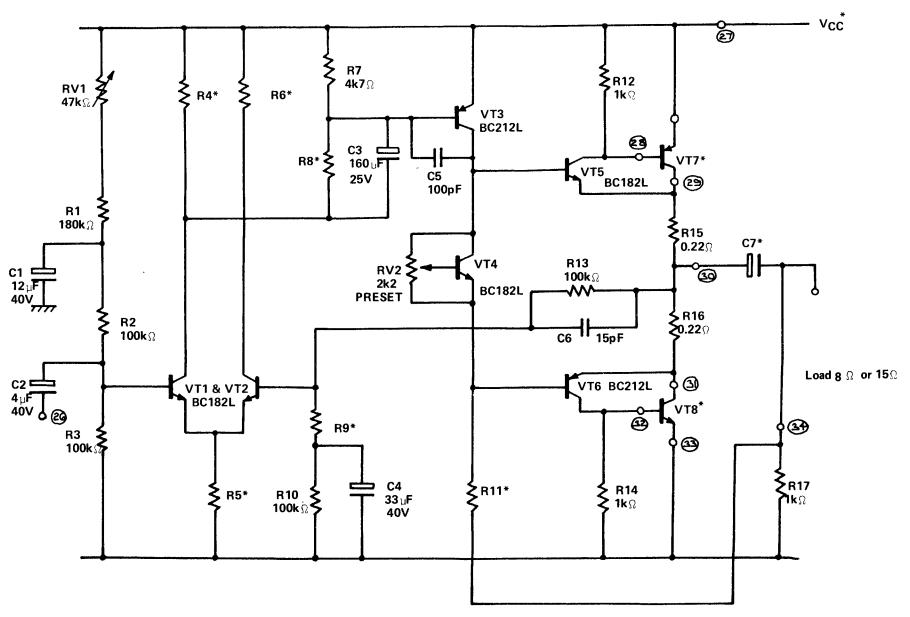

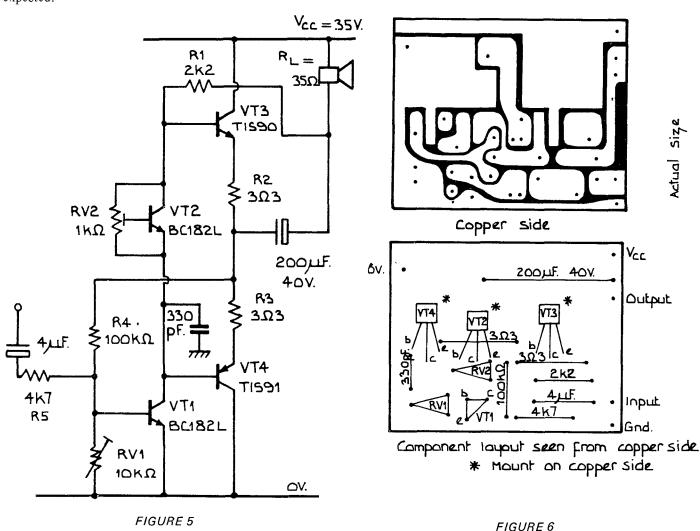

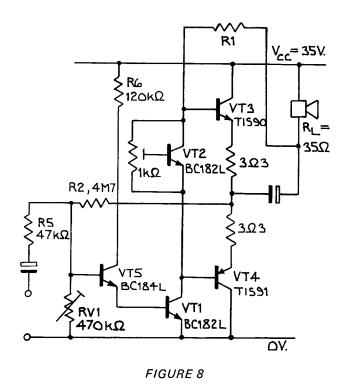

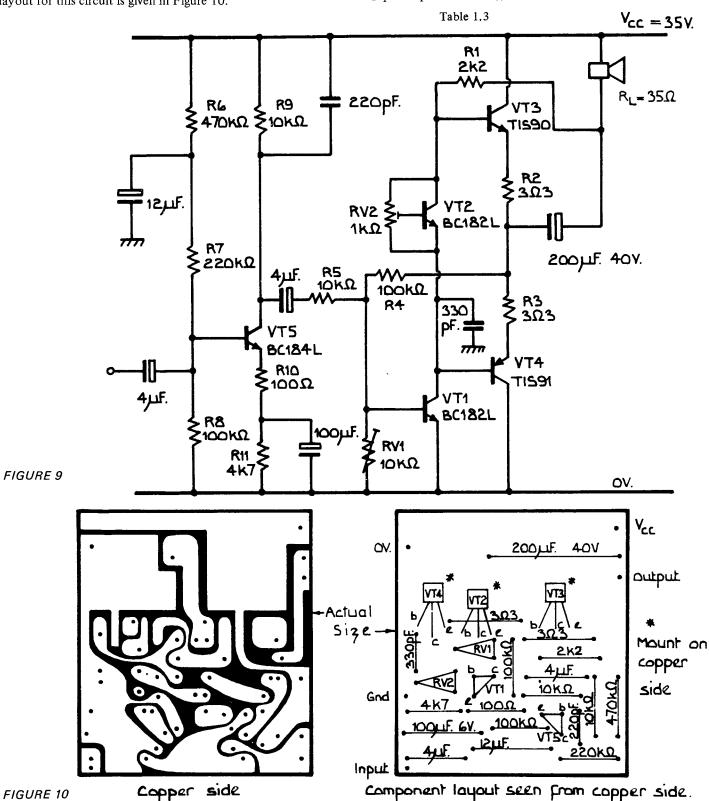

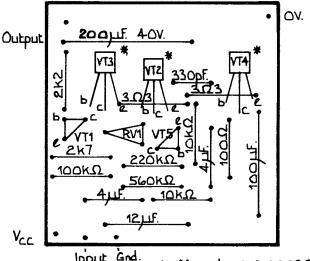

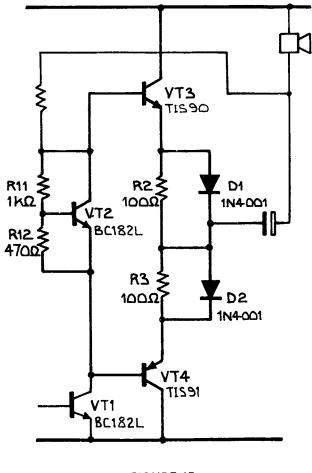

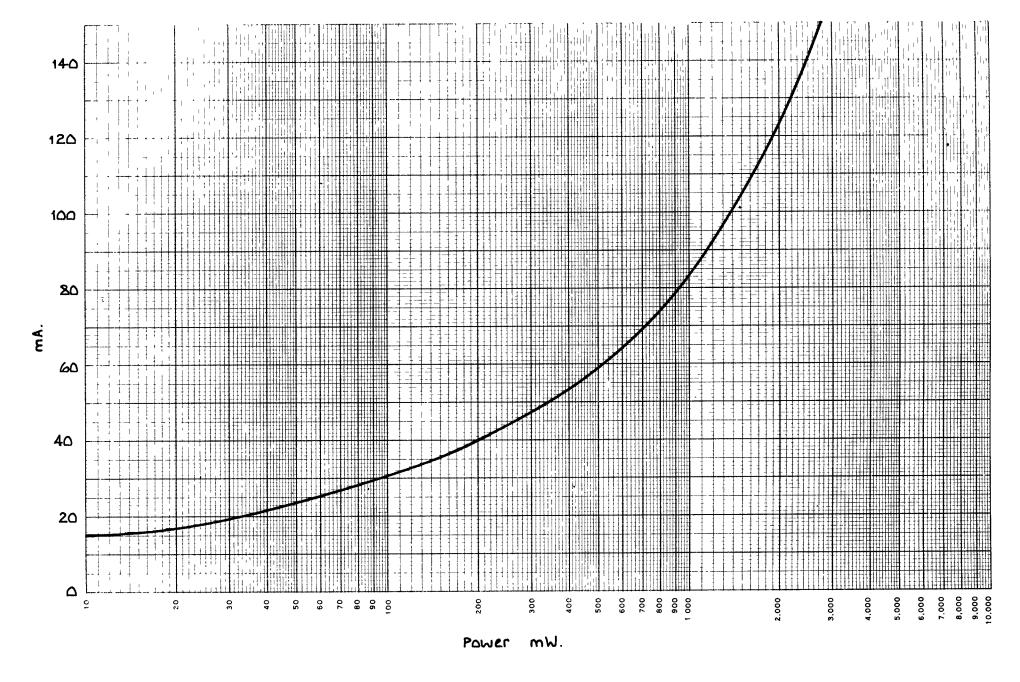

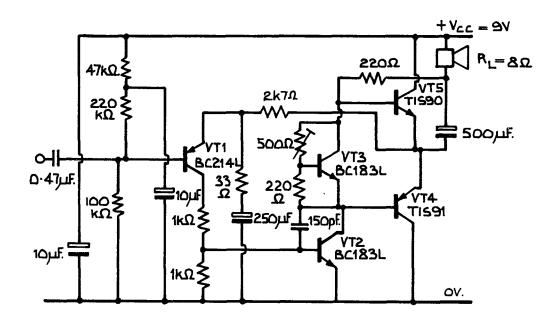

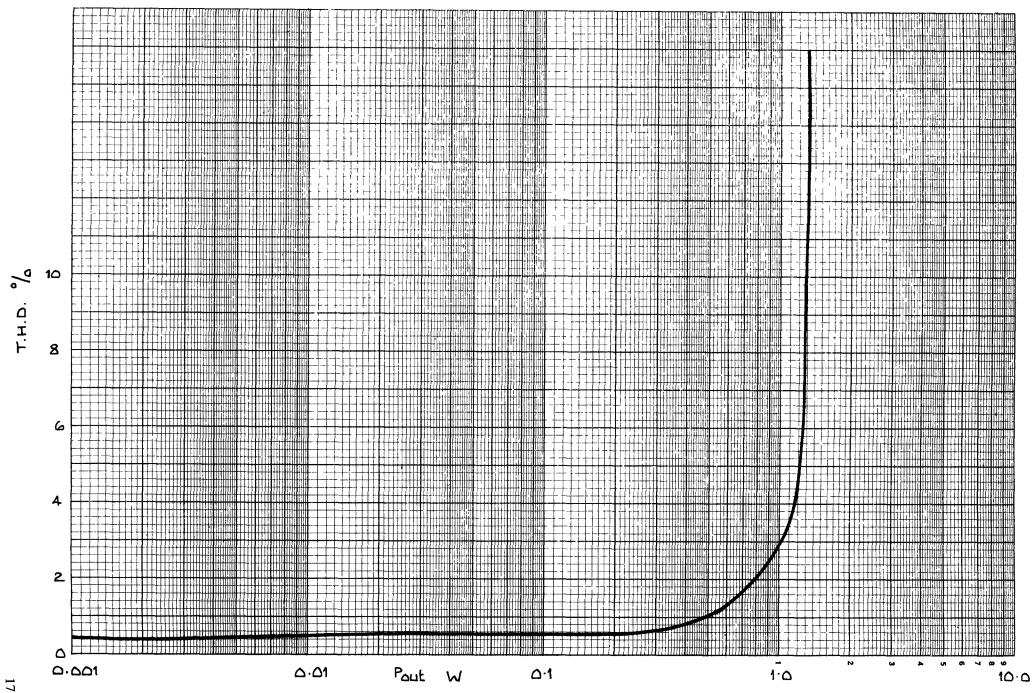

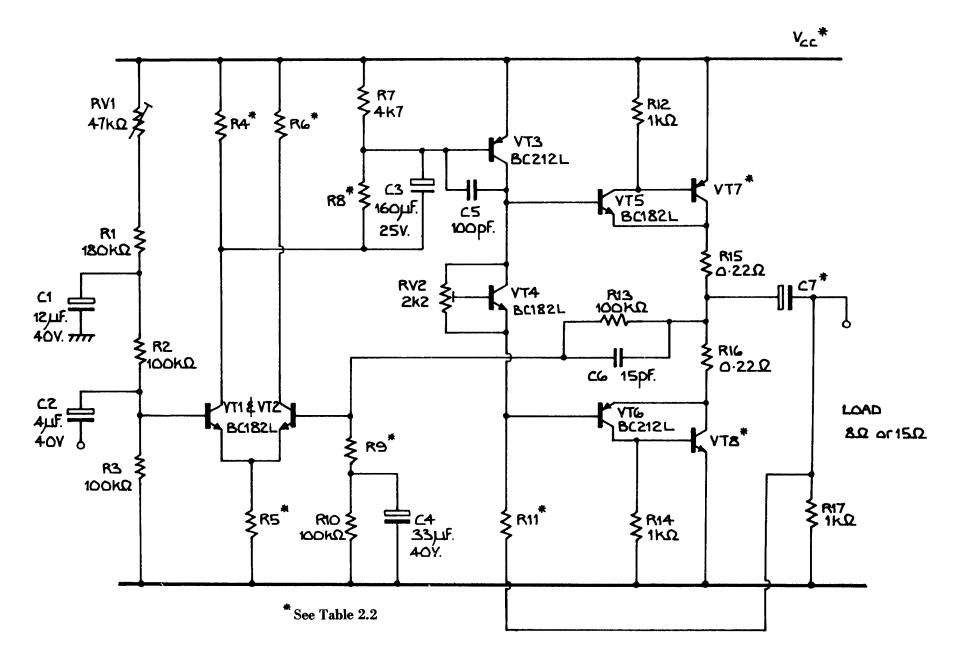

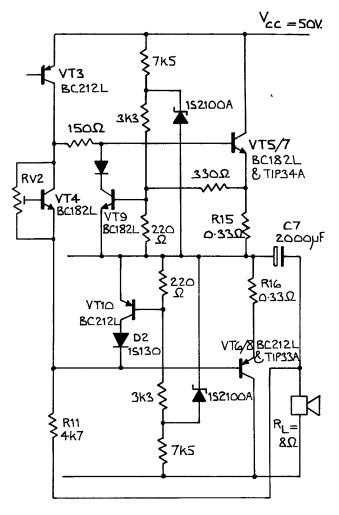

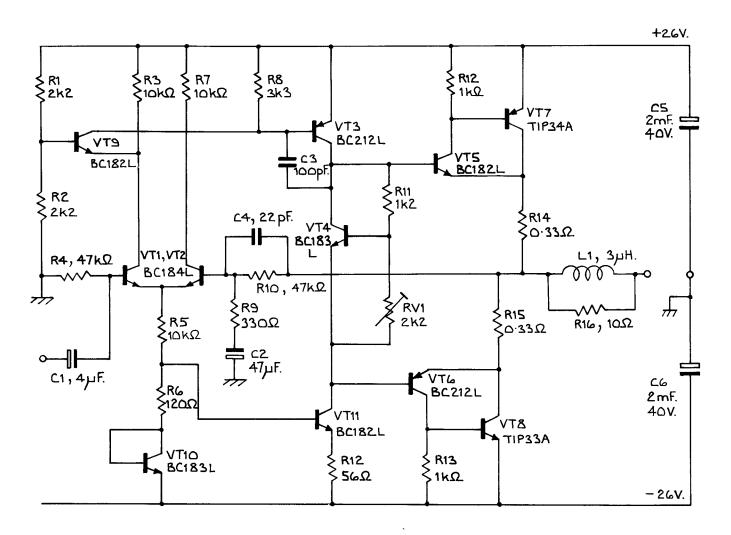

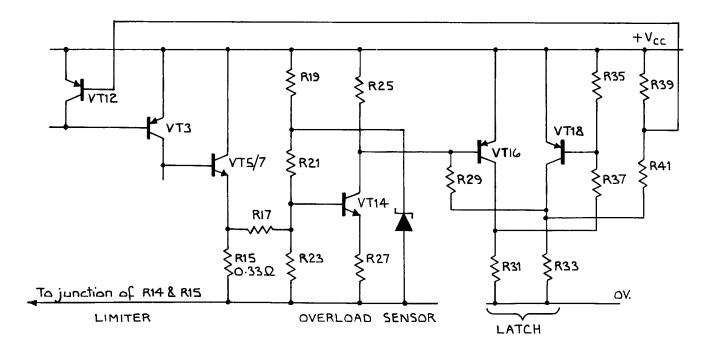

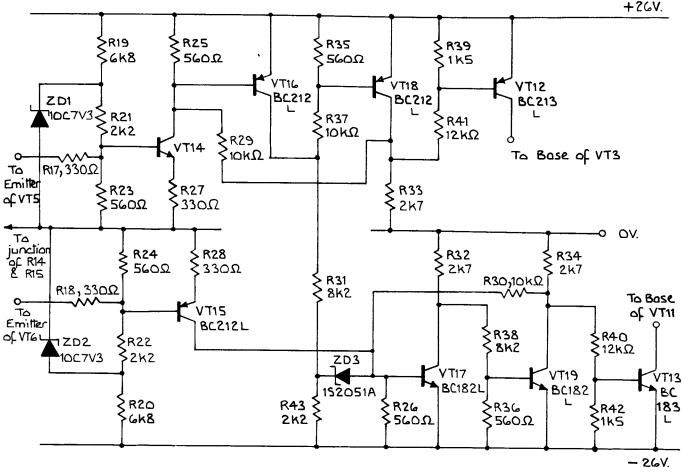

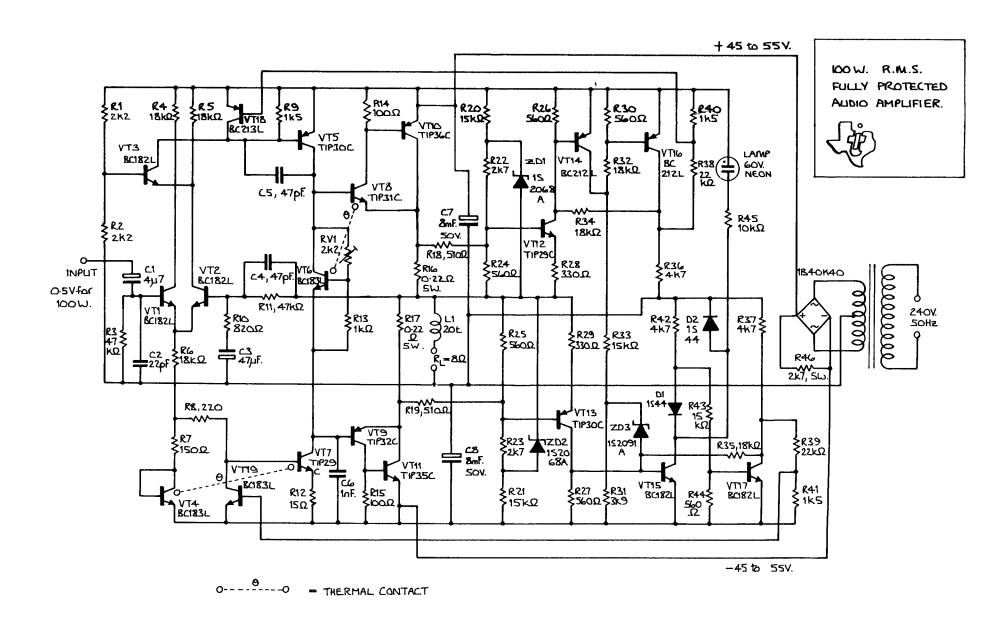

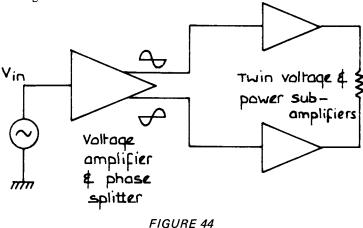

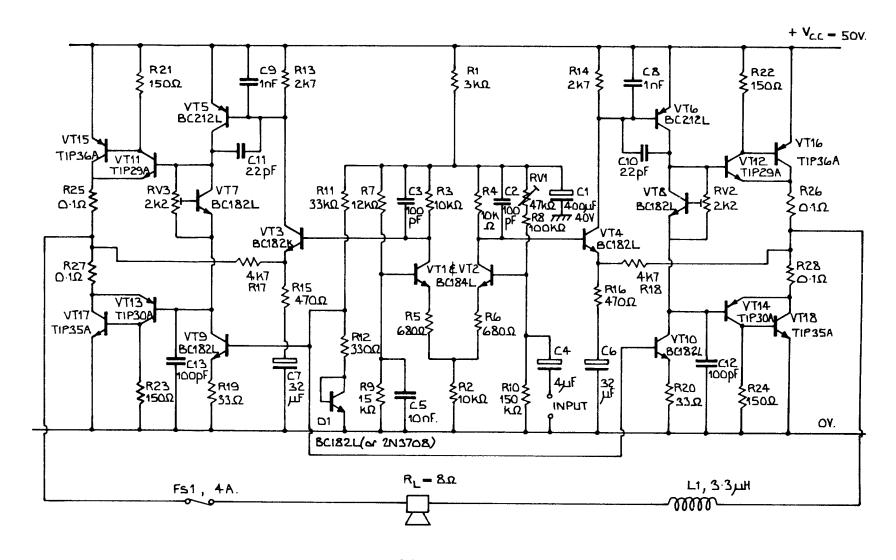

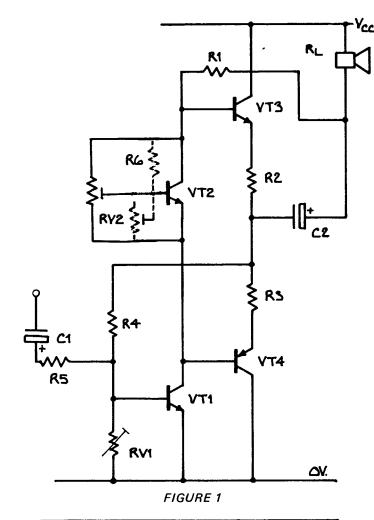

| Chapter XII  | POWER AMPLIE         | FIERS    |        |         |      |      |       |     | <br> | 161 |

| •            | Part 1. 1, 2 and 2.5 |          |        |         |      |      |       |     | <br> | 161 |

|              | Part 2. Amplifiers   |          | •      |         |      |      |       |     | <br> | 174 |

|              | Part 3. Amplifiers   | for 100  | )W and | above   |      |      |       |     | <br> | 196 |

|              | Part 4. Measureme    | ent Me   | thods  |         |      |      |       |     | <br> | 203 |

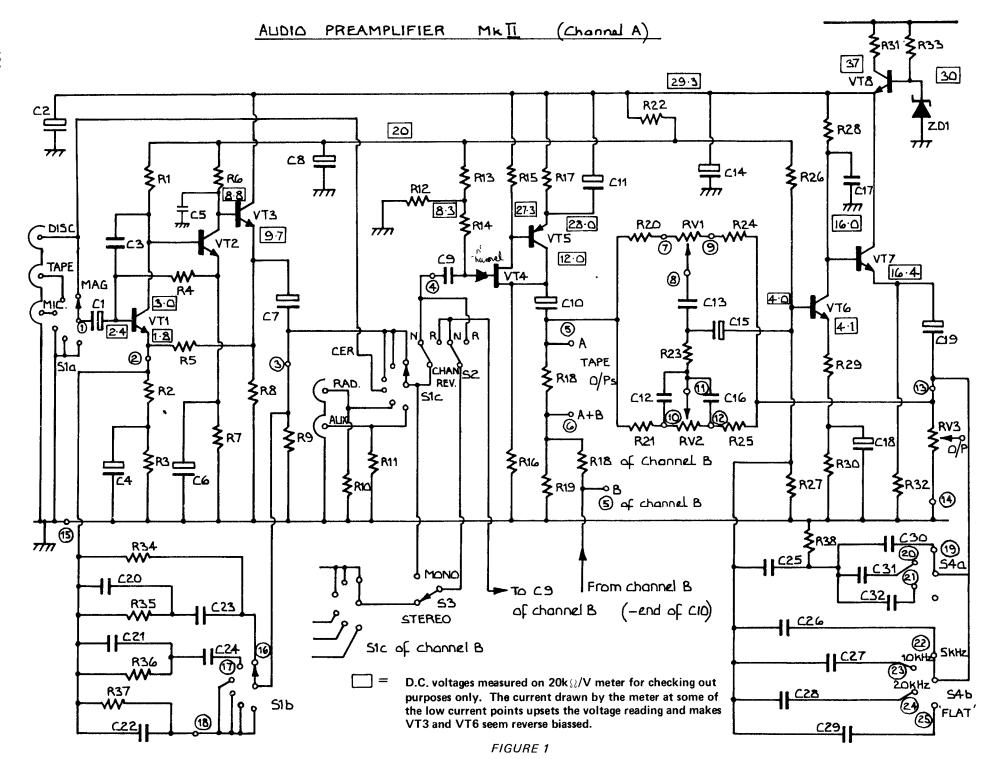

| Chapter XIII | SUPER SILECT         | ΓRAN     | SISTOI | RS IN A | AUDI | O AM | PLIFI | ERS | <br> | 206 |

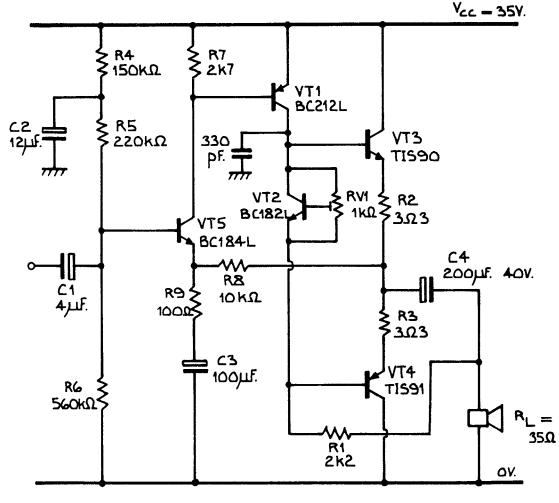

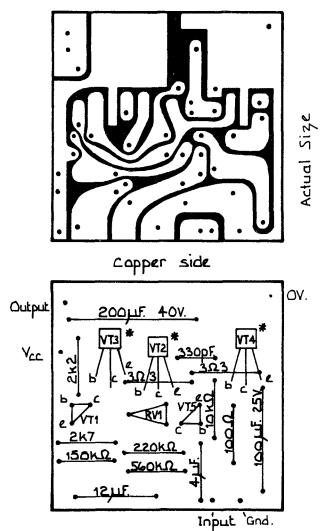

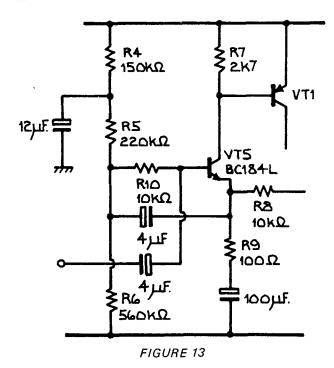

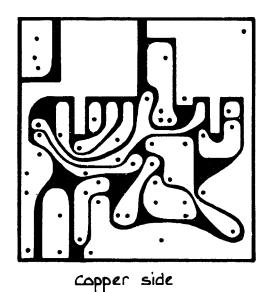

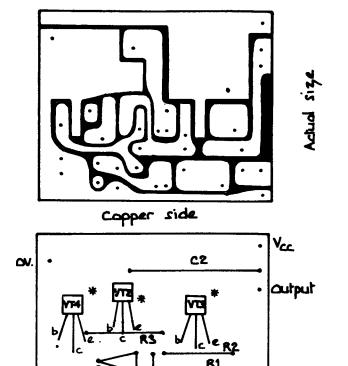

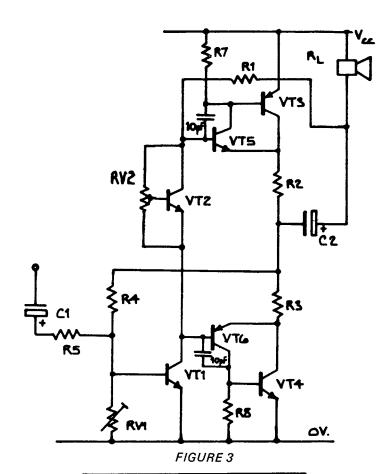

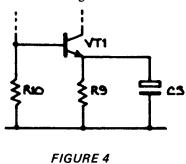

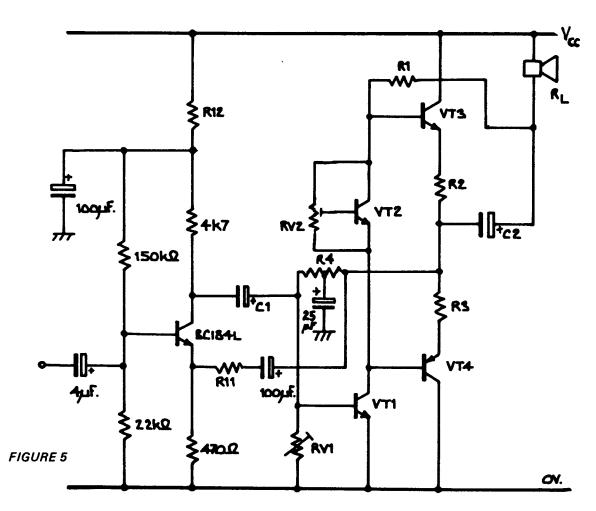

| •            | 5W Amplifiers        |          |        |         |      |      |       |     | <br> | 206 |

|              | Higher Output An     | nplifier | s      |         |      |      |       |     | <br> | 211 |

#### **SECTION 4. USING TTL INTEGRATED CIRCUITS**

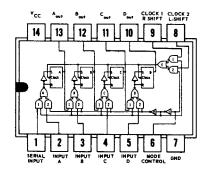

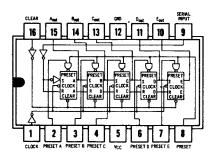

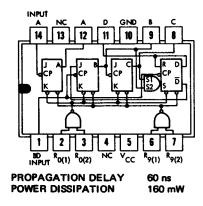

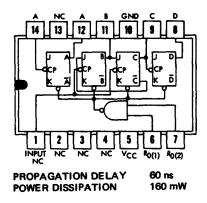

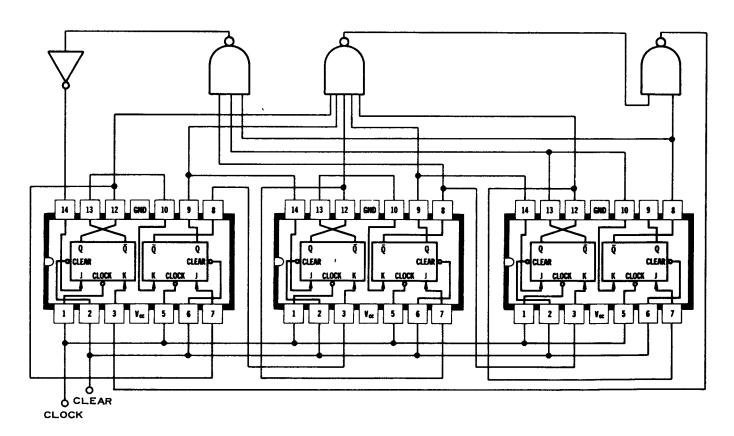

| Chapter XIV  | TTL COUNTERS AND RE               | GISTERS     |          |        |        |       |     | <br>215 |

|--------------|-----------------------------------|-------------|----------|--------|--------|-------|-----|---------|

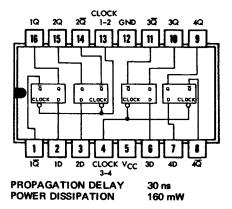

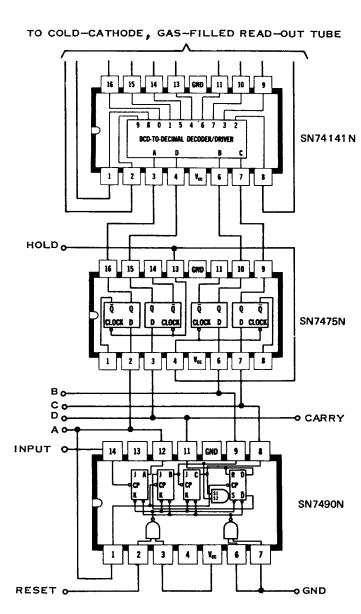

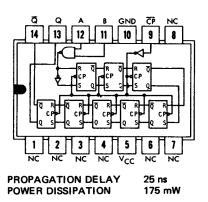

| ĺ            | Registers and Counters Desc       | riptions    |          |        |        |       |     | <br>215 |

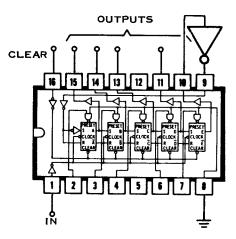

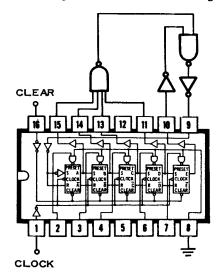

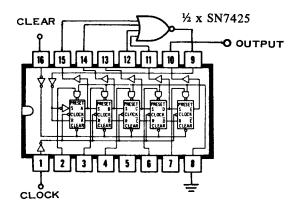

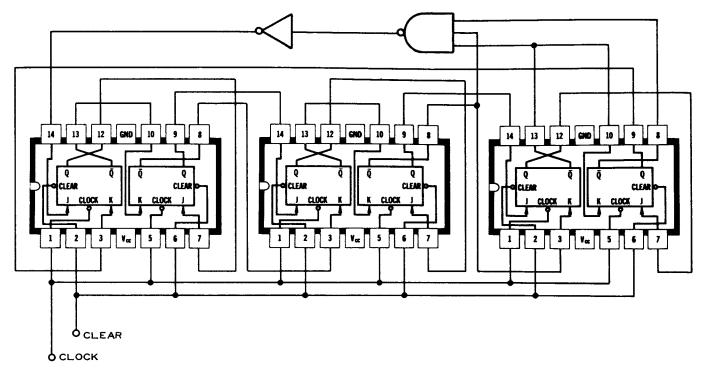

| ]            | Register Examples                 |             |          |        |        |       |     | <br>220 |

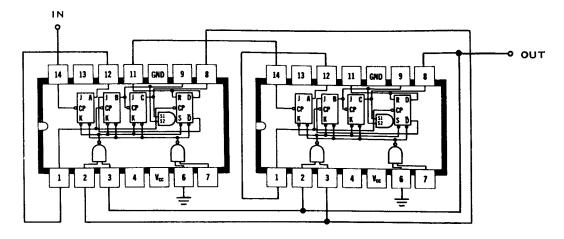

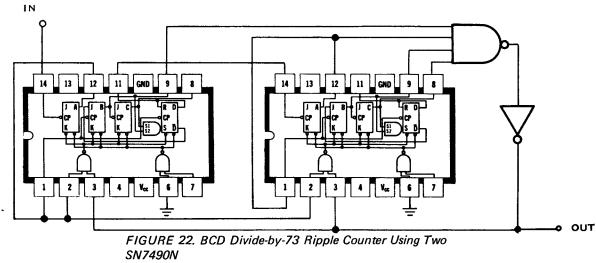

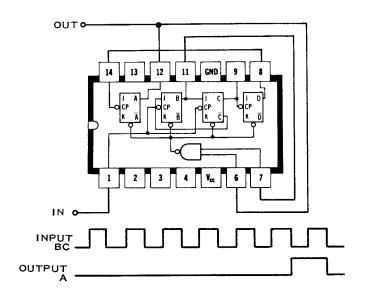

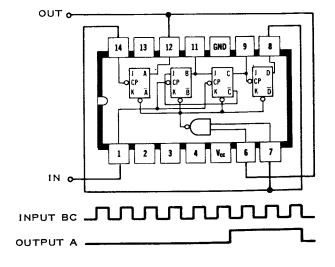

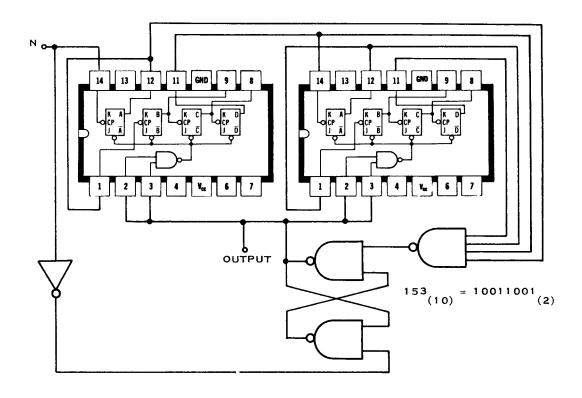

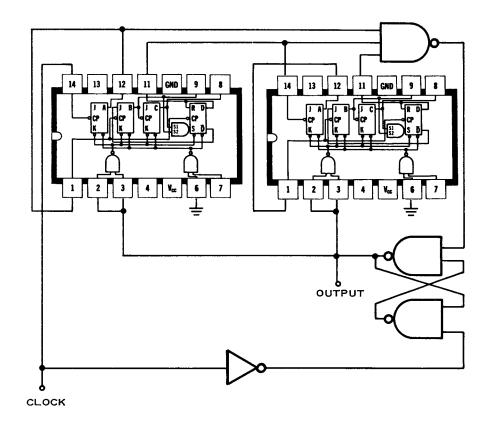

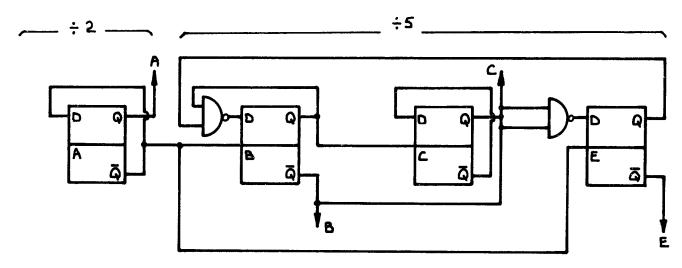

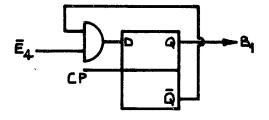

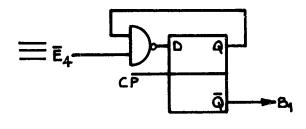

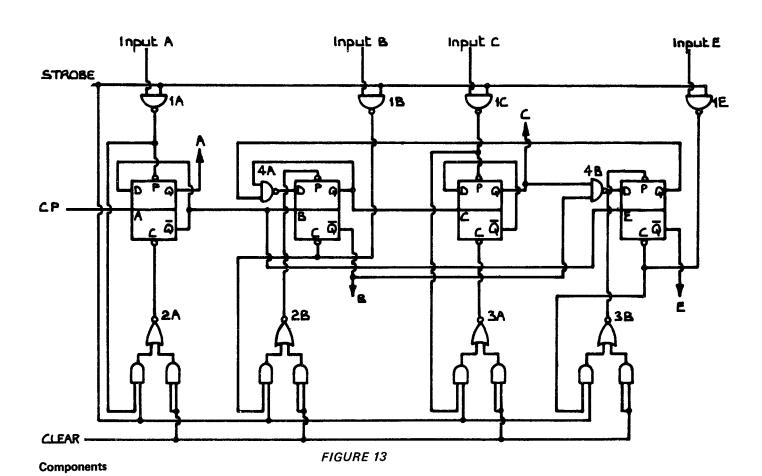

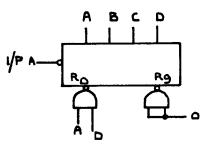

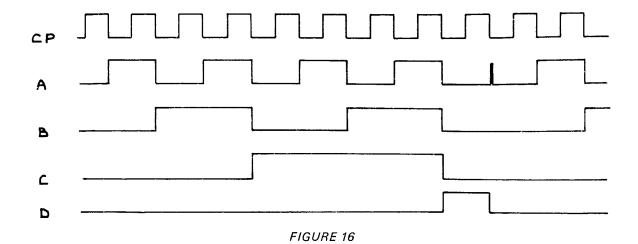

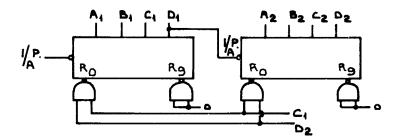

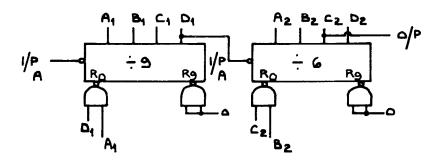

| 21.2         | Divide-by-N Ripple Counter        | s (N = Cyc) | le Leng  | th)    |        |       |     | <br>222 |

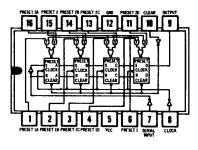

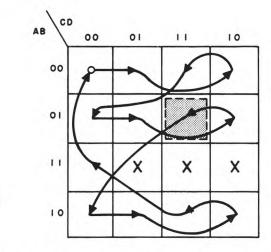

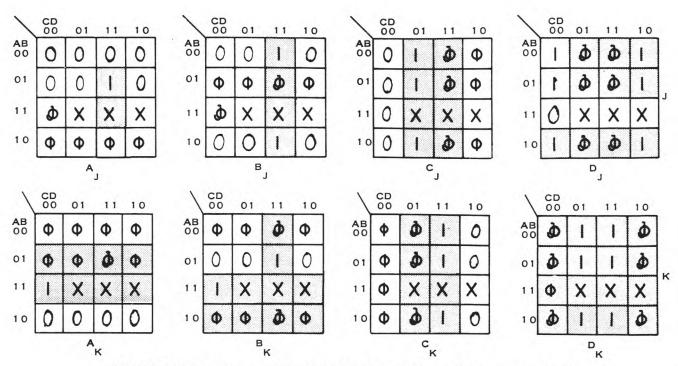

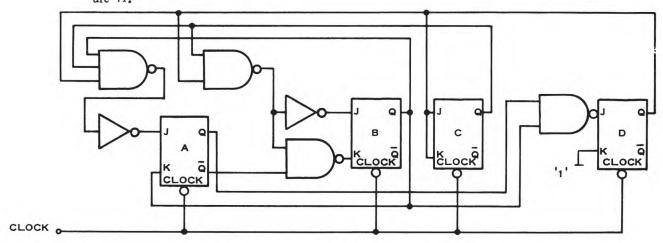

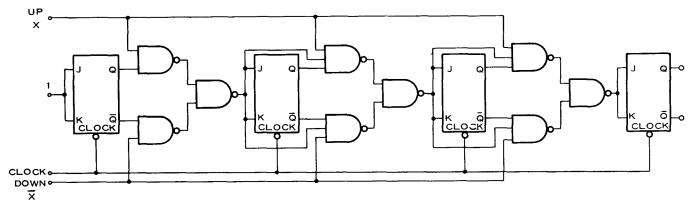

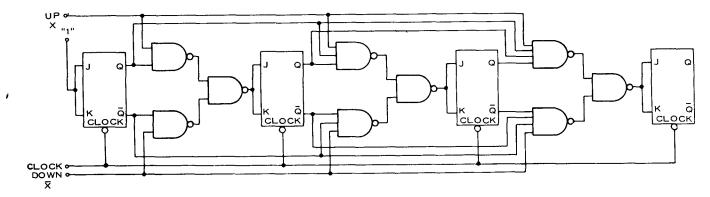

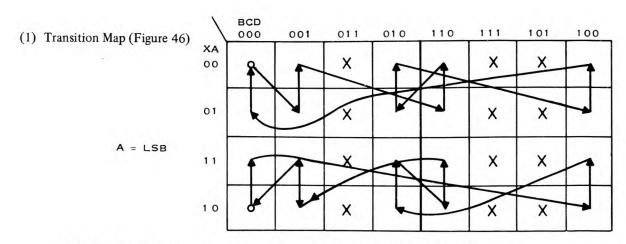

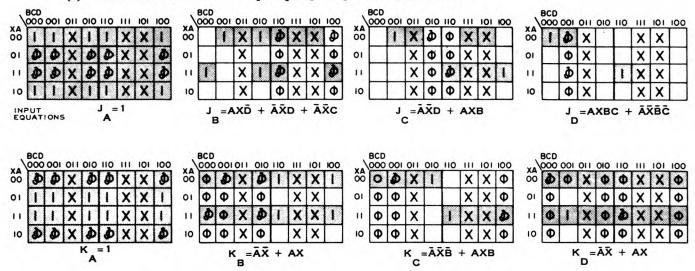

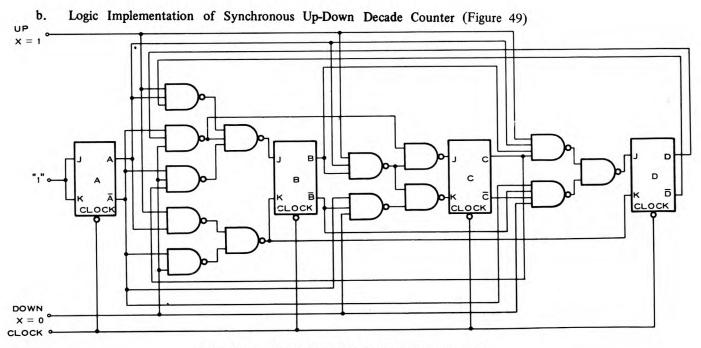

| B102 7       | Synchronous Counters              |             |          |        |        |       |     | <br>228 |

| 1            | Johnson Counters and Ring         | Counters    |          |        |        |       |     | <br>232 |

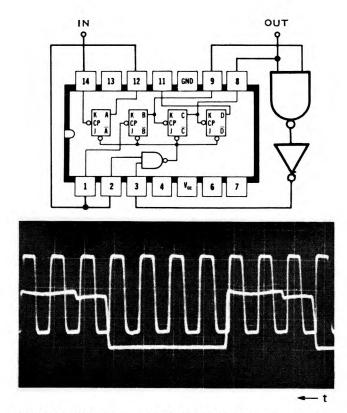

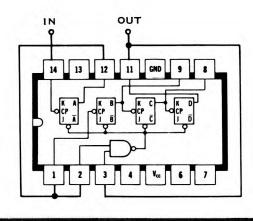

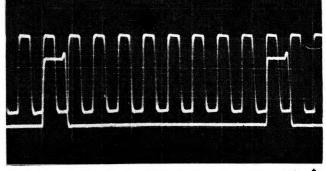

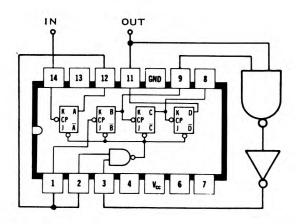

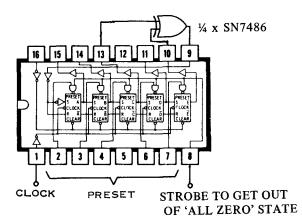

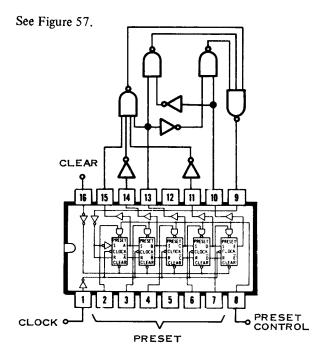

| C            | Shift Register Generator Con      | unters      |          |        |        |       |     | <br>234 |

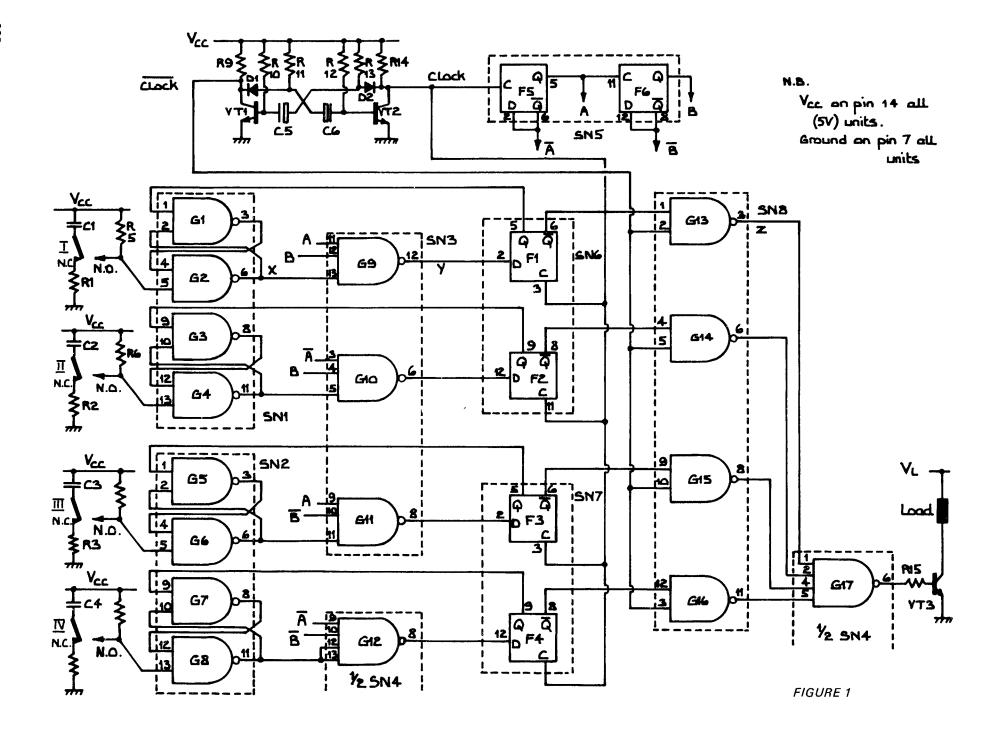

| Chapter XV   | NUMEROUS TTL APPLIC               | CATIONS     |          |        |        |       |     | <br>237 |

| BIO          | Parallel Summing Counter          |             |          |        |        |       |     | <br>237 |

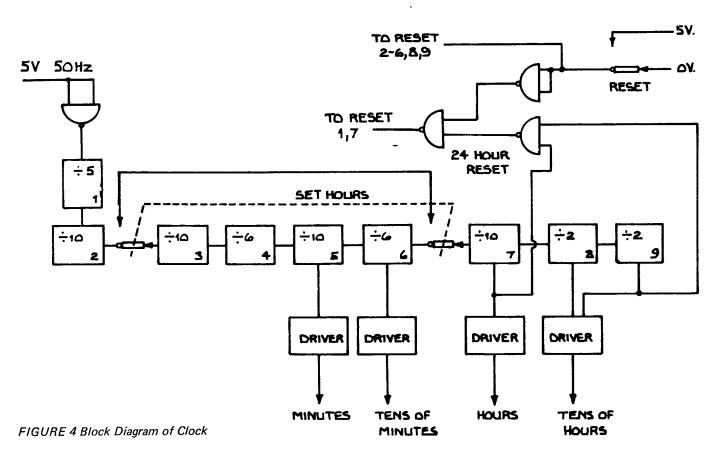

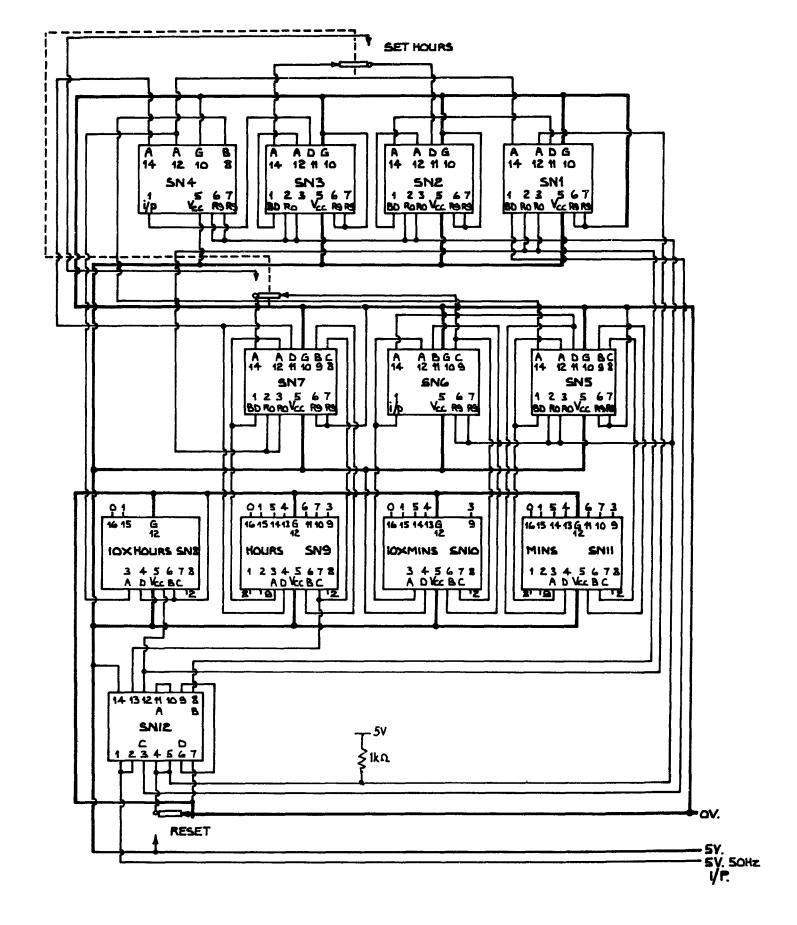

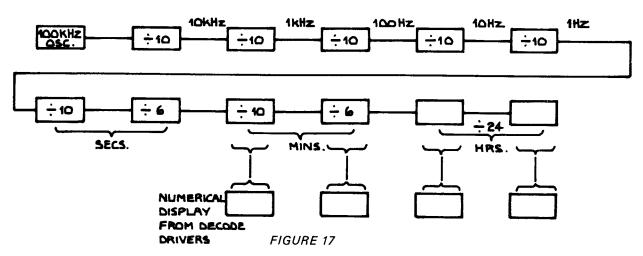

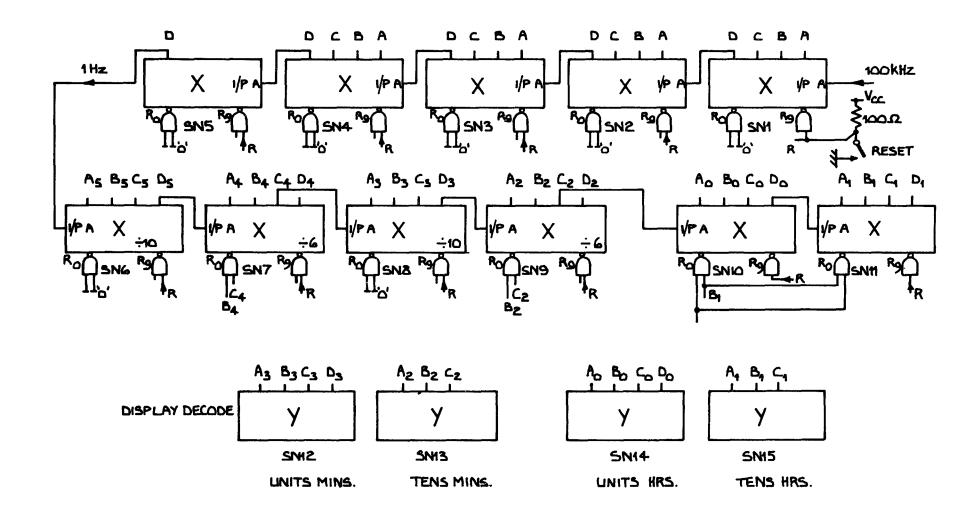

| 812          | Twenty-Four Hour Clock            |             |          |        |        |       |     | <br>240 |

|              | Ripple Counter Using TTL I        |             | p-Flops  |        |        |       |     | <br>242 |

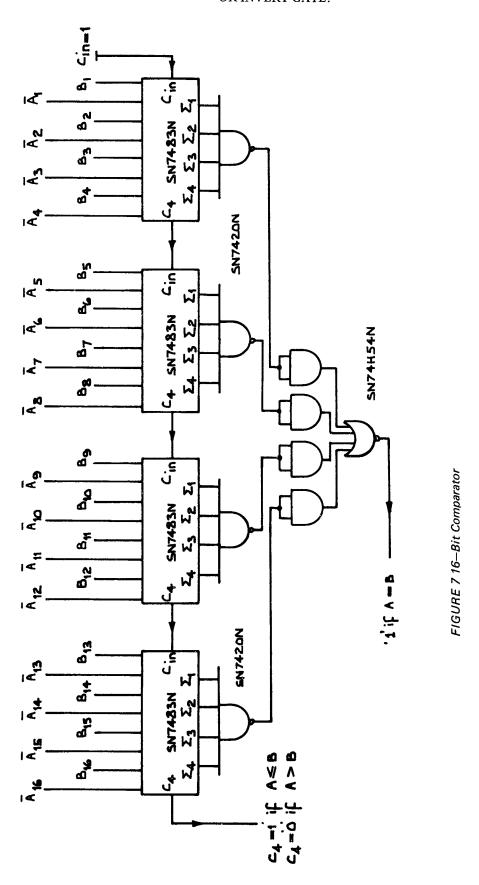

|              | 16 Bit Parallel Binary Compa      |             |          |        |        |       |     | <br>242 |

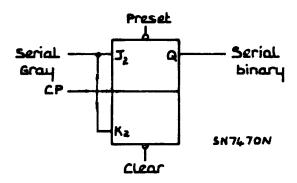

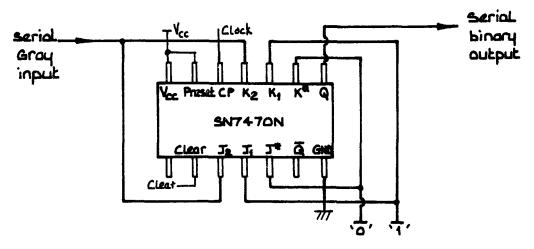

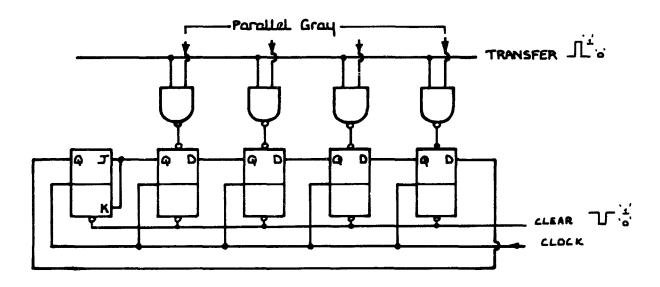

| 821          | Serial Grey to Binary Conver      | rter        |          |        |        |       |     | <br>244 |

| <b>ક</b> શ્4 | Decade Counter with Uncon         | ditional Pr | eset Fac | cility |        |       |     | <br>246 |

| 825          | Dividing by Numbers Other         | than Ten w  | vith the | SN749  | 0N     |       |     | <br>248 |

| 1326         | Twenty-Four Hour Clock Us         | sing only S | N7490N   | N Deca | de Cou | nters |     | <br>250 |

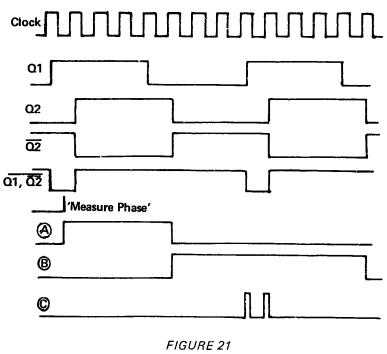

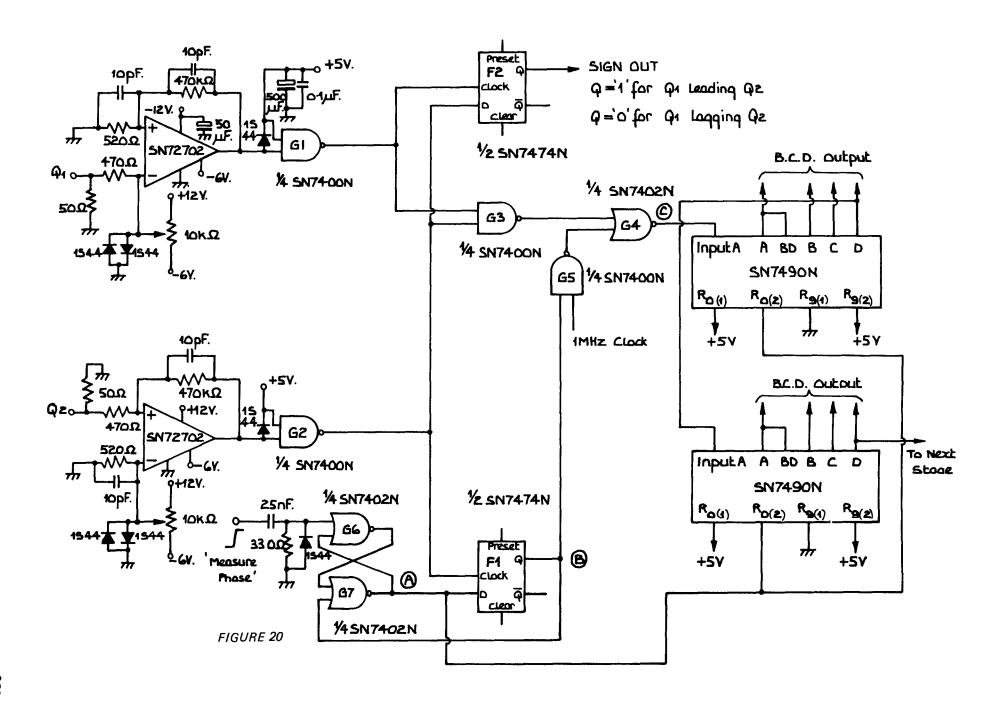

| 836          | A Digital Phase Meter             | • •         |          |        |        |       |     | <br>252 |

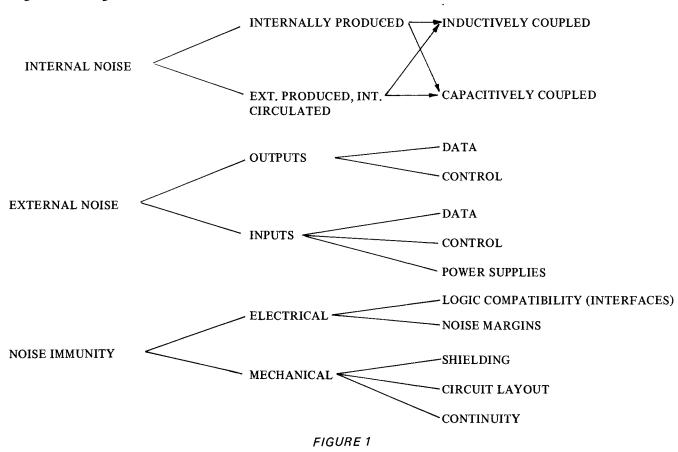

| Chapter XVI  | USE OF TTL INTEGRATE              | ED CIRCU    | ITS IN   | INDU   | STRIA  | L NO  | ISE |         |

|              | ENVIRONMENTS                      |             |          |        |        |       |     | <br>254 |

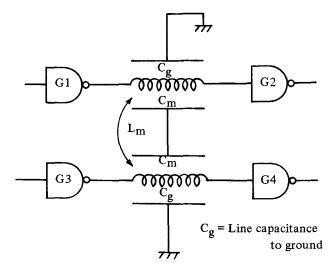

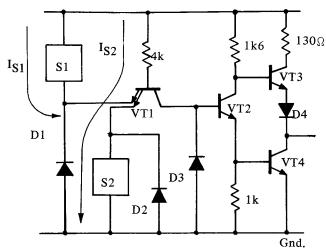

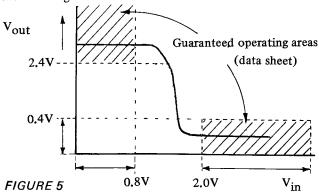

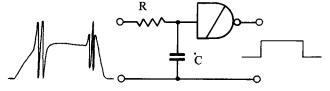

|              | Internal Noise Generation         |             |          |        |        |       |     | <br>254 |

|              | External Noise                    |             | .:       |        |        |       |     | <br>255 |

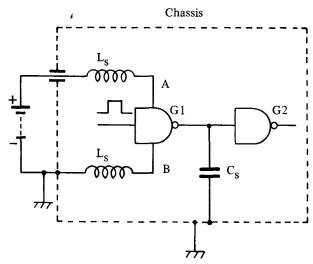

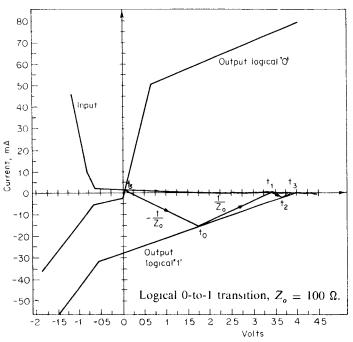

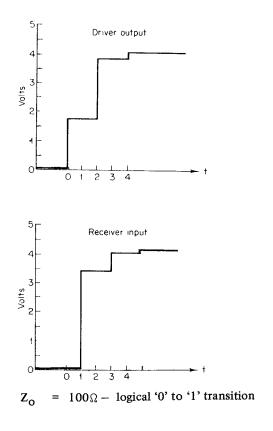

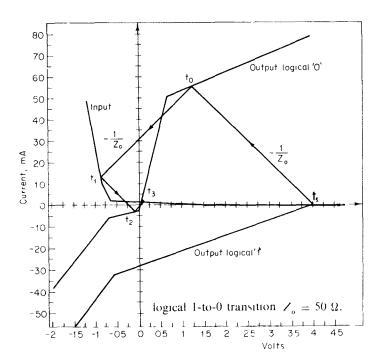

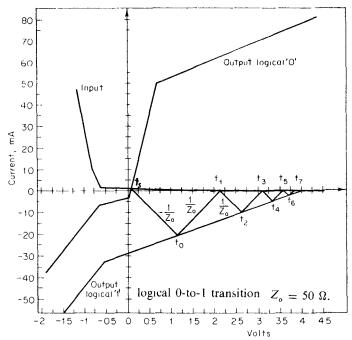

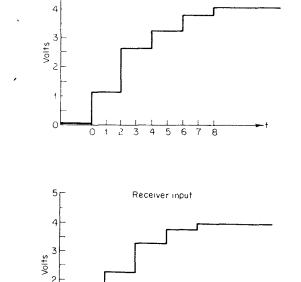

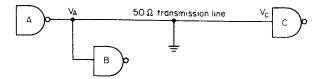

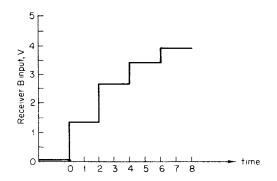

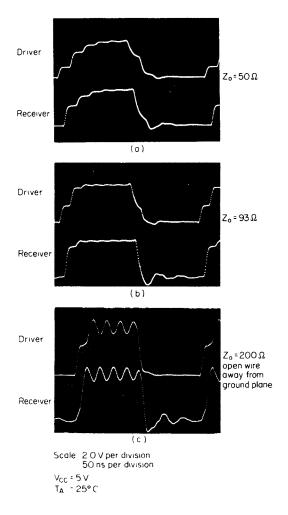

|              | <b>Driving Transmission Lines</b> |             |          |        |        |       |     | <br>259 |

|              |                                   |             |          |        |        |       |     | <br>264 |

|              | General Rules                     |             |          |        |        |       |     | <br>264 |

|              | Annendiv                          |             |          |        |        |       |     | 266     |

#### **SECTION 1.**

POWER CONTROL WITH TRIACS, THYRISTORS, AND UNIJUNCTION TRANSISTORS

#### I TRIACS - THEORY AND GENERAL APPLICATIONS

#### By Jurek Budek

#### INTRODUCTION

The name of Thyristor is derived from the Greek word " $\eta \theta v \rho a$ " meaning a door. Thus, strictly, all four layer (PNPN) devices with gates, such as silicon controlled rectifiers (SCR), bidirectional switches (Triacs) and gate controlled switches should be called Thyristors, However, the word "Thyristor" has become accepted in the past few years to mean a silicon controlled rectifier (SCR). In this book, therefore, it will have the same meaning.

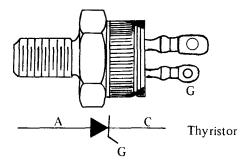

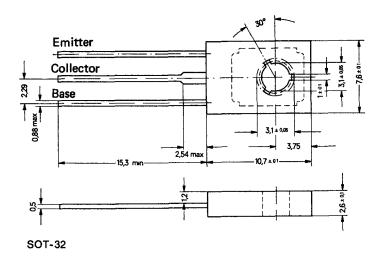

Thyristor: A semiconductor switch. It is most commonly a three terminal semiconductor device with electrical characteristics similar to those of a thyratron, except that it has a very low internal dissipation. The unilateral Thyristor, commonly called SCR, and the bilateral switch commonly called Triac, are often mounted in a stud package as shown in Figure 1. The Thyristor has three connections, where the stud is the anode, the largest of two isolated leads on the case is the cathode, and the smaller lead is the gate. The Triac is identical with the Thyristor, except that the large lead is normally referred to as Main Terminal 1 (MT1) and the case as Main Terminal 2 (MT2).

FIGURE 1

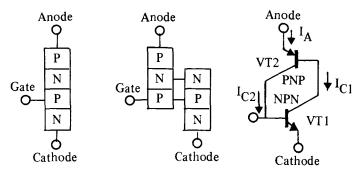

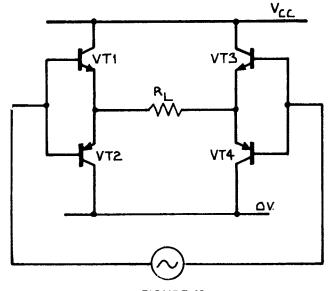

#### How a Four Layer (PNPN) Device Works

Four layer (PNPN) devices in use are either in one of two stable states; that is, they are either 'on' or 'off'. They are like switches in that they can be either open ('off') or closed ('on').

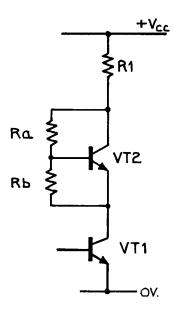

A two transistor analogy can best describe their action:

FIGURE 2

$I_A$  (total anode current) =  $I_{C1} + I_{C2}$

$$I_{A} = \frac{(1 + h_{FE1}) (1 + h_{FE2}) (I_{CBO1} + I_{CBO2})}{1 - (h_{FE1} h_{FE2})}....(1)$$

With positive bias applied to the transistor pair (+ anode to cathode), hFE1 and hFE2 are both low and their product is less than unity. This is true since only small leakage currents are involved. Since hFE is directly proportional to the collector current, the current gains are also small. Thus, the equation develops a value of IA that is only slightly higher than the sum of the collector-base leakage currents ICB01 + ICB02.

Regeneration takes place if the product of hFE1 and hFE2 is made to approach unity. In equation (1), IA approaches infinity. Here the current increases and drives the transistor pair into saturation, thus turning it into the 'on' state. Thereafter, no further gate signal is required to maintain the 'on' state as long as the anode current is above the holding current.

Regeneration to cause an 'on' condition may be made to occur by:-

- (i) applying a gate to cathode voltage (external base current to VT1) which causes the 'on' state to be reached by transistor action.

- (ii) applying a fast rising voltage (dv/dt) to initiate turn

- (iii) exceeding the avalanche breakover voltage  $(V_{\mbox{\footnotesize{BO}}})$  of the device.

Thyristors require a positive gate to cathode voltage and will turn 'on' only when the anode voltage is positive with respect to the cathode.

Triacs, on the other hand, can be designed to turn 'on' with either polarity of gate to MT1 and with either polarity of applied voltage between MT1 and MT2. For example, the Triac can be turned 'on' when MT2 is positive with respect to MT1 and the gate is negative with respect to MT1.

#### **FEATURES**

#### **Thyristors**

- 1. Three terminal devices similar to the thyratron except that it has a lower internal dissipation loss.

- Conducts current in one direction only. (Figure 3).

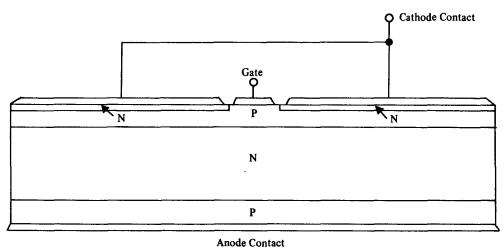

Basic construction of the Thyristor is shown in Figure 4

- Case is normally anode.

- 4. Triggered into conduction with a positive voltage on the gate of the device with respect to the cathode, with the main positive voltage applied to the anode.

- 5. Gate loses control when device is triggered on.

- 6. Turn on time is typically  $1\mu$ s.

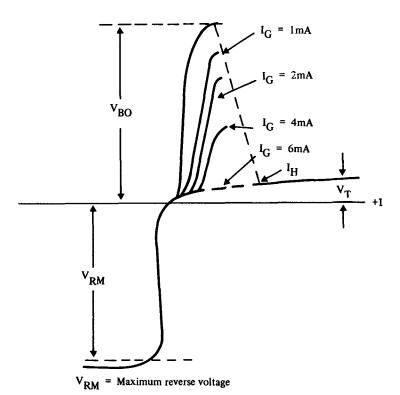

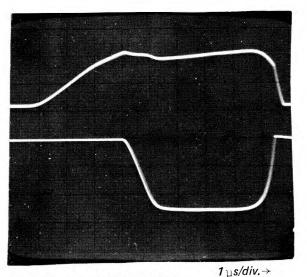

FIGURE 3 Typical Thyristor Characteristics

- Conduction ceases when current drops below the holding current.

- 8. Turn off time is typically  $5 60\mu s$ .

- Technology is planar up to 2A, 250V and mesa up to 1000A, 2000V.

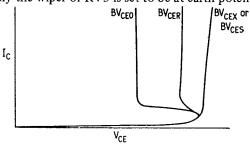

In a Thyristor, increasing the forward voltage does tend to increase the leakage current very slightly until the point at which avalanche begins. On exceeding this value, the leakage current will change rapidly into full conduction and the Thyristor will stay 'on' until the anode current drops below the holding current. On increasing the gate current, the forward break over voltage is reduced as shown in Figure 3. If the gate current is sufficiently large the forward blocking voltage is removed and Thyristor behaves as a diode.

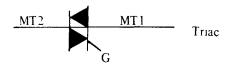

#### **Triacs**

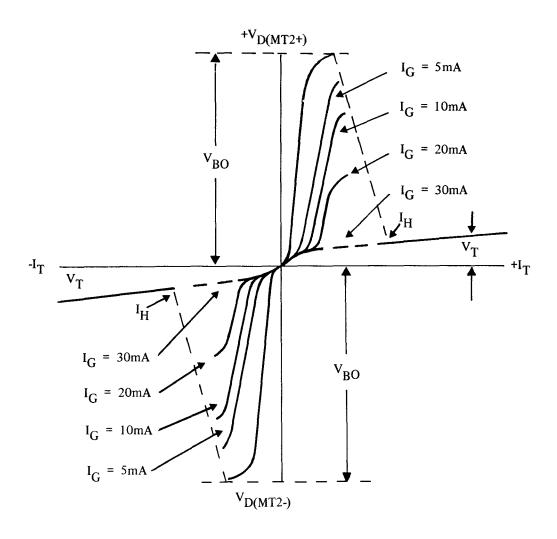

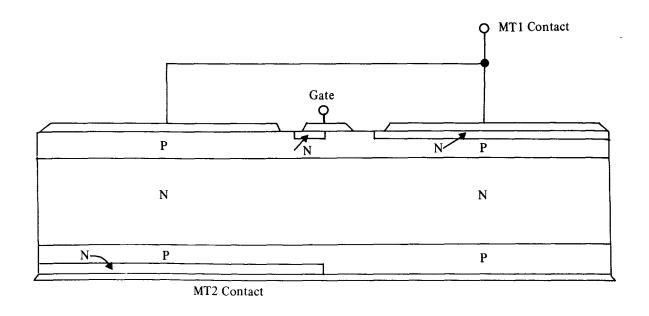

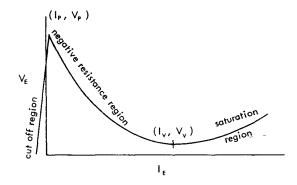

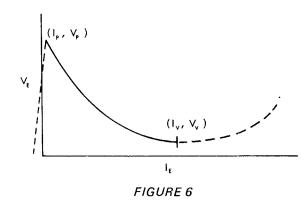

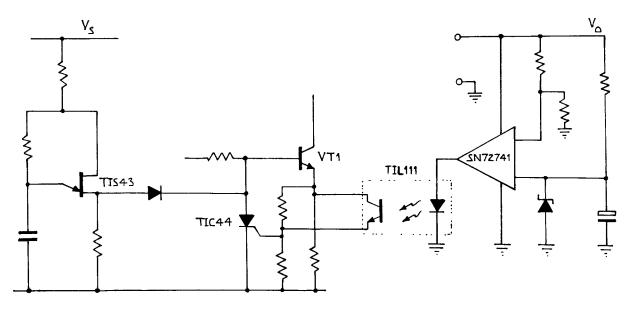

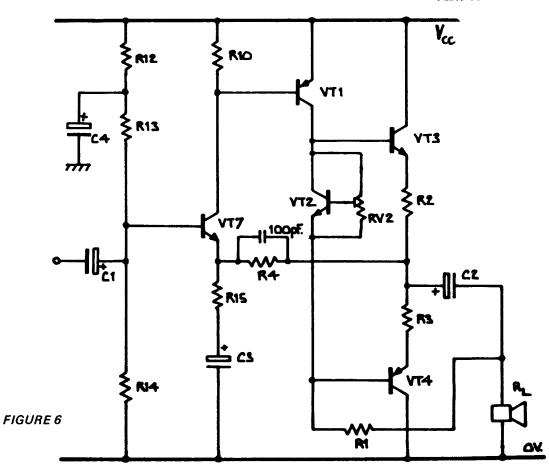

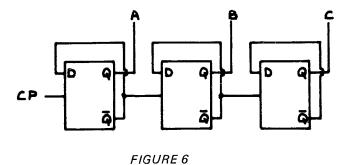

- 1. Conducts current (Figure 5) in either direction, similar to Thyristors operating in inverse parallel connection. Figure 6 shows basic Triac structure.

- May trigger into conduction either by positive or by negative gate signals with either polarity of main terminal voltage.

- 3. Case is normally main terminal 2 (MT2).

- 4. Gate loses control when device is triggered on.

- 5. Turn on time is typically  $1\mu$ s.

- Conduction ceases when current drops below minimum holding current (IH).

- 7. Turn off time is typically  $50\mu$ s.

- 8. It offers simplified circuitry over two Thyristors, eliminating additional components needed in the triggering.

- Present technology is limited to mesa, up to 200A, 1000V.

FIGURE 4

Basic Thyristor Structures

FIGURE 5 Typical Triac Characteristics

FIGURE 6 Basic Triac Structure

#### TRIAC ELECTRICAL CHARACTERISTICS

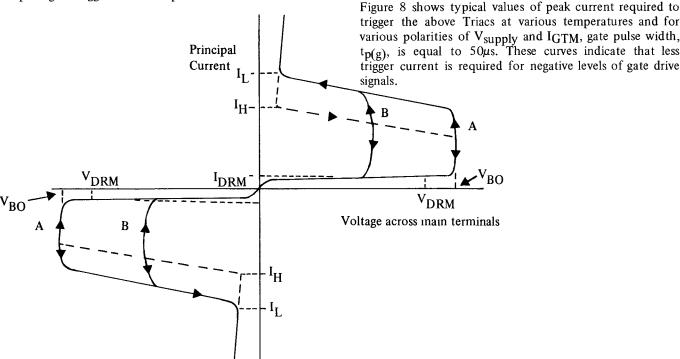

When the Triac is turned 'on', the current which flows between MT1 and MT2 is referred to as the principal current. The principal voltage-current characteristics of a Triac are shown in Figure 7; the voltage at MT1 is taken as a reference potential. Curve A is the V-I trace for a zero level gate current, and shows that for either polarity of applied voltage, the principal current is small and reasonably constant until the breakover voltage VBO is reached. Curve B is the V-I trace for a gate current to the Triac; this current is measured with respect to MT1. Either positive or negative values of gate current (and hence, gate voltage) may be used to trigger the device. A hysteresis effect is noted along the current axis; two current levels, the latching current, IL, and the holding current, IH, are illustrated. The gate-drive signal must increase the principal current above the level of II in order for the Triac to latch into conduction.

Once the device is on at a high current level, the principal current must drop below the IH level before the device will turn 'off'.

Figure 7 shows that the Triac operates in quadrants 1 and 3 of the V-I curve. As a rule, the Triac is difficult to trigger when device operation is in the third quadrant and the gate current is positive. Consequently, the Triac is generally not operated in this mode.

The repetitive peak off state current, IDRM, illustrated in Figure 7 is measured at a value of repetitive peak reverse voltage, VDRM, applied to MT2. The value of this reverse voltage is selected to be below the breakdown voltage, VBO, of the device. A worst case condition for this measurement is the application of a DC reverse voltage equal to the magnitude of VDRM.

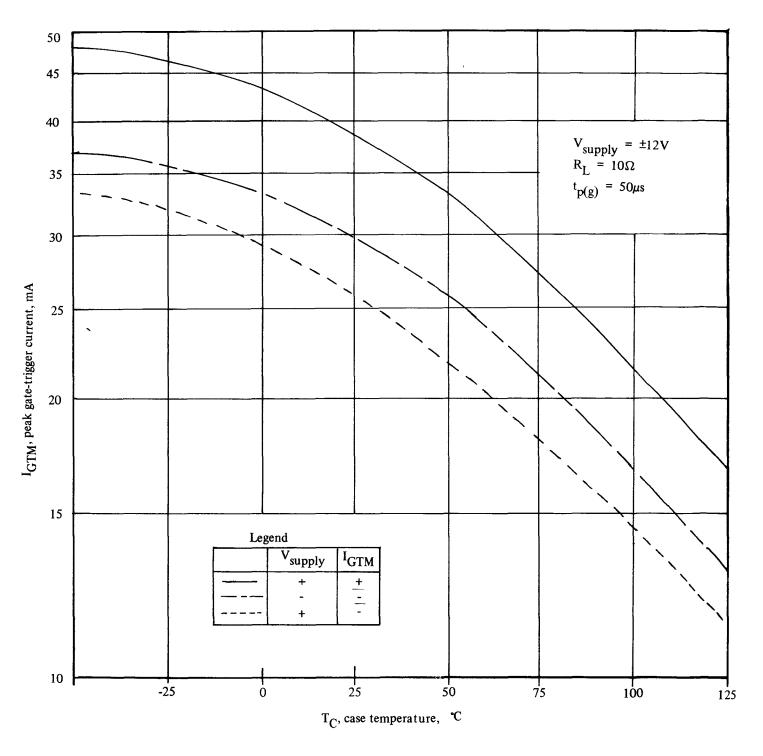

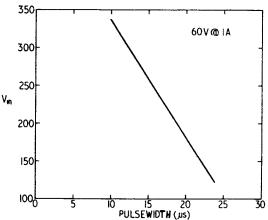

As the Triac is controlled by a charge at the gate terminal, the peak gate trigger current required to turn 'on' a device is dependent upon the width of gate-drive pulse. The peak gate trigger current,  $I_{GTM}$ , is also determined by the polarity of voltage  $V_{supply}$  across the main terminals, in addition to the polarity of gate voltage. Values of  $V_{supply}$ , load resistance and pulse width are specified for the measurement of  $I_{GTM}$  by the Triac manufacturer.

The peak gate trigger voltage, V<sub>GTM</sub>, is measured under the same circuit conditions as used for the measurement of I<sub>GTM</sub>. This voltage parameter is simply the voltage drop from gate to MT1.

Triacs, like Thyristors, have a critical rate of rise of 'off' state voltage designated dv/dt. This is a measure of the maximum rate at which 'off' state voltage can be applied to the device, and is generally given in  $V/\mu s$ . False firing may occur if the dv/dt rating is exceeded.

'On' state voltage drop across the main terminals is another important parameter of the Triac. This voltage is specified as V<sub>TM</sub>, the peak 'on' state voltage. It is measured at a peak 'on' state current, I<sub>TM</sub>.

#### T.I. TRIACS

Texas Instruments at present manufacture Triacs of rating up to 40A rms and up to 600V, continuous 'off' state voltage (VD). (See list in Appendix). Several significant features of these Triacs are evident from T.I. Triac data sheets. The maximum operating temperature of 125°C is larger by 25% than that of most other Triacs. The typical dv/dt rating of  $300\text{V}/\mu\text{s}$  at  $125^{\circ}\text{C}$  permits these Triacs to be used with inductive loads. An increased value of IGTM is required to trigger a device in exchange for a higher dv/dt rating. Because of the reduced sensitivity for IGTM, these devices are difficult to trigger with a positive gate current when operating in the third quadrant, Consequently, the data sheet does not specify this type of operation.

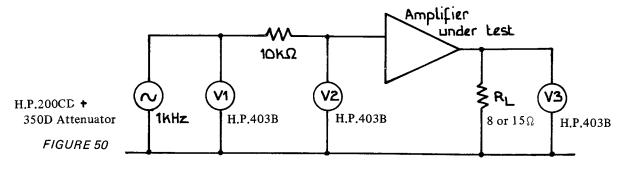

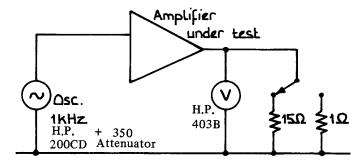

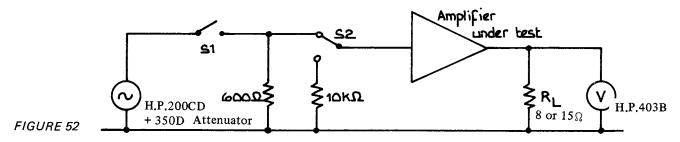

FIGURE 7 Principal Voltage Current Characteristics of the Triac

FIGURE 8 Typical curves of peak gate-trigger current versus case temperature for various polarities of  $V_{supply}$  and  $I_{GTM}$ .

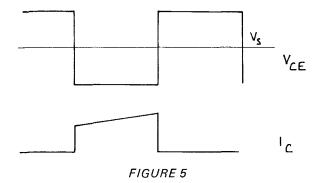

#### Comparison of Thyristor and Triac Circuits

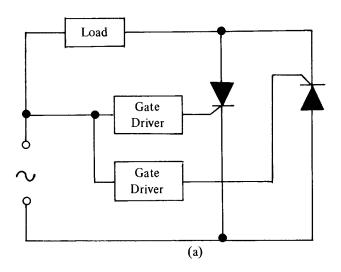

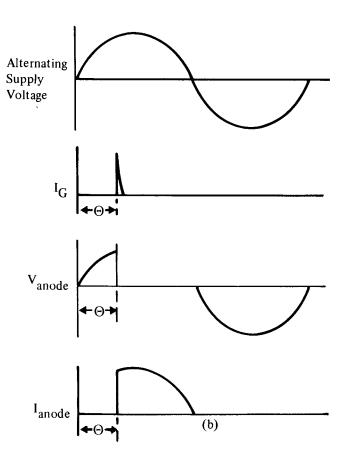

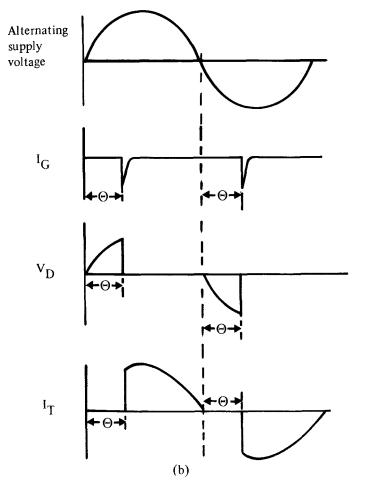

A conventional method of providing full-wave phase control utilises two Thyristors connected as shown in Figure 9 (a). Each device conducts load current for up to a half cycle period, one during the positive and the other during the negative cycle of input AC waveform. This is accomplished by applying gate turn 'on' current during the interval that the anode voltage of the Thyristor becomes positive with respect to its cathode. Figure 9(b) shows typical voltage and current waveforms in the resistive circuit: gate current IG, anode voltage,  $V_{anode}$ , and anode current,  $I_{anode}$ , are shown for one Thyristor. The gate-drive current is delayed by  $\Theta$  electrical degrees for this particular case. By advancing or retarding  $\Theta$ , proportional phase control is obtained.

This circuit is highly efficient, as the Thyristor has a relatively low power dissipation in both the 'on' and 'off' state. In addition, the Thyristor switches between these two states in only a few microseconds. An undesirable feature of using two Thyristors for full wave control is the requirement that two separate gate drive signals must be provided. This is not necessary by using the Triac in place of two Thyristors. Furthermore, only one power component is needed instead of two, hence simplicity in mounting.

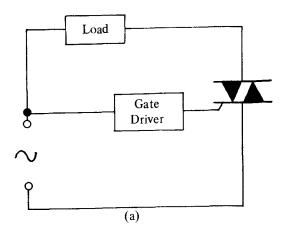

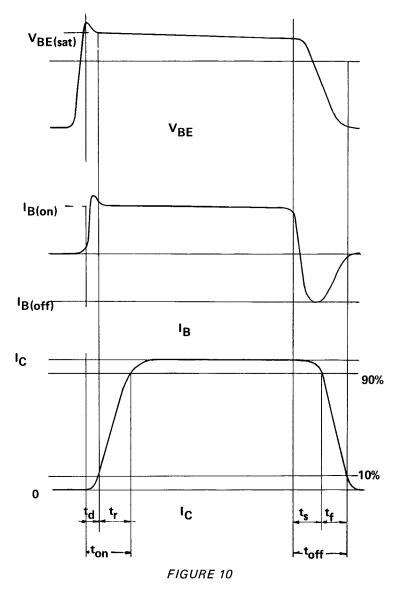

Figure 10(a) shows full-wave phase control in resistive circuit utilising a Triac. Waveforms of alternating supply voltage, gate current, IG, voltage, VD, across the main terminals and principal current, IT, are shown in Figure 10(b). A comparison of Figures 9 and 10 show that the Triac is electrically similar to an inverse parallel connection of two Thyristors, with a common gate for the two devices. Consequently, the gate-drive circuit is less complex for the Triac than for the two Thyristors. The ability to conduct either polarity of load current makes the Triac well suited for full-wave phase control.

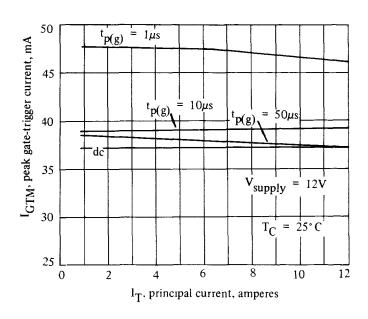

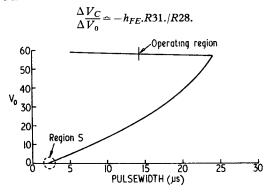

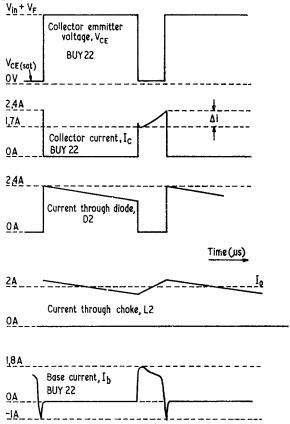

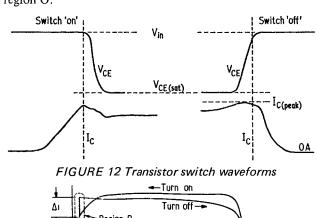

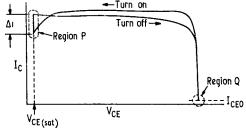

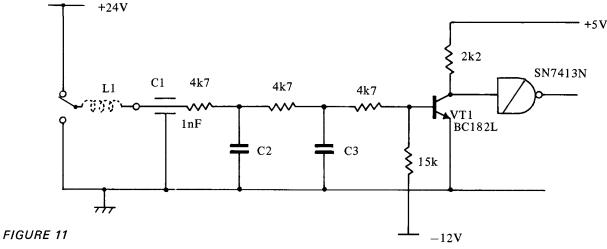

The manner in which the required gate-trigger current varies as a function of current through the main terminals is shown in Figure 11 for various widths of gate drive pulses. Data is plotted for device operation in the first quadrant and for positive gate signals; gate current requirements are largest for these conditions. These curves show that the gate-trigger current for a given width of gate drive signal is relatively constant over a wide range of 'on' state currents. It is found that the gate-drive current is independent of Vsupply.

In order for a Triac to be triggered to the 'on' state, the gate drive signal must not be removed until the principal current, I<sub>T</sub>, rises above the latch current I<sub>L</sub>. Figure 12 shows I<sub>L</sub> as a function of gate pulse width for two different values of V<sub>supply</sub>. These curves show that the value of I<sub>L</sub> decreases as the gate drive pulse is made wider.

Thyristor full-wave phase-control circuit (a)

Voltage and current waveforms (b) (Resistive loads)

FIGURE 9

Triac full-wave phase-control circuit

FIGURE 11 Typical curves of peak gate-trigger current versus principal current for various widths of gate-drive pulse.

30 = 300mA  $I_{\mathbf{G}}$ 25 IL, latching current, mA  $T_C = 25 \cdot C$  $V_{\text{supply}} = 12V$ 20 V<sub>supply</sub> 15 10 5 40 0 50  $t_{p(g)}$ , width of gate-drive pulse,  $\mu$ s

FIGURE 12 Typical curves of latching current versus width of gate-drive signal, for two values of  $V_{supply}$

Voltage and current waveforms (Resistive load)

FIGURE 10

#### **Triac Applications**

There are several circuit configurations for triggering the gate of a Triac. To a large extent, the trigger circuit depends upon the particular applications. Regardless of which trigger circuit is used, the gate turn-on current and the latching current must have at least minimum levels.

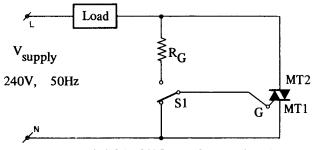

The gate drive circuit may consist simply of a resistor,  $R_G$  and a switch, S1, connected as shown in Figure 13. Gate current is positive when MT2 is positive, and negative when MT2 is negative. The undersirable operating mode of a positive gate current and a negative MT2 will not occur. The Triac will turn 'off' each time the principal current drops to zero. The recommended value for  $R_G$  is about 400 ohms for 240V A.C. supply. This circuit can be used as a solid state contactor.

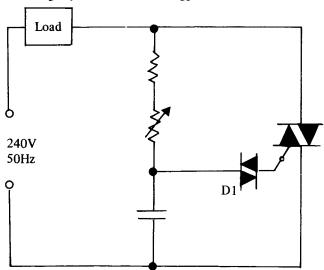

FIGURE 13 OFF - ON Power Control Circuit

As a spread in  $I_{GTM}$  among various Triacs exists, each device would conduct at a different value of  $V_{supply}$ . This problem of variation in the gate-trigger point can be overcome by using a voltage-threshold detector as shown in Figure 14. A bidirectional trigger diode D1 may be used to detect both polarities of  $V_{supply}$ . Similar results can be obtained by using a single phase bridge, connected in series with the gate of a Triac and shorting out the DC output of the bridge by a unidirectional trigger diode.

FIGURE 14 Single phase control using bidirectional trigger diode

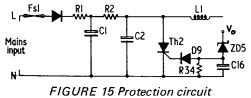

In order to achieve an extended range for gate triggering a Triac, a double CR network may be used as shown in Figure 15. This circuit offers a smooth control of a DC motor and lamp dimming without a flicker. Voltage across trigger diode D1 is shifted in Phase and attenuated by two CR networks. When this voltage rises to the avalanche

breakdown voltage of D1, a pulse of turn 'on' current will flow through the gate of the Triac.

FIGURE 15 Phase Control with Bidirectional Trigger Diode

A light sensitive device can be utilised in controlling the operation of a Triac. Such a circuit could be used for applications as burglar alarms, automatic opening of doors, etc. This circuit is shown in Figure 16.

FIGURE 16 Triggering of Triac by Light Sensing Device

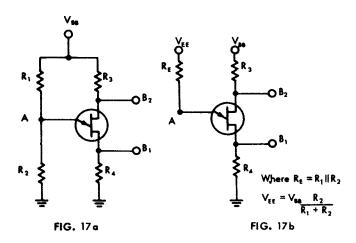

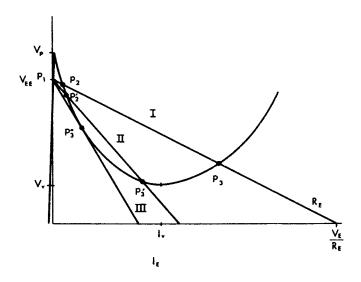

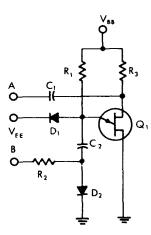

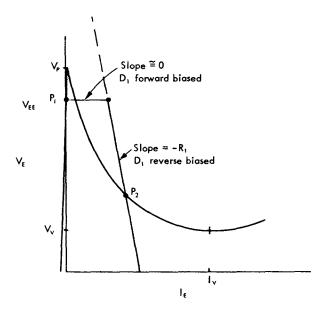

Integrated logic circuits may be used to control the Triac. Figure 17 shows an example of this.

FIGURE 17 Integrated logic circuit for Triac trigger control

All these circuits are described in detail in later chapters where component values are given.

#### **PROTECTION**

To ensure the satisfactory operation of equipment using semiconductor devices, the problem of protection must be solved. There are several points to which a designer must pay attention, i.e. the rate of rise of voltage, (dv/dt), the rate of rise of current, (di/dt), voltage surges and overloads.

#### 'Commutation' and 'Critical dv/dt'

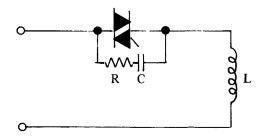

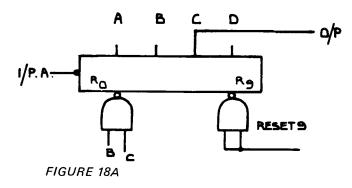

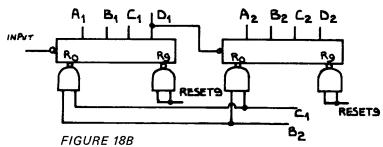

When there are inductive loads, Triacs and Thyristors are subjected to a sudden rise of voltage, see Figure 18. If a device is not capable of withstanding such fast rises in voltages, it will lose control. The problem of dv/dt becomes important especially when dealing with 'commutation dv/dt' as the capability of a device is somewhat lower in the commutation case.

From Figure 18 it can be seen that two Thyristors connected in inverse parallel are subjected to 'critical dv/dt' as opposed to a Triac in a similar circuit being exposed to 'commutation dv/dt'. The 'critical dv/dt' can be defined as a blocking dv/dt applied to a device after the device has fully recovered from a principal current conduction. 'Commutation dv/dt' occurs when the blocking voltage is being stressed across the device during the recovery time from the principal current. Malfunctioning can even occur due to the fast voltage transients initiated by switching, etc. This characteristic phenomenon of Triacs and Thyristors is caused by the CR coupling between gate and MT2 terminal for Triacs and gate and anode for Thyristors. (R is the impedance between MT1 and gate). Unwanted turn 'on' at full voltage could bring some problems, especially when the equipment is feeding low impedance loads such as stationary motors or a bank of filament lamps. Excessive currents flowing, even for half a cycle, could blow the protective fuses or damage some of the semiconductors. The gates of the Triacs will resume control after half a cycle. The values of dv/dt are published in the manufacturers' data sheets. One way of slowing down the voltage rise of the switching supply voltage or transients is to bring the circuit into oscillation by adding a CR network and inductance if required. A suitable place to connect R and C is across the Triac.

Solving and analysing the following equation:—

$$L(di/dt) + Ri + (1/C) \int i.dt = V_{max}$$

..... (2) gives

$$(dv/dt)_{max} = V_{max} / \sqrt{LC}$$

hence

where  $V_{max}$  = peak supply voltage

and dv/dt = values obtained from the manufacturers data sheets  $(V/\mu s)$

If the supply reactance = X%, then

$$(\omega L \cdot I \cdot 100) / V = X \cdot \dots (4)$$

where I = supply current, rms

V = supply voltage, rms

Substituting L from equation (4) into equation (3), the value of the capacitor becomes:—

$$C = \frac{2.V.\pi.I}{(dv/dt)^2 \cdot 10^2 \cdot X} \mu F \dots (5)$$

assuming a frequency of 50Hz and (dv/dt) in volts/us.

The discharge of the capacitor through a Triac should be limited by adding a series resistor. This resistor should also be able to damp the ringing of the capacitance with the load inductance.

A suggested value for R is: -

$$R = 2\sqrt{\frac{L}{C}}$$

(a) Thyristors in inverse parallel

Firing angle

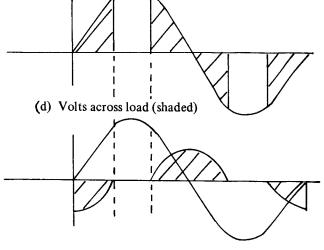

(c) Voltage across Triac and Thyristors (shaded)

(e) Current (shaded)

FIGURE 18 dv/dt in the inductive loads

#### Rate of Rise of Current (di/dt)

If the rate of rise of current is very high when compared with the speed with which the current turning 'on' can spread across the junction of the Triac or Thyristor, a local "hot spot" may develop causing a device to fail.

In most cases, there is no cause for concern as sufficient inductance exists in the circuit. However, where there is a fast rise of current, the value of di/dt should be examined and a choke added in the circuit to slow down the rise if necessary.

The value of inductance can be established from the expression:—

$$e = L.\frac{di}{dt} \qquad (7)$$

where e is a supply voltage and di/dt is the maximum permissible value of the rate of rise of current.

#### Voltage Transients

Diodes and Thyristors can be destroyed when subjected to excessive voltage transients, unless they incorporate avalanche characteristics. The Triac, being a bidirectional switch, will simply break over in one or other direction, turning 'on' into conduction. In spite of these self protective capabilities, the turning 'on' of a Triac, even for one isolated pulse, is not acceptable as explained on the previous page. An effective surge absorbing device, therefore, is necessary for reliable operation. Voltage transients can be initiated by various means such as switching transformers, inductors, from Thyristor circuits as commutation spikes, etc.

The suppression of transient voltages can easily be achieved if the sources and causes of transients are known. Voltage transients generated by switching 'off' transformers are known to a certain extent. The energy stored in the magnetic field can be evaluated from the equation  $E_{\text{(energy)}} = \text{Li}^2/2$  where 'i' is peak magnetising current. By using a CR network as a surge absorbing device, a simple comparison of the magnetic energy with energy to be absorbed by the capacitor used  $(CV^2/2)$  will give its required value. There are many surge absorbing devices on the market in the form of CR networks, selenium plates connected back to back, or silicon carbide units. If the magnitude of the transient is unknown, a trial and error approach to the problem is often unavoidable.

#### **Overloads and Short Circuits**

The decision on what form the protection of an equipment should take rests with the designer. Depending on the application, the cost of protective devices must obviously be related to the price of the equipment. There are numerous problems to be borne in mind at the designing stage. The protective devices should be chosen and arranged in such a way as to obtain the desired discrimination.

AC and DC circuit breakers, AC and DC contactors, fuses and current limiting circuits are normally used to protect semiconductor equipments against overloads. There are some basic points which it may be helpful to remember. A circuit breaker is designed to protect against overloads and

to open and isolate a healthy circuit during the short circuit. Contactors are, as a rule, cheaper than circuit breakers and are used for frequent switching and operation at overloads but must be backed up by fuses as they do not have the clearing capability during short circuits. Fuses, however, are the cheapest and most commonly used in medium and small sized equipments for protection against damage to wiring and components in heavy overloads and short circuits. When frequent faults are expected, the loss of fuses during each failure may present an economic problem. A circuit breaker or contactor could then become a more attractive proposition.

In order to withstand an inrush current to a transformer, the fuse in the input side of the transformer is usually rated at twice or three times the nominal current, unless other provision is made to reduce the inrush current.

When fuses and breakers are adapted for the protection of Triacs, correct discrimination can be achieved by studying the overload characteristics of fuses, Triacs and circuit breakers. Normally Triacs or Thyristors will be protected against a short circuit and a heavy overload by fuses, and against other conditions of overload by circuit breakers. Care must be taken to keep below the Triac overload curve at every point, by either fuse or breaker characteristics. The transformer reactance is a useful tool to control a fault current. The peak fault current can be evaluated from a transformer secondary rms current by using the following formula:—

$$I_{s/c peak} = (I_{rms} . \sqrt{2} . 100) / X$$

where X is a percentage reactance of a system (transformer plus supply). As an example, in three phase bridge connection, each device will carry a current approaching sinusoidal shape for 180° during short circuit and not 120° as in the case of a nominal load. Then the peak value, related to the nominal DC current, will be:—

$$I_{s/c \text{ peak}} = \frac{I_{rms}.\sqrt{2.100}}{X} = \frac{2.\sqrt{2}. I_{DC}.100}{\sqrt{3}.X}$$

Hence

$$I_{s/c peak} = \frac{116 \cdot I_{DC}}{X} \qquad (8)$$

From equation (8), it can be seen that the peak fault current can vary with the variation of transformer reactance. Furthermore, the first pulse of a fault current can be much higher than a steady state short circuit. This first pulse is called an "asymmetric peak" and its magnitude is a function of the "R/X" of the circuit. For practical purposes, this value can be assumed to be 1.6 times the symmetric short circuit. The asymmetric peak current is very important when dealing with isolated fault pulses and for obvious reasons can be neglected in long term overloads.

The knowledge of i<sup>2</sup>t (let through energy) is very useful in cases where a fault current is expected to be interrupted between 2 and 8 milliseconds. In this time interval, the i<sup>2</sup>t can be assumed to be approximately constant. A simple comparison of the Triac 'i<sup>2</sup>t' with total fuse 'i<sup>2</sup>t' will give the rating of the fuse needed. The total 'i<sup>2</sup>t' of the fuse consists of pre-arcing and arcing 'i<sup>2</sup>t. The technique of using 'i<sup>2</sup>t' is dicussed in an article, reference 2.

#### **COOLING**

As the Triac can be used in various circuit configurations, it will be necessary to know the power dissipation of the device in terms of rms or mean current needed. Most of the Triac manufacturers provide information on power dissipation with reference to the rms current.

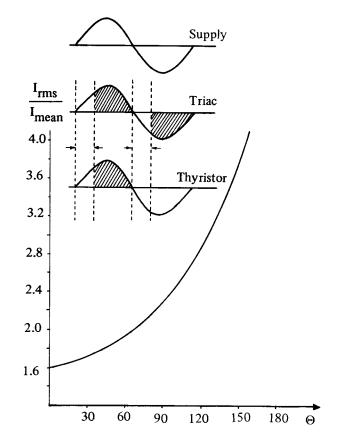

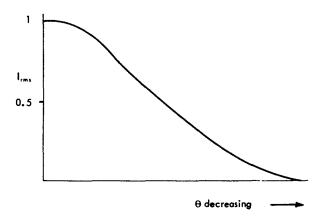

Figure 19 shows the ratio of current  $\frac{\text{rms}}{\text{mean}} = f(\Theta)$ , where  $\Theta$

is the delay angle. It should be noted that the rms value and mean value are calculated for a Thyristor with one pulse per one cycle, for the same peak current.

$$I_{rms} = \sqrt{\frac{1}{2\pi}} \int_{a}^{\pi} (I_{m} \sin X)^{2} dx =$$

$$\frac{I_{\rm m}}{2} \sqrt{\frac{1}{\pi} \left(\pi - a + \frac{\sin 2a}{2}\right)} \tag{9}$$

$$I_{\text{mean}} = \frac{1}{2\pi} \int_{a}^{\pi} I_{\text{m}} \sin X \, dx = \frac{I_{\text{m}}}{2\pi} (1 + \cos a) \dots (10)$$

The results of the above formulae are shown in Table 1.

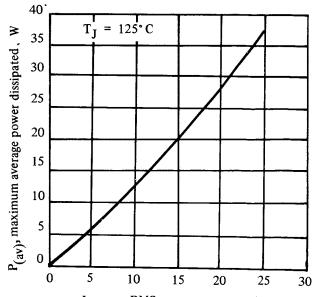

The minimum heat sink requirements may be calculated for any 'on' state current, heat sink combination by the following procedure:—

- (a) Determine the worst case power dissipation from Figure 20.

- (b) Calculate the maximum allowable case to free air thermal resistance, Θ<sub>C-A</sub>, by use of the equation:—

$$\Theta_{C-A} = \frac{T_J - T_A}{P(av)} - \Theta_{J-C} \quad \dots (11)$$

where  $T_{I}$  = junction temperature

$T_{\Lambda}$  = ambient temperature

P(av) = average power dissipation (Figure 20)

$\Theta_{J-C}$  = junction to case thermal resistance . = 1.75°/W

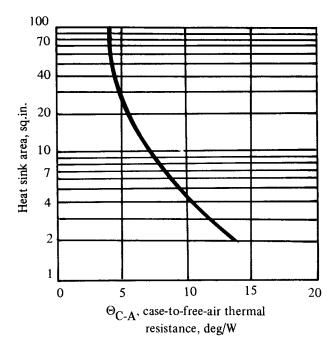

(c) If possible, determine the area of heat sink from Figure 21. If Figure 21 cannot be used, obtain further information from the heat sink manufacturer.

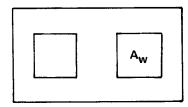

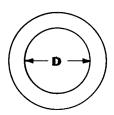

The Triac (Figure 21) is mounted in the centre of a square heat sink vertically positioned in still free air with both sides exposed. The heat sink area is twice the area of one side.  $\Theta_{C-A}$  includes the case to heat sink thermal resistance  $\Theta_{C-HS}$  in addition to the heat sink to air thermal resistance  $\Theta_{HS-A}$  and is defined by the equation:—

$$\Theta_{\text{C-A}} = \Theta_{\text{C-HS}} + \Theta_{\text{HS-A}} \quad \dots \qquad (12)$$

| Θ.                                    | 0     | 30    | 60    | 90    | 120  | 150    | 180 |

|---------------------------------------|-------|-------|-------|-------|------|--------|-----|

| I <sub>m</sub> X (rms)                | 0.5   | 0.492 | 0.447 | 0.353 | 0.22 | 0.084  | 0   |

| I <sub>m</sub> X (mean)               | 0.319 | 0.298 | 0.24  | 0.159 | 0.08 | 0.0215 | 0   |

| I <sub>rms</sub><br>I <sub>mean</sub> | 1.57  | 1.65  | 1.86  | 2.22  | 2.75 | 3.9    | ∞   |

FIGURE 19 Ratio between rms and mean versus delay angle 🖯

I<sub>T(rms)</sub>, RMS on-state current, A

FIGURE 20

Maximum average power dissipation versus rms on-state current

Table 1

FIGURE 21

Case to free air thermal resistance (1/32" thick aluminium heat sink)

#### Example

Determine the minimum size of 1/32" thick aluminium heat sink for safe operation of the Triac at an rms current of 10A, with the device mounted directly on the heat sink, given that the maximum:—

$$T_J = 125^{\circ} C$$

$T_A = 35^{\circ} C$

$\Theta_{J-C} = 1.75^{\circ}/W$

From Figure 20, P(av) - 13W for 10A rms. Using equation (11).

$$\Theta_{\text{C-A}} = \frac{125^{\circ}\text{C} + 35^{\circ}\text{C}}{13\text{W}} - 1.75^{\circ}/\text{W} = 5.1^{\circ}/\text{W}.$$

For  $\Theta_{\text{C-A}} = 5.1$  (Figure 21), the area is 24 square inches (total), the minimum dimension then is  $\int \frac{24}{2} = 3.5$ ". The

dimension of the heat sink will be 3.5" x 3.5".

#### **TERMS AND SYMBOLS**

dv/dt Critical rate of 'off' state voltage

IDRM Repetitive peak 'off' state current

IGM Peak gate current

IGTM Peak gate trigger current

IH Holding current

IL Latching current

IT 'On' state current (rms)

ITSM Peak 'on' state surge current

PG(av) Average gate power dissipation

PGM Peak gate power dissipation

T<sub>C</sub> Operating case temperature

VBO Breakover voltage

VD Continuous 'off' state voltage

VDRM Repetitive peak 'off' state voltage

V<sub>GM</sub> Peak gate voltage

VGTM Peak gate trigger voltage

V<sub>TM</sub> Peak 'on' state voltage

#### References

- 1. SCR Manual, GE, Fourth Edition.

- Protective Methods for Silicon Rectifier Equipment by J.A. Budek and A.H. Marchant in "Direct Current" November, 1964.

#### By Jurek Budek

#### INTRODUCTION

The performance and reliability of semiconductors have proved to be acceptable in a variety of applications ranging from space vehicles to high voltage light current or low voltage heavy current equipments.

The thyristor has established its position in the industrial and domestic field with the circuits for switching or controlling a.c. or D.C. powers. The Triac, replacing 'back to back' connected Thyristors, offers definite advantages in certain applications over the Thyristor.

The most common application of the Triac is that of controlling resistive or inductive loads. The triggering, however, in the two cases is different. This report will attempt to explain certain phenomena occurring in controlling these loads by Triacs together with recommended triggering for inductive or resistive loads.

## TRIAC OPERATED BY A TRIGGER DIODE (FOR RESISTIVE LOADS)

The trigger diode is the main device in the Triac gating circuit. Texas Instruments diffused silicon trigger device type TIC56 is a bidirectional device with forward and reverse breakover voltages of 32 ±6V. The breakdown differential voltage, however, is guaranteed to be within 2 volts which is very well suited for a symmetrical firing of the positive and negative half cycles. Furthermore, the breakback voltage 'V' is 8 volts and this, together with a triggering capacitor, provides sufficient energy to turn-on the Triac effectively. (Other devices with the same characteristics as the TIC56 are the TI43A/TIC57 with breakover voltages of 32±4V and 30±8V respectively.

#### A Simple Trigger Circuit

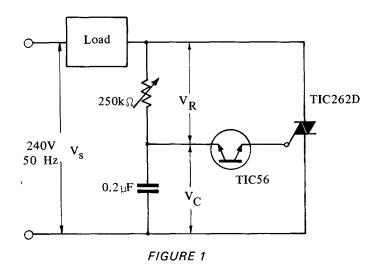

Two factors contribute to the phase shift in the circuit shown in Figure 1.

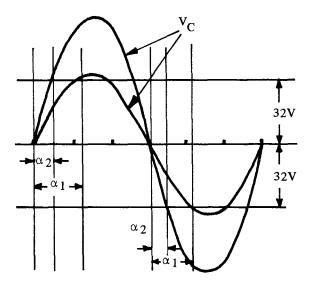

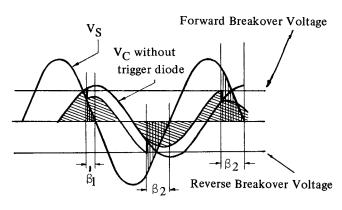

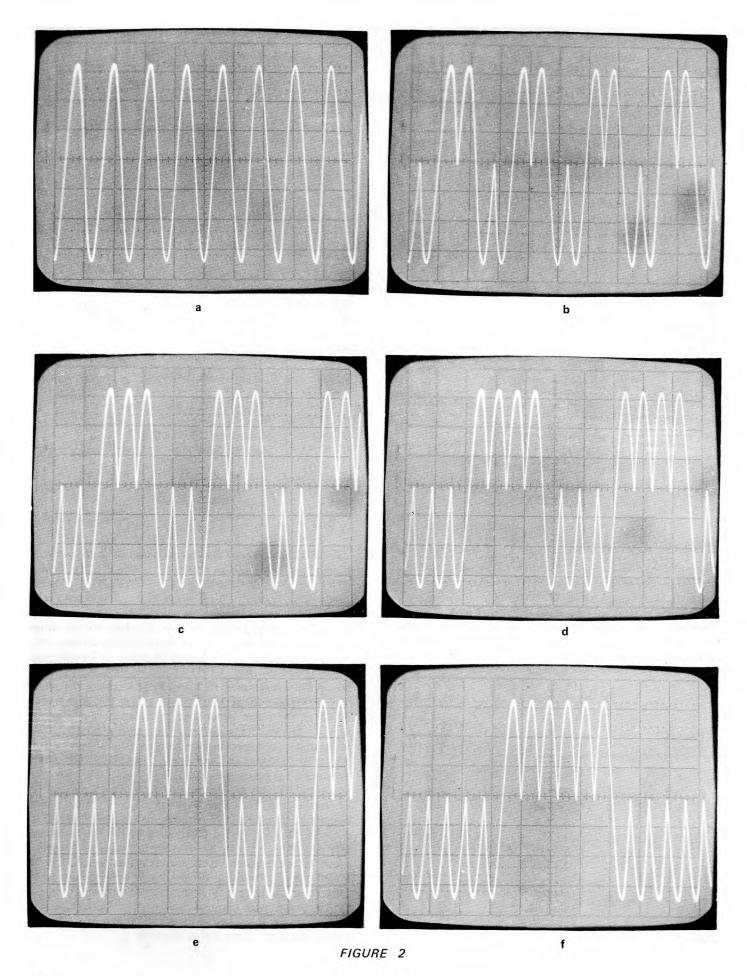

When the voltage across the capacitor,  $V_C$ , is increased by reducing the value of the potentiometer resistor, the trigger diode will break down earlier at ' $\alpha$ 2' and not ' $\alpha$ 1' as is shown in Figure 2 — hence the phase shift.

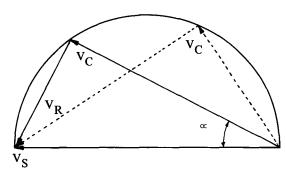

On the other hand, by varying the ratio of potentiometer 'R' to ' $1/\omega$ C', the phase shift is also obtained between the capacitor voltage 'VC' and the input voltage 'VS'. This phase shift is shown in Figure 3.

FIGURE 2

FIGURE 3

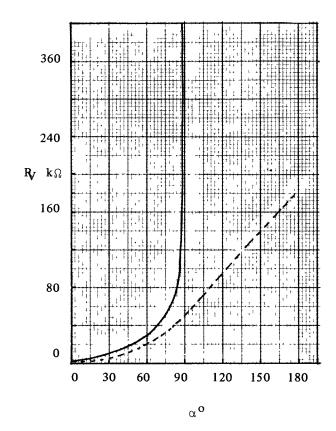

The actual phase shift as applied to the trigger diode will be, therefore, a combination of the two phase shifts discussed above. Figure 4 shows the phase shift caused by the variation of 'R/ $\omega$ C' only, (1/ $\omega$ C is assumed to be constant) and, also, the actual phase shift. The curves have been plotted for 240V a.c. input, 50Hz and 0.2 $\mu$ F capacitor. Figure 4 shows that control is possible from approximately 0° to 180° by using the circuit shown in Figure 1.

#### **Hysteresis Effect**

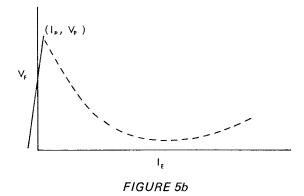

It was noticed, when using the circuit shown in Figure 1, that once the Triac has been turned 'on' at the minimum volts, the volts could be further reduced by increasing the potentiometer resistance. In other words, the striking voltage seemed to be higher than the turning 'off' voltage. This hysteresis type phenomenon is attributed to the trigger diode and it can be explained by examining Figure 5. The peak voltage across the capacitor,  $V_C$ , must be slightly higher than that of the breakdown voltage of the trigger diode or the Triac may never turn 'on' there being insufficient volts between terminals MT1 and MT2.

As soon as the trigger diode breaks down, part of the energy from the capacitor is transferred to the gate of the Triac. Figure 5 shows that the first breakdown occurs when the voltage across the capacitor reaches the forward breakdown voltage, giving a phase shift  $\beta_1$ . The triac will then turn 'on' and the capacitor, partly discharged, will charge again. Thus when the second and succeeding breakdowns occur at the reverse and forward breakdown voltages alternately, they will give a phase shift  $\beta_2$ . The steady state condition, therefore, will be established at  $\beta_2$ .

Once the firing point is set at  $\beta_2$ , it is then possible to reduce the load voltage by increasing the resistance of the potentiometer until the peak of the shifted,  $V_C$ , can be reached at the trigger diode breakdown line.

Phase shift due to  $R/_{1/_{\omega}C}$

Actual Phase Shift (excluding hysteresis effect)

FIGURE 4 Relation Between Delay Angle 'a' and Potentiometer Resistor

V<sub>C</sub> with trigger diode

FIGURE 5

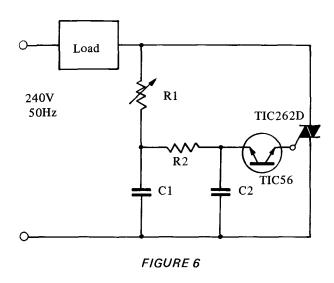

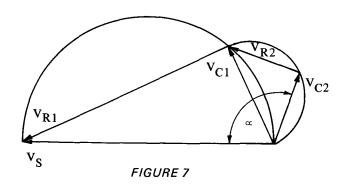

#### Double C/R Circuit

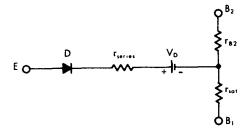

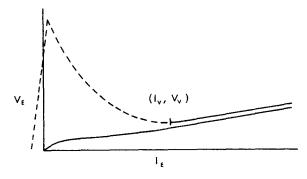

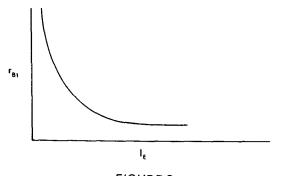

It is not always desirable to turn on the Triac with the voltage,  $V_C$ , around the peak value since any small variation in  $V_C$  could cause a large change in the delay angle ' $\alpha$ '. This problem can be eliminated by adding a second C/R network to that of the circuit shown in Figure 1. It is clear from Figure 6 that a further fixed delay is achieved at the gate of a Triac by adding resistor R2 and capacitor C2. This delay is shown in Figure 7.

It is possible for the trigger diode to breakdown during the fast rising section of the,  $V_{C2}$ , sine wave. The reduction of the hysteresis effect is a further advantage of using a double C/R circuit. After the trigger diode has turned 'on', the partly discharged capacitor, C2, is recharged by some of the energy from capacitor C1. This occurs during the time the Triac is conducting, hence the smaller phase shift and hysteresis.

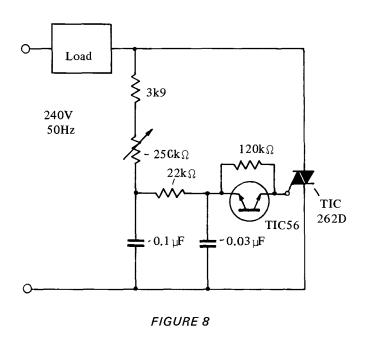

#### Choice of Circuit for Resistive Loads

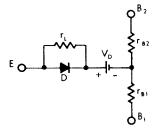

Figure 8 shows the circuit recommended for use with resistive loads. It is a cheap and simple circuit which gives adequate control in lamp dimming without flicker and with minimized hysteresis effect. The resistor, connected in series with the potentiometer, limits the maximum voltage applied to the capacitors. The resistor across the trigger diode ensures smooth control at all angles of delay.

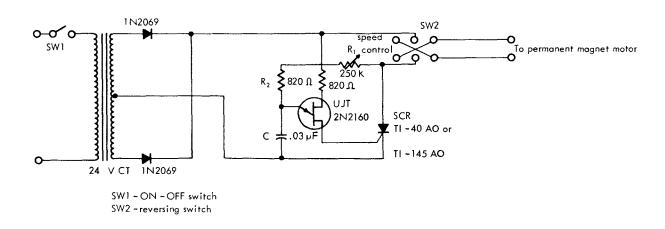

The 'load' in Figure 8 can be replaced by a single phase bridge with the D.C. outputs connected to a fractional H.P. D.C. motor. By adding a  $50\mu F$  capacitor in series with a  $4.7\Omega(5W)$  resistor across the armature, a smooth speed control of the D.C. motor can be obtained.

#### TRIACS WITH INDUCTIVE LOADS

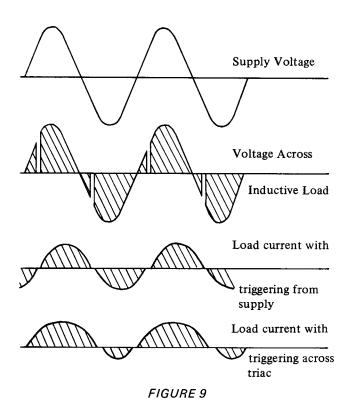

The circuit discussed in the previous paragraph cannot be used for controlling inductive loads. With the resistive loads (Figure 1) the current and voltage are in phase, hence the capacitor starts charging again at the time when the voltage reverses. Thus, the positive and negative half cycles will reach the trigger diode's breakdown voltage at the same time, resulting in symmetrical firing of the Triac. In the case of an inductive load, however, for a set value of the potentiometer, the current will still flow when the a.c. voltage reverses, causing the second half of the cycle to be delayed. This is because the capacitor will begin to recharge from the time when the current ceases to flow through the Triac. Figure 9 illustrates the positive and negative half cycles with inductive loads where triggering is directly from the supply and across the Triac.

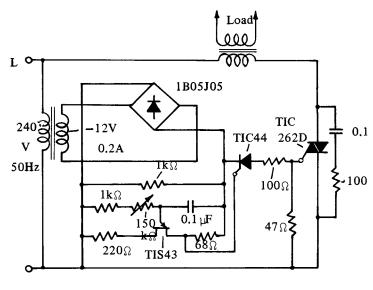

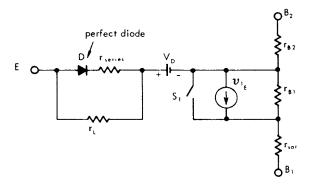

When the triggering is directly from the supply it provides one remedy for correcting the unbalance. Figure 10 shows the recommended circuit for controlling inductive loads of up to 6kW.

The low supply voltage to the triggering circuit (12V) means that it is necessary to replace the trigger diode by a unijunction transistor. The pulses generated by a basic unijunction transistor circuit cannot be used for direct gating of a Triac as they are of a very short duration and may disappear just before the Triac reaches the latching current. One way of extending these pulses is to use a 'slave Thyristor' through which the resistive current will flow.

FIGURE 10

The thyristor will then turn 'off' each time the full wave rectifier voltage reaches zero as shown in Figure 9. The normal precautions against dv/dt and di/dt are arranged as in Reference 1. The unbalanced current flowing through the transformer will become even more unbalanced due to the presence of D.C. component.

A very large unbalance in one direction would certainly destroy the Triac. The circuit shown in Figure 10 gives a reasonable balance between the positive and negative half cycles. A further improvement, if required, can be accomplished by connecting a resistor across the primary winding of the transformer.

#### CONCLUSIONS

This chapter shows two circuits which have proved to give satisfactory results. An inexpensive, reliable circuit for controlling lamp dimming without a flicker, and various types of resistive loads is shown in Figure 8. Inductive loads, especially transformers, always present some problems. The circuit shown in Figure 10, however, gives a satisfactory performance, with minimum unbalance (D.C. component) between a positive and negative half cycle.

#### REFERENCES

- 1. Chapter 1.

- 2. G.E. SCR Manual, Fourth Edition.

### III SOLID-STATE SWITCHING USING TRIACS AND THYRISTORS

#### By Jurek Budek

#### INTRODUCTION

Mechanical contactors and relays, having moving parts, are subject to wear and tear and require periodic maintenance. There are cases when frequent switching operations are needed; for instance, controlling a fresh water supply by switching on and off electric pumps, controlling electric heaters, solenoids, etc. In addition to the cost of the maintenance of contactors, the inconvenience caused by the interruption of work, especially in nonattended stations, is another factor that has to be considered.

A triac, used as a semiconductor switch, has features which overcome these difficulties and is ideally suited for frequent operation. It is small and reliable. It turns on when a gate pulse is applied and in a.c. circuits switches off each time the current passes through zero. It requires a very small gate power to control the main (principal) current. It must be remembered, however, that by using a solid-state contactor, complete isolation is not possible. In fact a triac inserts in the circuit a very high impedance when in off state, turning this impedance to a very low value in the on position. For complete electrical isolation an off load switch is recommended.

This chapter is concerned mainly with single-phase switching circuits, but some 3-phase and d.c. static contactors are discussed.

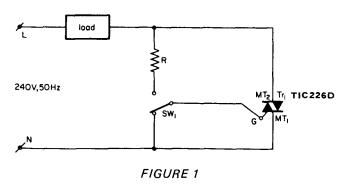

#### SIMPLE TRIAC SWITCH

The gate drive circuit may consist simply of a resistor and a switch, connected as shown in Fig 1. Gate current is positive when MT<sub>2</sub> is positive, and negative when MT<sub>2</sub> is negative. The triac will turn off each time the principal current drops to zero.

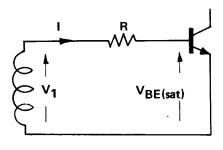

The resistor R limits the gate current to the desired value. Assuming the worst condition when the triac is turned on at the peak supply voltage V, the resistor R, must be

#### $R > \sqrt{2/I_{GM}}$

where  $I_{GM}$  is the permissible maximum peak gate current. If R is made too large, the triac will not trigger at the beginning of each cycle, resulting in the loss of some of the output voltage. The recommended resistor R is  $120\Omega$ . The toggle switch can be replaced by a reed relay or pilot thermostat contacts, thus eliminating the wear of contacts associated with breaking high currents.

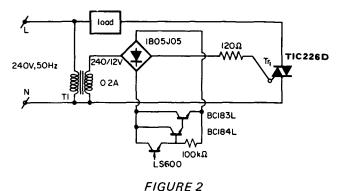

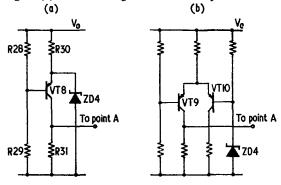

#### TRIAC SWITCH OPERATED BY A LIGHT SOURCE

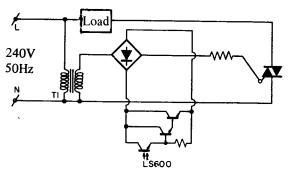

A light-sensing device can be utilised in controlling the operation of a triac. A circuit, shown in Fig 2, could be used for applications such as burglar alarms, automatic opening of doors, switching motors, etc.

The light-sensor amplifier comprises a high-gain Darlington pair with collector and emitter terminals connected across a single-phase bridge. When the light falls on and activates the LS600 light sensor, a voltage is developed across the  $100k\Omega$  resistor which turns on the Darlington pair. This in turn shorts out the bridge and fires the Triac. By changing over the positions of the light sensor and  $100k\Omega$  resistor, the operation can be reversed.

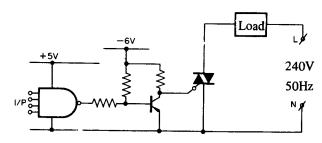

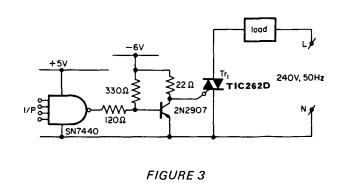

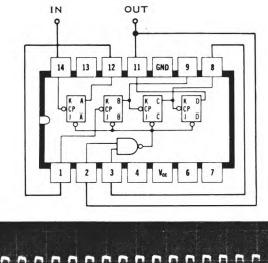

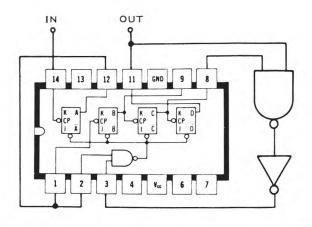

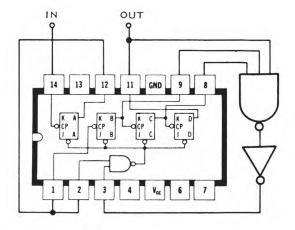

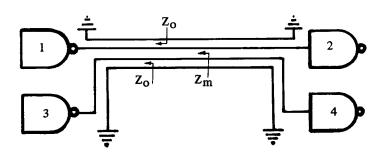

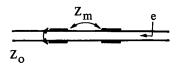

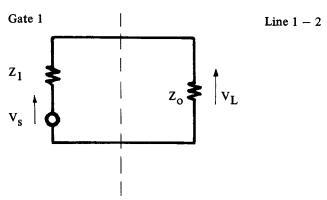

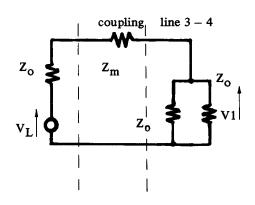

## TRIAC SWITCH OPERATED BY A LOGIC NAND CIRCUIT

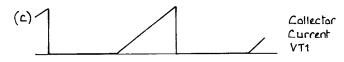

An integrated logic circuit may be used to control the triac; Fig. 3 shows an example of this.

The NAND gate controls the state of a pnp transistor which, in turn, controls the gate current to the triac. When all inputs to the NAND gate are at a positive level, the pnp transistor is turned on; the gate is now brought down to almost neutral potential of the supply through the saturated pnp device. If any input to the NAND gate decreases to a low level, the pnp device turns off, and turn on gate current flows from the triac. In this circuit the components have been chosen to give sufficiently large gate power to turn on a 25A r.m.s. Triac. It should be noted that the neutral of supply is not at the earth potential.

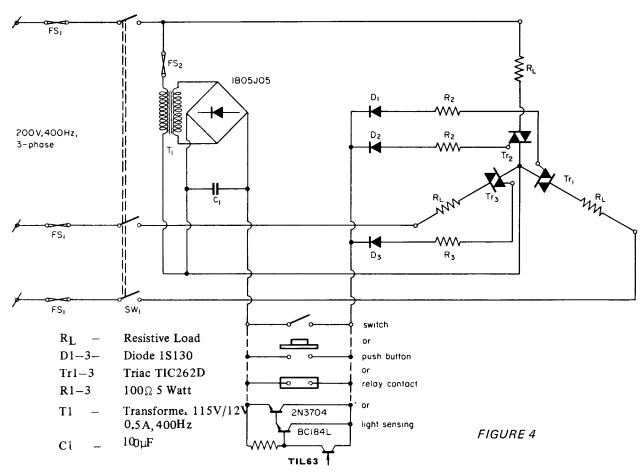

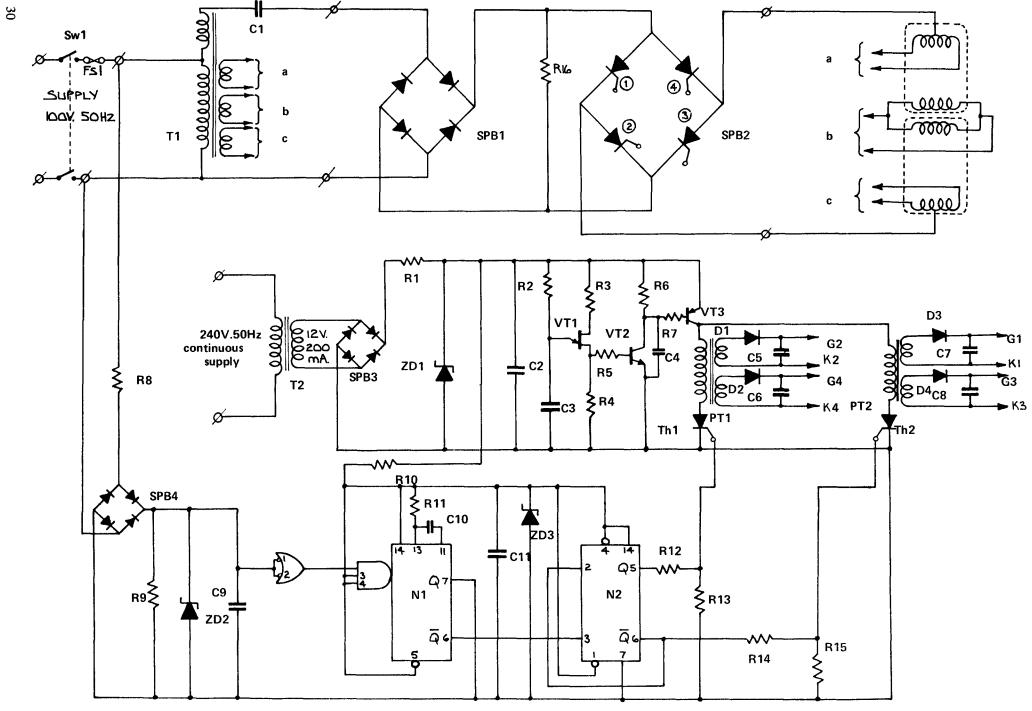

#### SWITCHING 3-PHASE LOADS WITH A TRIAC

Switching on and off 3-phase inductive or resistive loads can be achieved by controlling power to the gates of triacs as shown in Fig. 4. Three resistive loads RL are connected in star via three triacs  $Tr_1$ ,  $Tr_2$ , and  $Tr_3$ . The supply to the gates is arranged through  $100\Omega$  resistors  $R_{1/3}$  and blocking diodes  $D_{1/3}$ . As shown in Fig. 4, the load can be controlled either by a toggle switch, a pushbutton, a relay contact or light sensing. For complete isolation, a switch  $S_1$  has been added and fuses  $F_2$  and  $F_1$  are also included to protect the main circuit and auxiliaries against a fault.

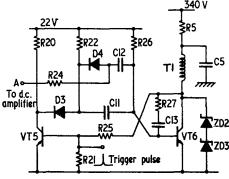

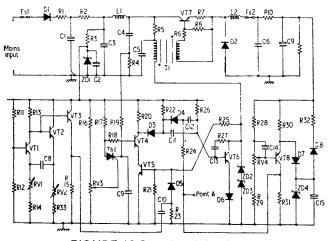

and looking from the input side E-S represents impedance only. The sensing bridge, consisting of resistors  $R_3,\,R_4,\,R_5$  and potentiometer  $RV_1$  is balanced for E-S higher than 1 to  $8M\Omega$  adjusted by  $RV_1.$  The output of the sensing bridge is injected into the f.e.t. differential amplifier (VT  $_1$  and VT  $_2$ ) and then to the modified Schmitt-trigger circuit consisting of VT $_4$  and VT $_5$  transistors. When the transistor VT $_6$  is on the voltage developed across  $R_{19}$  will turn on transistor VT $_7$  and hence the single-phase bridge SPB $_2$  will be shorted out, completing primary connection to the transformer T $_3$ .

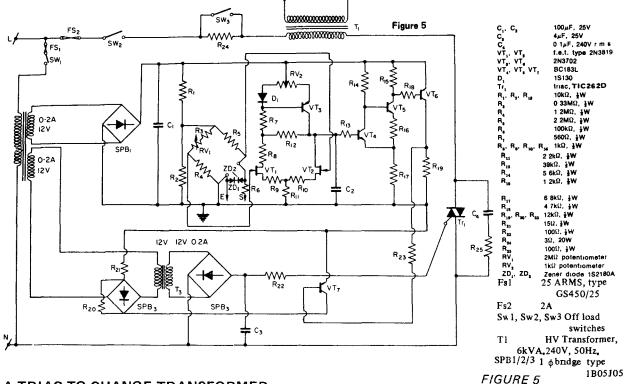

#### TRIGGERING TRIACS FROM A VERY-HIGH-IMPEDANCE SOURCE

It is sometimes necessary to control loads from a very-high-impedance source. As an example, a circuit is given in Fig. 5 which could be used in plastic welding equipments as a protection against flashover. The impedance of the plastic material, during normal welding, may be of many thousand megohms. As the plastic is not always perfect, a pinhole or unevenness could reduce this impedance to a very low level, possibly 1 or 2 M $\Omega$ . As a result there could be flashover and arcing. This, of course, in undesirable. The flashover may damage the welding electrodes and, if the welding was on plastic bags containing liquid, puncturing and thus some splashing could occur.

In order to prevent the flashover, a triac could be used as a solid-state contactor, being turned off when the impedance between electrodes is reduced to a few megohms and thus cutting off the supply to the h.v. transformer just before the breakdown voltage is reached.

Referring to Fig. 5, the sensing arm of the balanced bridge is connected to the welding electrodes; E to the earthed electrode and S to the live one. The high-voltage high-frequency across electrodes has been filtered out externally

The d.c. current, limited by resistor R<sub>22</sub>, will now flow through the gate and terminal MT<sub>1</sub> of true Tr<sub>1</sub>.

Capacitor C<sub>2</sub> ensures that the triac is either in on or off state and eliminates unbalanced phase control which is undesirable in inductive loads<sup>1</sup>. The purpose of transformer T<sub>3</sub> is to isolate the earthed electrode E from the neutral of the supply N. An f.e.t. differential amplifier is being used because of the high impedances involved in the sensing bridge. Back to back zener diodes ZD<sub>1</sub> and ZD<sub>2</sub> protect the f.e.t differential amplifier against excessive voltage transients generated during arcing while adjusting potentiometer RV<sub>1</sub>.

The protection against excessive dV/dt is arranged by connecting resistor R25 in series with capacitor C4 across the triac<sup>2</sup>.

The user normally provides an inrush current limiting resistor R<sub>24</sub> which is short time rated and is shorted out as soon as the steady-state conditions are obtained. The triac protective fuse F<sub>2</sub> can be then rated closely to the nominal current.

The circuit shown in Fig. 5 suggests a means of triggering triac from a very high impedance source. By redesigning the sensing bridge, the usage of this circuit can be extended.

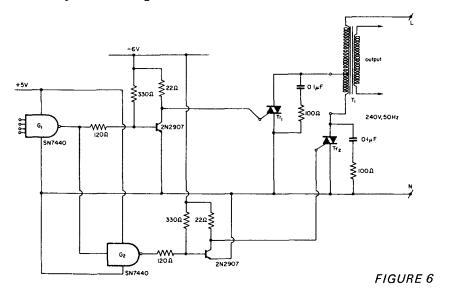

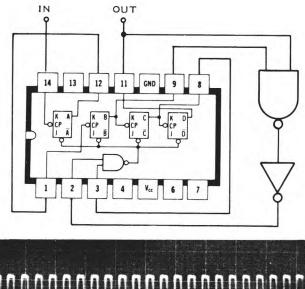

## USING A TRIAC TO CHANGE TRANSFORMER TAPS

Triacs can be used in place of mechanical contactors to change the tappings of a transformer. Care must be taken, however, to eliminate the possibility of triggering both triacs at the same time, as, in such cases, a short circuit current will flow in the winding shorted out by both triacs.

Fig. 6 shows a circuit consisting of two triacs controlling two tappings of a transformer. Both triacs are triggered by a logic NAND circuit. The operation of the circuit is similar to that described earlier. When all inputs to the NAND gate are at a positive level, triac  $Tr_2$  is on giving a lower voltage from transformer  $T_1$ .

If any input to the NAND gate decreases to a low level, triac  $Tr_1$  is turned on giving higher voltage output from the transformer. Both i.c. circuits  $G_1$  and  $G_2$  are mounted on the same chip with  $G_2$  inverting the output signal from  $G_1$  so that at any time when triac  $Tr_1$  is on triac  $Tr_2$  is off, or

vice versa. By switching off -6V supply, both triacs will turn off.

There is no danger here that the triacs  $Tr_1$  and  $Tr_2$  may short out part of the winding when changing the state from on to off, as the switching over is made with triacs conducting the current in the same direction. Similar protection will be needed against transformer in-rush current as discussed on page 18. When the current and voltage permit the above circuit can be adopted for the secondary windings of the transformer. An advantage would be that there are no transformer in-rush current problems.

## LIGHT SENSOR/THYRISTOR CONTROL OF D.C. TOY MOTOR

The gate has no control over its thyristor once anode to cathode current is flowing. In D.C. circuits, therefore, the current through the thyristor can be interrupted only by a mechanical switch connected either in series or across the thyristor, or, by forced commutation as used in inverter circuits. However, small thyristors can be switched 'off' by reverse biassing the gate. This method should be applied with caution as far as the gate to cathode reverse voltage is concerned. With increasing areas of the thyristor junction, i.e. for larger devices, negative gate bias has less effect.

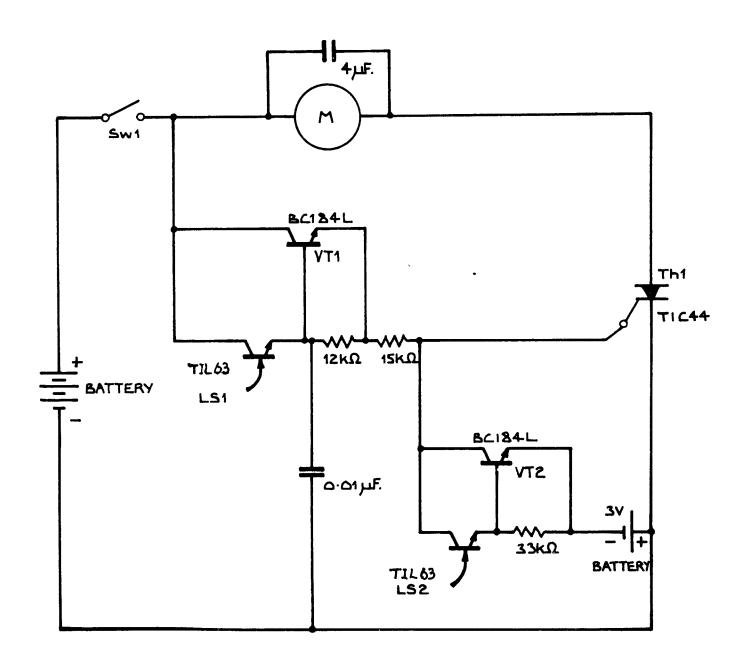

Figure 7 gives a circuit suitable for switching 'on' and 'off' a small D.C. Toy Motor by means of a thyristor.

On shining the light from a torch on the light sensing device 'LS1' transistor VT1 will turn 'on' and the gate current will flow through thyristor, switching 'on' the supply to the motor. By diverting the light beam from 'LS1' device to 'LS2', transistor VT2, will turn 'on' and apply reverse voltage to the gate of thyristor Th 1. The latter will turn 'off' and hence the supply to the toy motor will also be switched 'off'.

The above circuit can have various applications, especially in the toy manufacturing industry. An example might be walking dolls. The eyes of a doll could be replaced by light sensing devices. By shining the light in one eye of a doll, the doll will move, and by diverting the light beam from a torch to the other eye of the doll will stop moving.

FIGURE 7

#### SWITCHING d.c. SOLENOIDS BY THYRISTORS

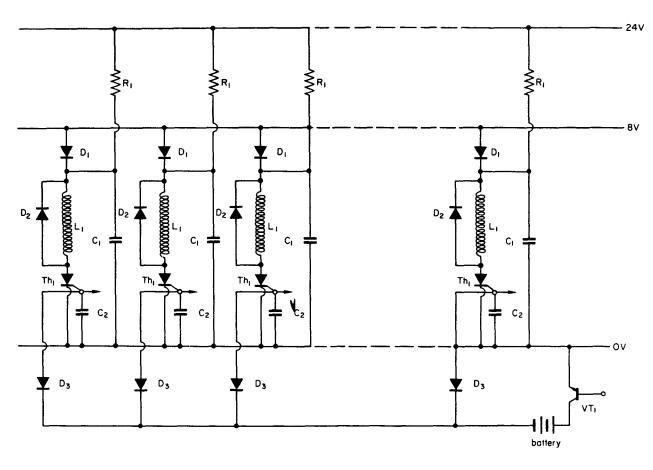

Additionally, a thyristor can be switched off in d.c. circuits by applying a reverse voltage to the gate. Fig. 8 shows a circuit with an array of solenoids  $L_1$  being controlled individually by applying signals to the thyristors  $Th_1$  gates.

All the solenoids are switched off by a signal applied to the base of transistor  $VT_1$ . This circuit required two d.c. supplies, 24V and 8V. The capacitor  $C_1$  is charged to 24V and its energy is used to give an extra boost to the solenoid at the time of switching on. As soon as the solenoid is energised its holding current is taken, then from a 8V d.c. supply. Diode  $D_1$  ensures that the capacitor  $C_1$  is charged to 24V at the time when thyristor  $Th_1$  is off. Diode  $D_3$  is a blocking diode, preventing interaction between the gates of thyristors. Diode  $D_2$  discharges energy stored in the solenoid at the time when thyristor  $Th_1$  is switched off.

FIGURE 8

#### **CONCLUSIONS**

There is a large variety of circuits where triacs and thyristors could be used as solid state switches. The circuits discussed in this chapter offer some ideas on the use of solid state contactors. The operation of contactors by a logic, light beam and switching is discussed together with some of the problems encountered.

There are two points which it will be useful to remember, when designing a solid state contactor:—

- (a) The neutral of the supply voltage is not at the EARTH potential.

- (b) The triac gate pulses should have the same polarity as the main triac voltage or alternately the gate should be always negative with respect to the MT1 terminal for either main voltage polarity.

#### REFERENCES

- 1. Chapter II

- 2. Chapter I

- 3. S.C.R. Manual, G.E. Fourth Edition

#### IV BURST FIRING TECHNIQUES USING TRIACS

#### By Jurek Budek

#### INTRODUCTION

Thyristors and Triacs used in a phase control mode produce considerable radio frequency interference (r.f.i.) due to the step change in current. A solution to the problem of suppression becomes more difficult and expensive as the load increases. In domestic appliances, particularly, the r.f.i. is acute and must be suppressed according to B.S. specification 800. For domestic use phase controllable power up to 500 Watts may be acceptable. However, above this value the ratio between the phase controllable power to the total consumed power becomes significant and in addition to the expensive suppression circuit, the power factor may cause some concern to the Electricity Board.

Electric heaters and other loads with a long time constant may be controlled by passing through them a selected number of full or half cycles. The current, then will be in phase with the voltage and there will be no problem of r.f.i., the switching taking place at the point when the voltage crosses zero. Such control is called Burst Firing or Zero Voltage Switching. Burst firing is not suitable for lamp dimming due to the flicker, or for Motor Speed Control and transformer input control.

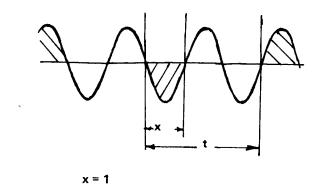

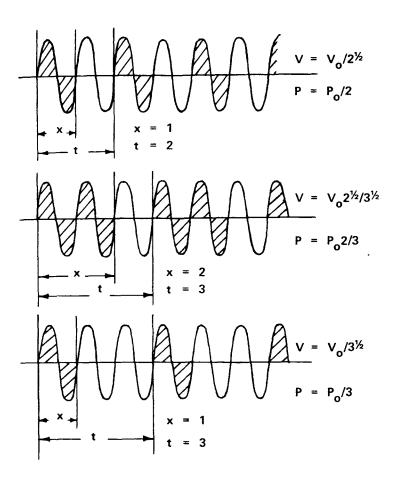

This chapter discusses two circuits. Power control can be achieved by blocking individual half cycles in an established pattern, or by passing a selected number of cycles in a mark-space mode.

#### **VOLTAGE AND POWER**

A simple substitution in the following equation gives the value of output r.m.s. voltage, V.

where

V<sub>O</sub> - maximum r.m.s. output voltage (uncontrolled)

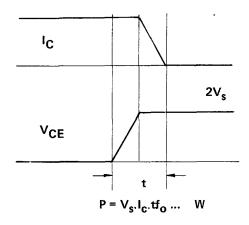

t - period expressed in number of half cycles

x - number of conducting half cycles

As an example: -

FIGURE 1

$$V = (V_o^2/3)^{1/2} = V_o/3^{1/2}$$

t = 3

and the output power (Resistive load), P:-

$$P = P_0 \cdot x/t$$

where

P<sub>O</sub> - maximum output power \*uncontrolled)

$P = P_0/3$

If the control is in full cycles, t will represent the period

consisting of the number of full cycles and x will give the number of full conducting cycles, as shown in Figure 2.

FIGURE 2

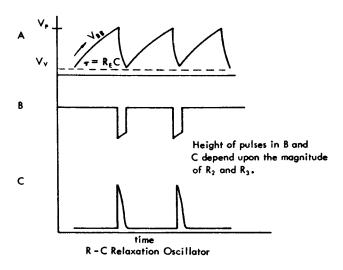

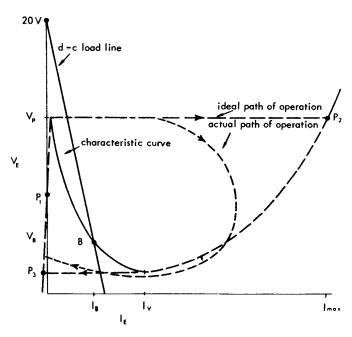

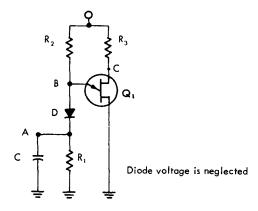

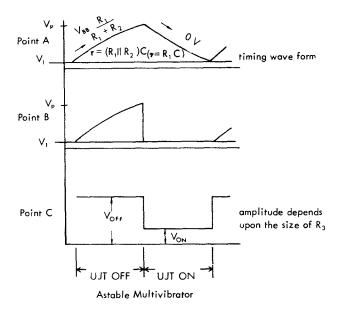

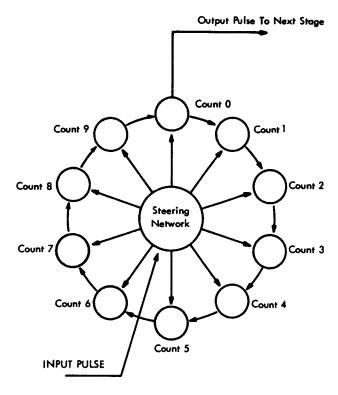

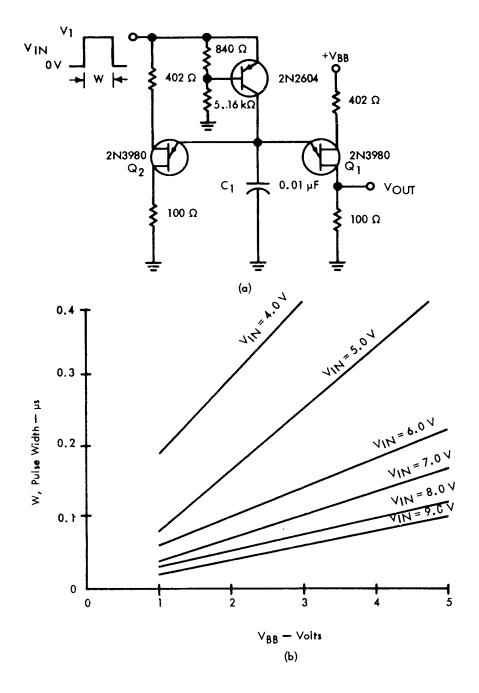

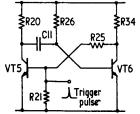

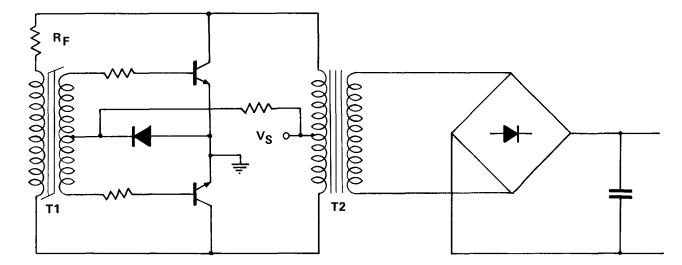

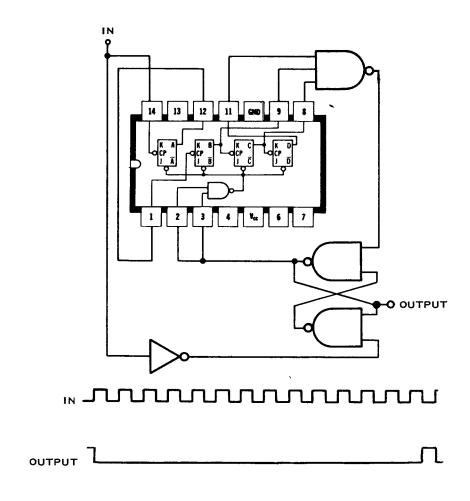

#### **BURST FIRING USING A TRANSISTOR PUMP**

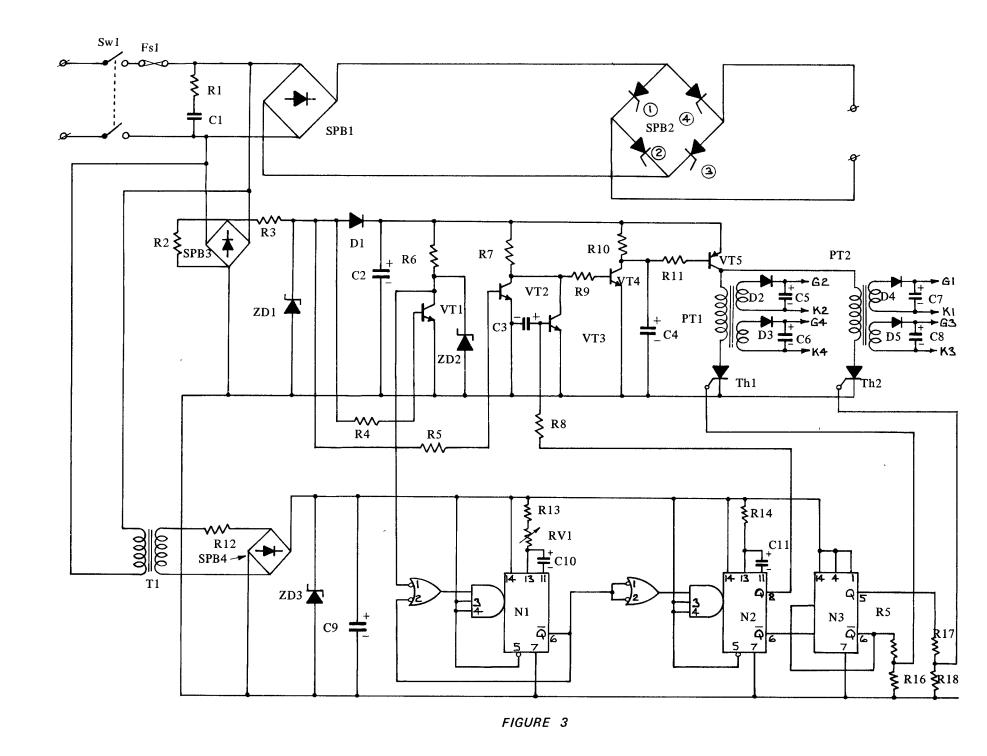

The circuit shown in Figure 3 provides Burst Firing controlled in steps of half cycles down to one firing in fifteen half cycles. Table 1 shows the power reduction for this type of control with 1 half cycle conduction.

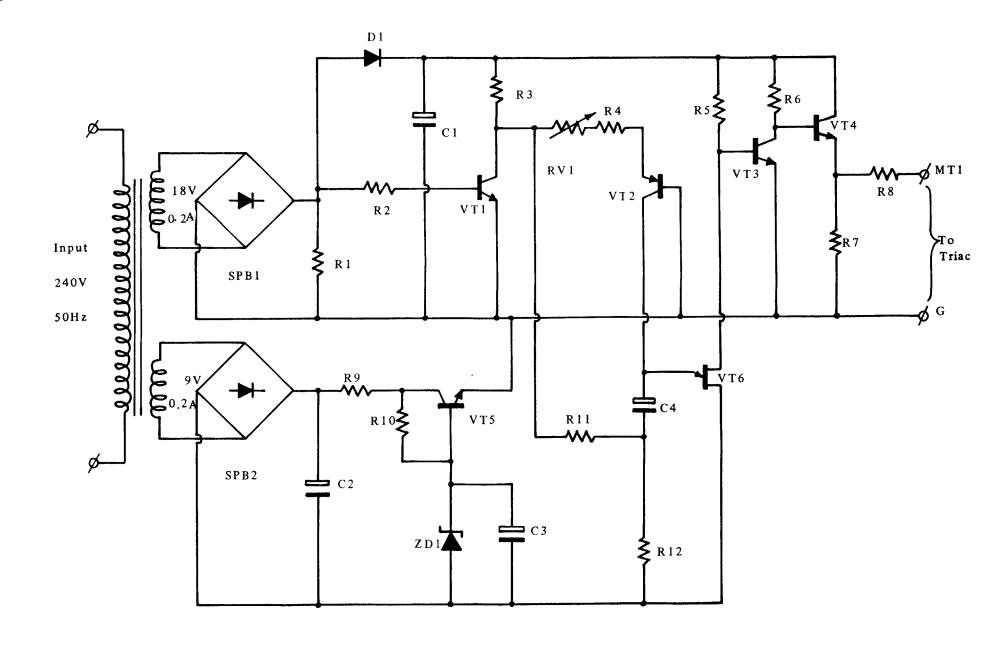

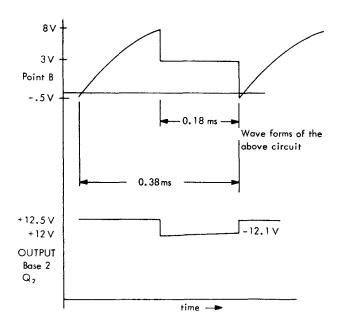

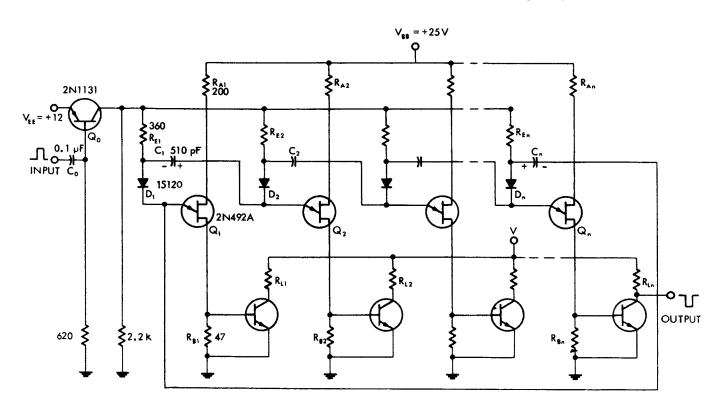

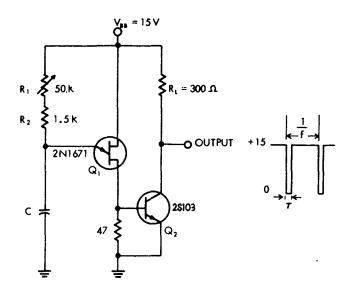

The positive DC supply is derived from an 18V winding of transformer T1 (Figure 3) via a single phase bridge rectifier, SPB1, diode D1 and the 100µF smoothing capacitor C1. Diode D1 is included in order to obtain unsmoothed full wave rectified voltage at the positive terminal of the bridge for the porpose of pulse generation. The negative supply is similarly generated from a 9V winding of transformer T1. A series stabilizing transistor, VT5, and zener diode, ZD1, provide a smoothed constant voltage reference necessary for accurate firing of the unijunction transistor, VT6.

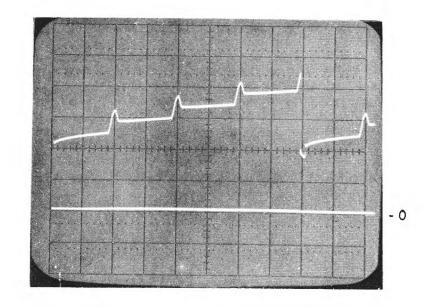

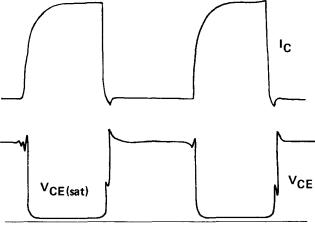

The full wave unsmoothed voltage is applied to the base of transistor VT1 which acts as a pulse generator. At the collector of VT1, the positive pulses appear each time the base voltage drops to zero, and hence synchronize with the mains at the time when the supply voltage is virtually zero. Then the pulses from the collector of transistor VT1 are fed via the potentiometer RV1 and fixed resistor R4 to the emitter of transistor VT2 which works as a transistor pump. Capacitor C4 is charged with constant current pulses giving voltage steps of equal increments, as shown in Figure 4.

When the increments of step voltage between emitter and base 1 reach approximately 4.5V the unijunction will fire, pulling down the base voltage of transistor VT3, thus turning it off. Capacitor C4 will discharge through the emitter of the unijunction and resistor R12 until insufficient current can be supplied into the emitter to keep it conducting. The unijunction then switches off the voltage at the base of transistor VT3, rises, and the latter turns on.

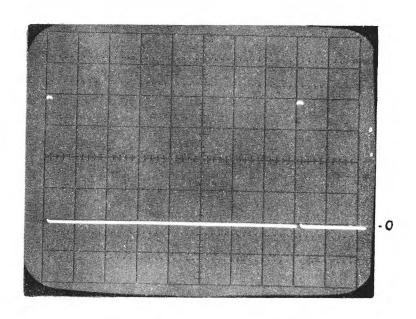

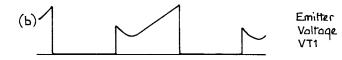

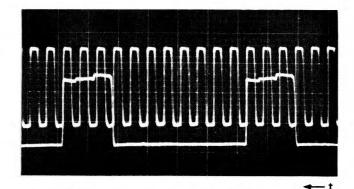

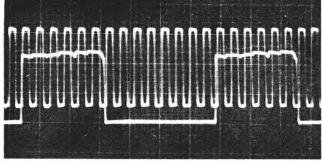

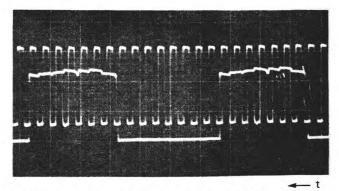

Transistor VT4 acts as an emitter follower and provides sufficient current to drive a T1 25 A r.m.s. Triac. Therefore positive pulses will appear between the Triac's main terminal MT1 and gate, G, each time the unijunction transistor fires (See Figure 5).

FIGURE 3

Transistor pump

V<sub>BE</sub> of VT6

1V/cm †

5ms/cm \_\_\_

FIGURE 4

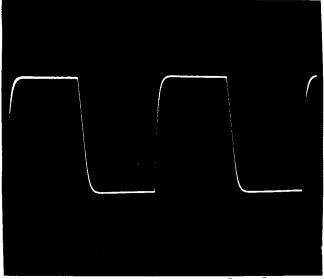

Output and pulses

(MT1 - G)

5V/cm

5 ms/cm \_\_\_

FIGURE 5

TABLE 1

| Total No. of half cycles | 1   | 2  | 3  | 4  | 5  | 6    | 7    | 8    | 9    | 10 | 11  | 12  | 13  | 14  | 15  |

|--------------------------|-----|----|----|----|----|------|------|------|------|----|-----|-----|-----|-----|-----|

| % Power<br>Output        | 100 | 50 | 33 | 25 | 20 | 16.7 | 14.3 | 12.5 | 11.1 | 10 | 9.1 | 8.4 | 7.7 | 7.1 | 6.7 |

By adjusting the value of resistor, R12, the unijunction's 'on' time is made sufficiently long enough to ensure that the width of the output pulses are at least  $500\mu$ s for any point of control.

Figure 4 shows that the voltage across the capacitor C4 rises in approximate linear steps (with a slope of about 0.2V per step). If the unijunction were fired at some point along the linear step instead of at the beginning of the step (quite possible with unijunction transistors), indeterminate firing would occur resulting in unwanted phase control. The potential divider chain R11 and R12 is introduced to provide, at the beginning of each step. a narrow pulse, whose magnitude is small but greater than the slope, to ensure that the unijunction can fire only at this time.

If the output pulses need to be slightly delayed to ensure correct Triac firing, a O.1µF capacitor can be added between the base and emitter of transistor VT3.

In this circuit the power varies in steps of 100%, 50%, 33% and smaller decrements down to zero. The control step pattern can be rearranged so that the smaller steps are around 100% of full power and the larger jumps at the lower end. This can be achieved by the addition of an npn transistor, three resistors and a capacitor to the circuit shown in Figure 3.

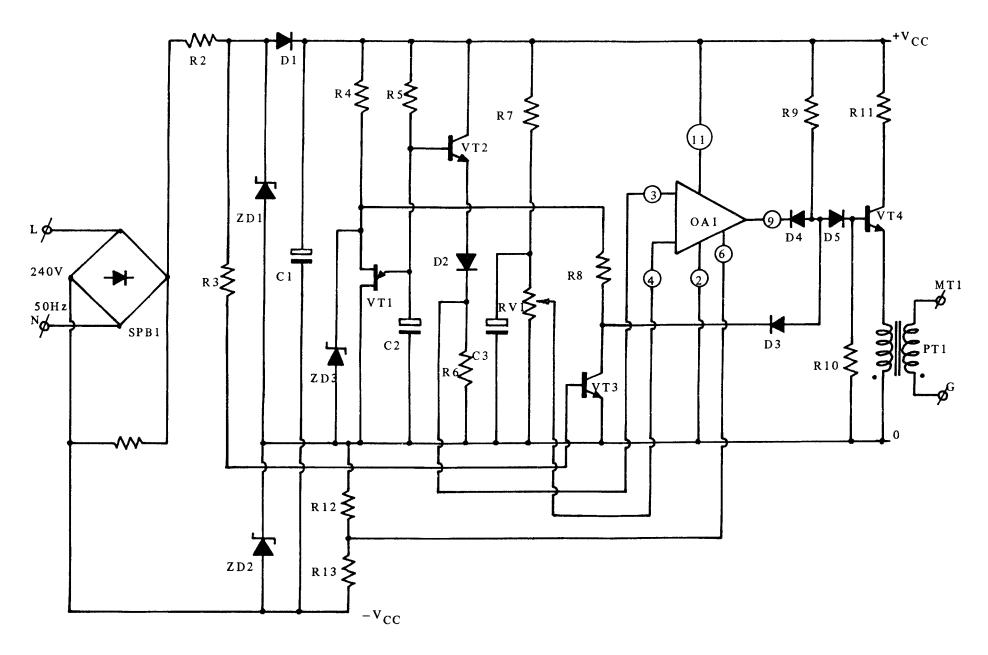

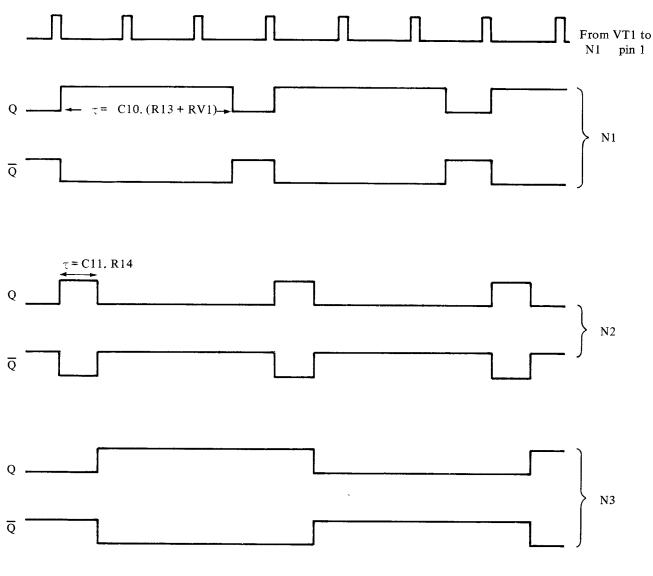

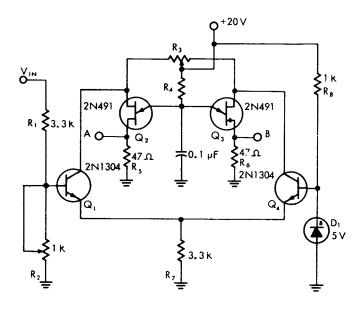

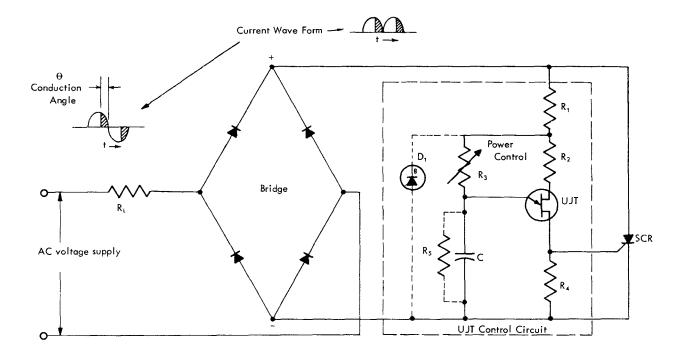

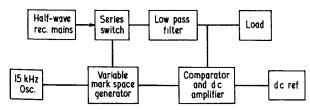

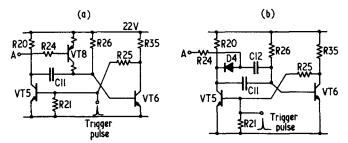

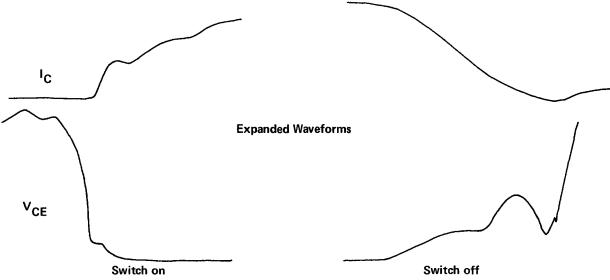

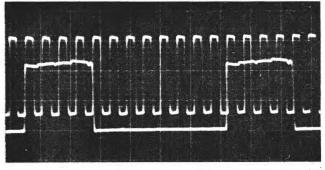

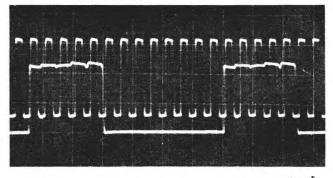

#### BURST FIRING BY MARK SPACE CONTROL

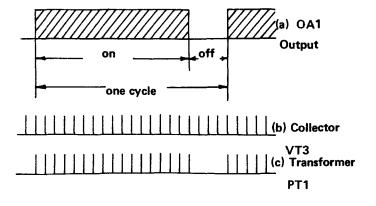

The circuit is shown in Figure 6. Bridge SPB1 provides full wave rectification and an input to the two zener diodes ZD1 and ZD2, for a constant voltage supply of 12V (+V<sub>CC</sub>) and 7.5V (-V<sub>CC</sub>). Using the unijunction transistor, VT1 a sawtooth waveform is generated with a frequency of about 1 second period determined by resistor R5 and capacitor C2. Transistor VT2 brings the sawtooth voltage down so that its optimum value is below one volt, thus offering better control when working in conjunction with the differential amplifier 'OA1'. The pulses at zero voltage crossing points are generated by transistor VT3, whose base is connected to the unsmoothed supply across zener diode ZD1. The base voltage drops to virtually zero each time the mains voltage crosses zero turning the transistor 'off' and providing positive pulses at its collector.

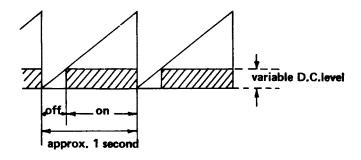

The sawtooth is then injected to the differential comparator OA1 — non inverting pin (3), and a DC voltage level control from the potentiometer RV1 is connected to the inverting pin (4). The output (pin 9) will give a mark-space control by varying the DC level as shown in Figure 7.

FIGURE 7

As the differential comparator is very sensitive to the input voltage, a  $100\mu F$  capacitor, C3, has been added across potentiometer RV1 in order to obtain a satisfactory mark-space waveform, without intermittent switching when in the 'ON' position. The differential comparator needs two supply voltages, a +12V and a -6V; the latter being taken from a resistor chain R12 and R13.

The output from the differential comparator and the train of pulses at zero voltage crossing points from the collector of transistor VT3 are applied to an 'AND' circuit consisting of diodes D3 and D4 and transistor VT4. When both the cathodes of D3 and D4 are at a positive level, pulses will appear in the output of transformer PT1. (This transformer is included to give gate isolation protection for the Triac). There will be no pulses if either or both cathodes of diodes D3 and D4 are at zero level, as shown in Figure 8. Therefore pulses at zero voltage crossing are controlled by the mark-space-mode covering one half cycle in one second (i.e. 1%) to 100%.

FIGURE 6

| C1, C2        | $100 \mu F$ , $25 V$  |

|---------------|-----------------------|

| C3, C4        | 4 μF, 25V             |

| D1            | 1N4001                |

| SPB1, SPB2    | 1B05J05               |

| ZD1           | 1S2075A               |

| VT1, VT3, VT5 | BC183L                |

| VT2           | 2N3702                |

| VT4           | 2N3704                |

| VT6           | 2N2160                |

| R1            | 1.5k Ω, ½W            |

| R2            | 12k Ω ½W              |

| R3            | 470 <sup>Ω</sup> , ½W |

| R4            | 680 Ω, ½W             |

| R5            | 8.2k Ω, ½W            |

| R6            | 1.2k Ω, ½W            |

| R7            | 1k Ω, ½W              |

| R8            | 100 Ω ½W              |

| <b>R</b> 9    | 330 Ω ½W              |

| R10           | 3.3k Ω, ½W            |

| R11           | 6.8k Ω ½W             |

| R12           | 120 Ω ½W              |

| RV1           | 100k Ω, ½W            |

|               | Potentiometer         |

| T1            | 240V/18V, 0.2A;       |

|               | 9V, 0.2A trans-       |

|               | former                |

|               |                       |

FIGURE 8

| C1, C3     | 100 μF, 25V                        |

|------------|------------------------------------|

| C2         | 5μF, 25V                           |

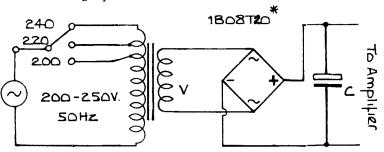

| SPB1       | 1B08T40                            |

| ZD1        | 12V, zener diode, IW               |

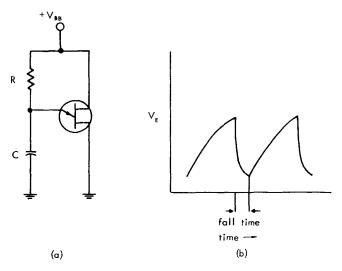

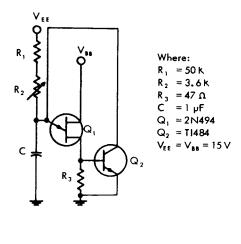

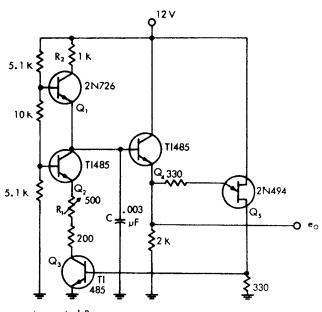

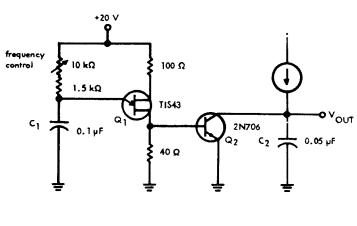

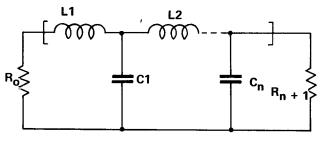

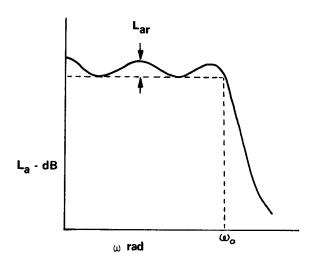

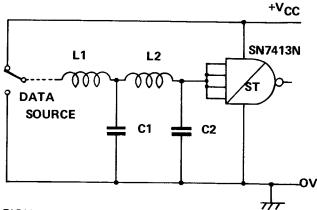

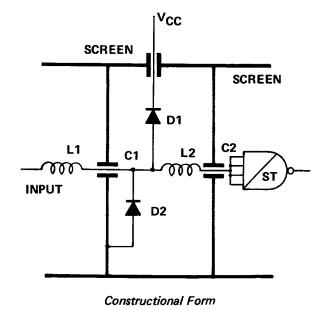

|            | 1S3012A                            |