Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This Acrobat document was generated by me, Colin Hinson, from a document held by me. I requested permission to publish this from Texas Instruments (twice) but received no reply. It is presented here (for free) and this pdf version of the document is my copyright in much the same way as a photograph would be. If you believe the document to be under other copyright, please contact me.

The document should have been downloaded from my website <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<a href="https://blunham.com/Radar">https://blunham.com/Radar</a>). Please do not point them at the file itself as it may move or the site may be updated.

It should be noted that most of the pages are identifiable as having been processed by me.

\_\_\_\_\_

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you personally – I know that I would have liked to have found some of these files years ago – they would have saved me a lot of time!

Colin Hinson

In the village of Blunham, Bedfordshire.

# TMS 9995 MICROPROCESSOR SYSTEM EMULATOR (9995 SE) SPECIFICATION

PRELIMINARY: 6/13/80

REVISION 1: 2/14/81

REVISION 2: 6/12/81

Prepared by:

John Schabowski, Microprocessor Systems Engineer

# TABLE OF CONTENTS

| T | I | T | L | E |

|---|---|---|---|---|

| _ | _ |   | _ |   |

# SHEET NO.

| 1.0                | SCOPE                                                                                                           |

|--------------------|-----------------------------------------------------------------------------------------------------------------|

| 1.1                | Description                                                                                                     |

| 1.2                | Characteristics                                                                                                 |

| 2.0                | ARCHITECTURE                                                                                                    |

| 2.1                | memory allocation                                                                                               |

| 2.2<br>2.2.1       | Organization<br>Arithmetic Logic Unit -                                                                         |

| 2.2.2.             | Internal Registers                                                                                              |

| 2.2.2.1            | Program Counter                                                                                                 |

| 2.2.2.2            | Status Register                                                                                                 |

| 2.2.2.3            | Workspace                                                                                                       |

|                    | Workspace Pointer                                                                                               |

|                    | Context Switching                                                                                               |

| 2.3                | Interfaces                                                                                                      |

| 2.3.1              | Memory Interface<br>Memory Read Operations                                                                      |

| 2.3.1.1            | Memory Read Oferations                                                                                          |

| 2.3.1.2            | memory Write Operations                                                                                         |

| 2.3.1.3            | Direct Memory access                                                                                            |

| 2.3.2<br>2.3.2.1   | Interrupts.                                                                                                     |

| 1.5.2.1            | External Interrupt Requests                                                                                     |

|                    | Interrupt Level O (RESET)<br>Mon-maskable of nterrupt (NMI)                                                     |

|                    | Interrupt Levels 1 through 15                                                                                   |

| 2.3.2.2            | Internally Generated Interrupts                                                                                 |

|                    | Interrupt Levels 1 through 15<br>Internally Generated Interrupts<br>Macro Instruction Detection (MID) Interrupt |

|                    | arithmetic overflow anterrupt                                                                                   |

| 2.3.3              | Communication Register Unit I reterface                                                                         |

| 2.3.3.1            | Single Bit CRU Operations                                                                                       |

| 2.3.3.2            | multiple Bit CRU operations                                                                                     |

| 2.3.4              | Nait State Generation                                                                                           |

| 2.3.5              | External Instructions                                                                                           |

| 2.3.6              | Internal ALU/Other Operation Cycles<br>Special Signals                                                          |

| 2.3.7              | Affilial Signature                                                                                              |

| 2.3.7.1<br>2.3.7.2 | DESTURITE of Long                                                                                               |

| 2.3.7.3            | 99955E/9990-Signal DESTWRITE Signal FREEZE-Signal                                                               |

| 2.3.7.4            | IACK Signal                                                                                                     |

| 2.3.7.5            | MID Signal                                                                                                      |

| - •                |                                                                                                                 |

# TABLE OF CONTENTS (CONT.)

TITLE SHEET NO.

| 3.0 | THEV. | yyyy instr        | RUCTION SET                                         |

|-----|-------|-------------------|-----------------------------------------------------|

|     | 3.1   |                   | on                                                  |

|     | 3.2   |                   | ng Modes                                            |

|     |       | 3.2.1             | Workspace Register Addressing                       |

|     |       | 3.2.2             | Workspace Register Indirect Addressing              |

|     |       | 3.2.3             | Workspace Register Indirect Auto Increment          |

|     |       |                   | Addressing                                          |

|     |       | 3.2.4             | Symbolic (Direct) Addressing                        |

|     |       | 3.2.5             | Indexed Addressing                                  |

|     |       | 3.2.6             | Immediate Addressing                                |

|     |       | 3.2.7             | Program Counter Relative Addressing                 |

|     |       | 3.2.8             | CRU Relative Addressing                             |

|     | 3.3   | _                 | on of Terminology                                   |

|     | 3.4   |                   | egister Manipulation                                |

|     | 3.5   |                   |                                                     |

|     | 3.5   | 3.5.1             | lons Dual Operand Instructions (Multiple Addressing |

|     |       | 3.2.1             | bual Operand Instructions (Multiple Addressing      |

|     |       | 3.5.2             | for Source and Definition)                          |

|     |       | 3.9.4             | Dual Operand Instructions (Multiple Addressing      |

|     |       | 2 = 2             | for Source)                                         |

|     |       | 3.5.3<br>3.5.4    | Signed Multiply and Divide Instructions             |

|     |       | 3.5.5             | Extended Operation (XOP) Instruction                |

|     |       | 3.5.6             | Single Operand Instructions                         |

|     |       | •                 | CRU Multiple Bit Instructions                       |

|     |       | 3.5.7             | CRU Single Bit Instructions                         |

|     |       | 3.5.8             | Jump Instructions                                   |

|     |       | 3.5.9             | Shift Instructions                                  |

|     |       | 3.5.10            | Immediate Register Instructions                     |

|     |       | 3.5.11            | Internal Register Load Immediate Instructions       |

|     |       | 3.5.12            | Internal Register Load and Store Instructions       |

|     |       | 3.5.13            | Return Workspace Pointer (RTWP) Instruction         |

|     |       | 3.5.14            | External Instructions                               |

|     | 2 6   | 3.5.15            | MID Interrupt Opcodes                               |

|     | 3.6   |                   | Lon Execution                                       |

|     |       | 3.6.1             | Microinstruction Cycle                              |

|     |       | 3.6.2             | Execution Sequence                                  |

| 1   |       | 3.6.3             | THAT Instruction Execution Times                    |

| 4.0 |       |                   | DESCRIPTION                                         |

| 5.0 |       |                   | ECIFICATIONS                                        |

|     | 5.1   | THUMBER           | Maximum Ratings                                     |

|     | 5.2   | TYPE THE PARTY OF | Recommended Operating Conditions                    |

|     | 5.3   |                   | Electrical Characteristics                          |

|     |       | 5.3.1             | General                                             |

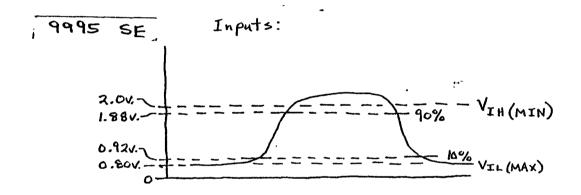

|     |       | 5.3.2             | Clock Characteristics                               |

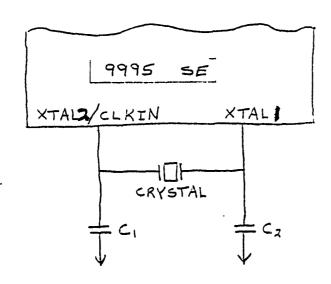

|     |       |                   | 5.3.2.1 Internal Oscillator                         |

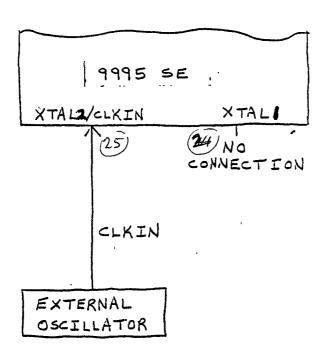

|     |       |                   | 5.3.2.2 External Clock Source                       |

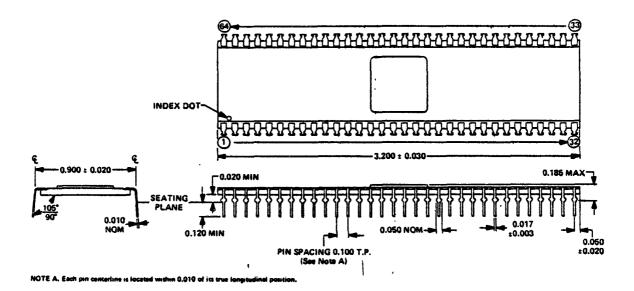

| 6.0 | M     | ECHANICAL         | SPECIFICATIONS                                      |

# LIST OF TABLES

| <u> </u> | TITLE                                    | SHEET | NO. |

|----------|------------------------------------------|-------|-----|

| 1.       | Status Register Bit Definitions          |       |     |

| 2.       | Dedicated Workspace Registers            |       |     |

| 3.       | 9995 SE Pin Description                  |       |     |

| 4.       | Interrupt Level Data                     |       |     |

| 5.       | - Flag Register Bit Definitions          |       |     |

| 5.       | 9995 SE External Instruction Codes       |       |     |

| 6.       | Definition of Terminology                |       |     |

| 7.       | Instruction Execution Times              |       |     |

| 8.       | 9995 SE Maximum Ratings                  |       |     |

| 9.       | 9995 SE Recommended Operating Conditions |       |     |

| 10.,     | 9995 SE Electrical Characteristics       |       |     |

| 11-      | 9995 SE Switching Characteristics        |       |     |

## LIST OF FIGURES

| FIGURE         | TITLE                                                                                    | SHEET      | NO. |

|----------------|------------------------------------------------------------------------------------------|------------|-----|

| 1.             | Word and Byte Formats                                                                    |            |     |

| 2.             | 9995 SE Memory Map                                                                       |            |     |

| 3.             | 9995 SE Block Diagram                                                                    |            |     |

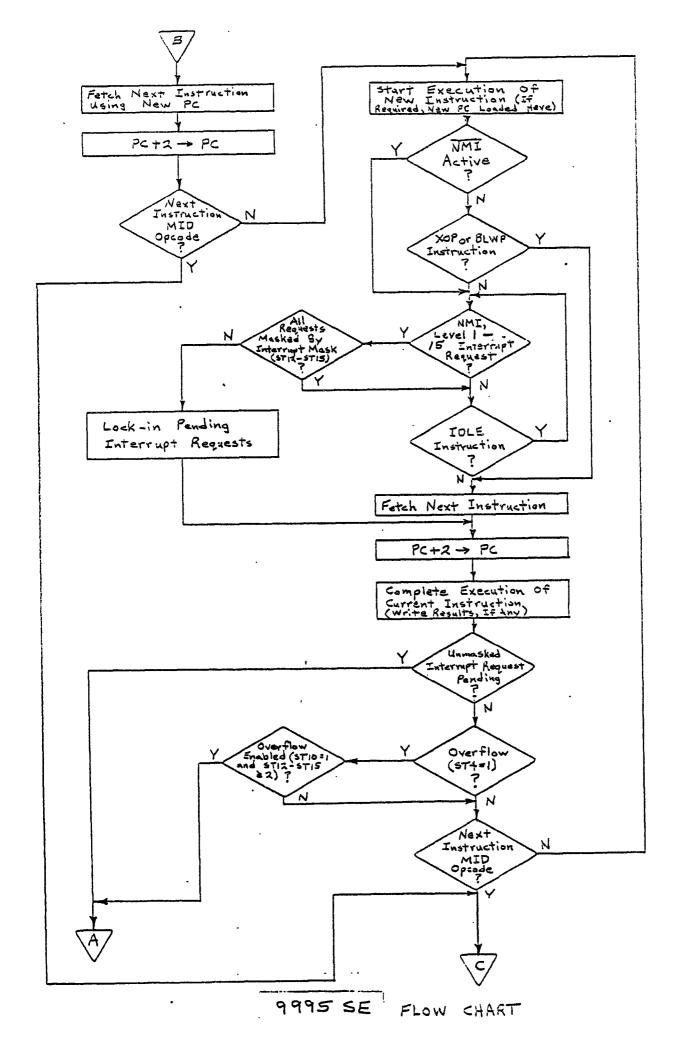

| 4.             | 9995 SE Flow Chart                                                                       |            |     |

| 5.             | Status Register Bit Assignments                                                          |            |     |

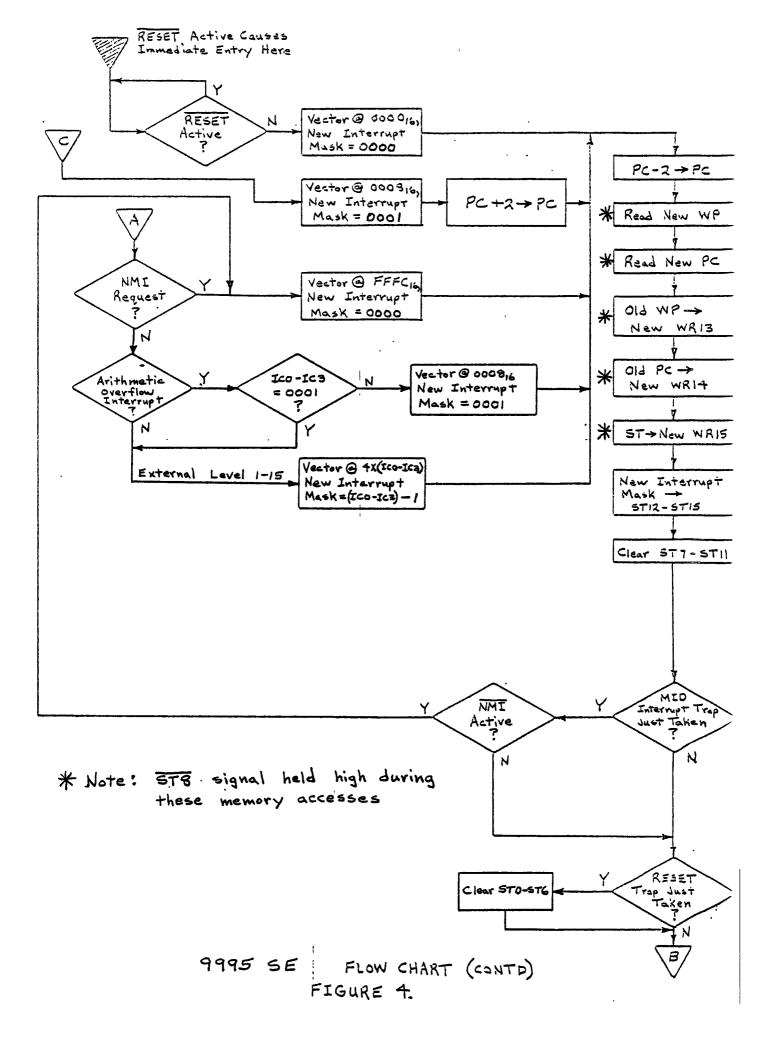

| 6.             | Workspace Registers Usable as Index Registers                                            |            |     |

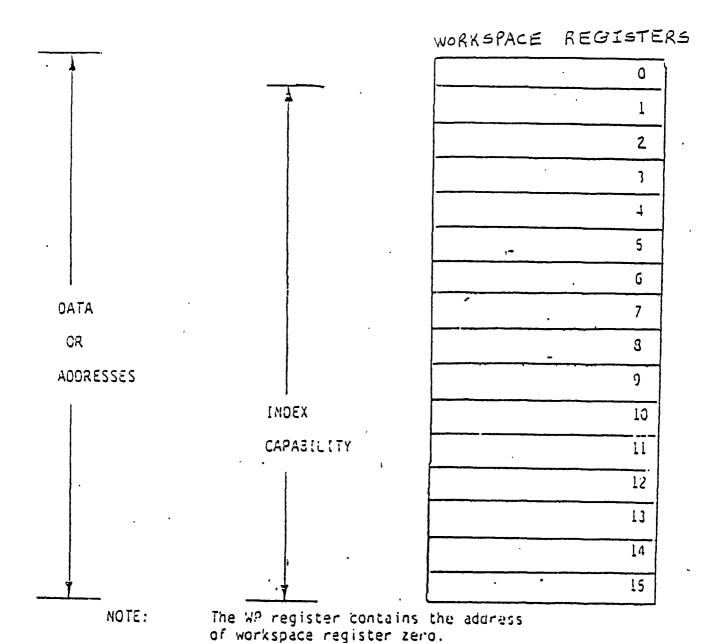

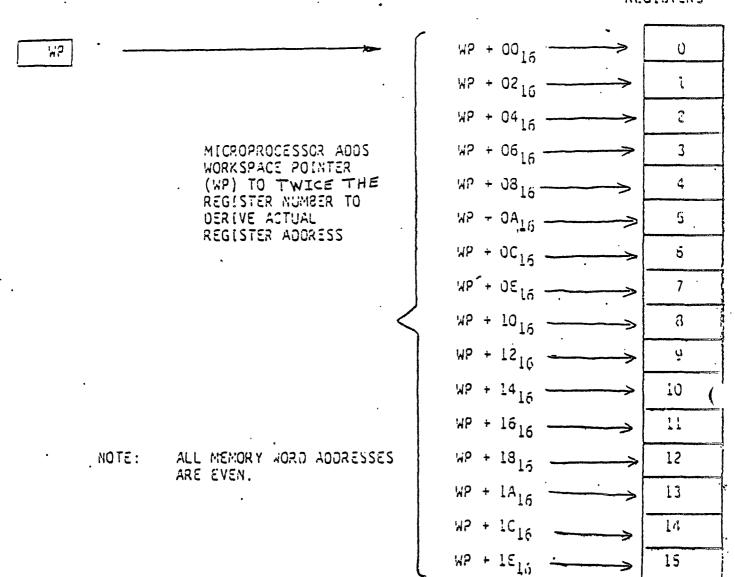

| 7.             | Workspace Pointer and Registers                                                          |            |     |

| 8.             | 9995 SE Memory Interface                                                                 |            |     |

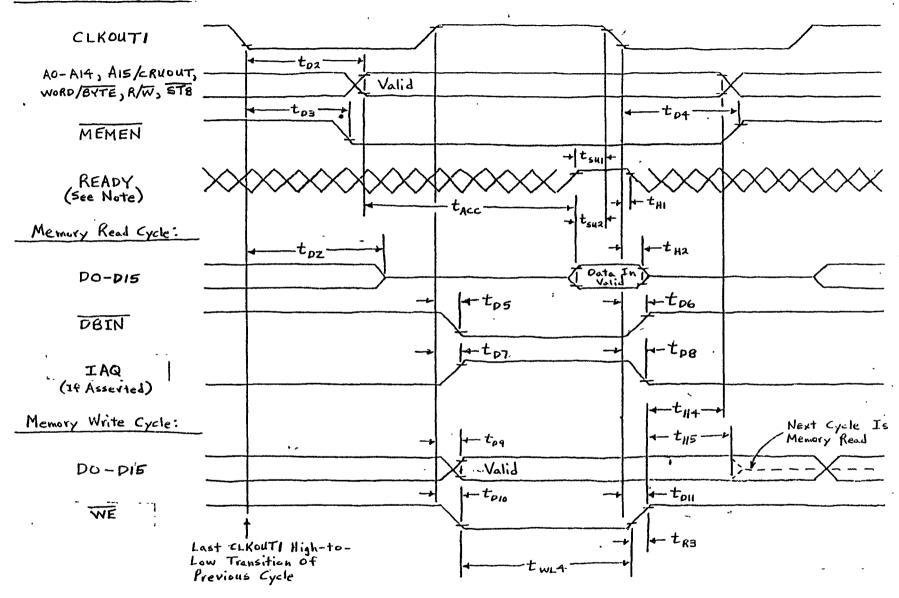

| 9.             | 9995 SE Memory Read Cycle                                                                |            |     |

| 10.            | 9995 SE Memory Write Cycle                                                               |            |     |

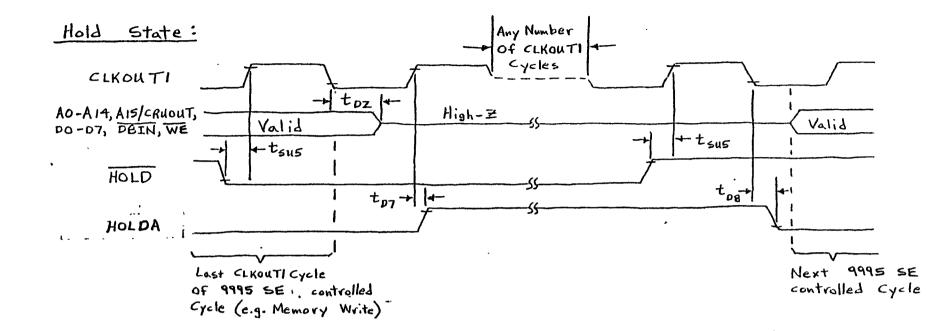

| 11.            | 9995 SE Hold State                                                                       |            |     |

| 12.            | Decrementer Functional Block Diagram                                                     |            |     |

| <del>13.</del> | Wait State Generation for External Memory and External GRU Gycles                        |            |     |

| 14.            | External Circuitry For Invoking/Inhibiting Automatic First Wait State Generation Feature |            |     |

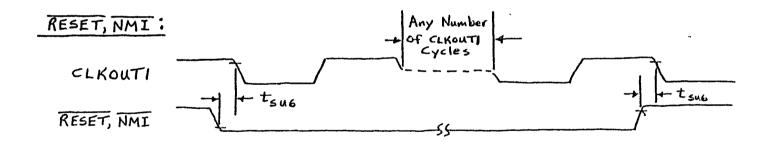

| 12.            | 9995 SE RESET- Signal Timing Relationships                                               |            |     |

| 13.            | 9995 SE NMI- Signal Timing Relationships                                                 |            |     |

| <del>17 </del> | Functional Block Diagram of Internal Interrupt Request Late                              | <u>c</u> h |     |

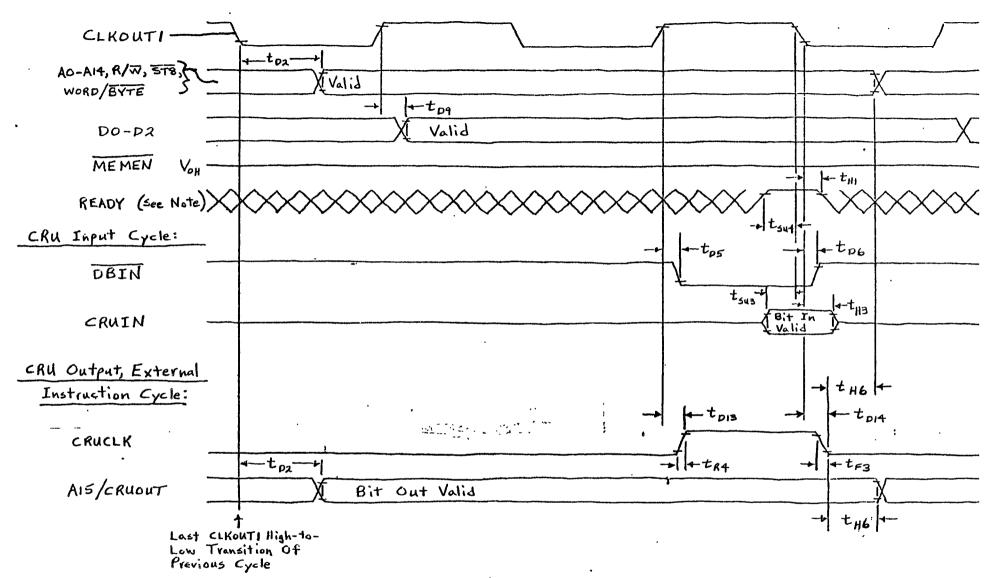

| 14.            | 9995 SE CRU Interface                                                                    |            |     |

| 19.            | - CRU Address Map                                                                        |            |     |

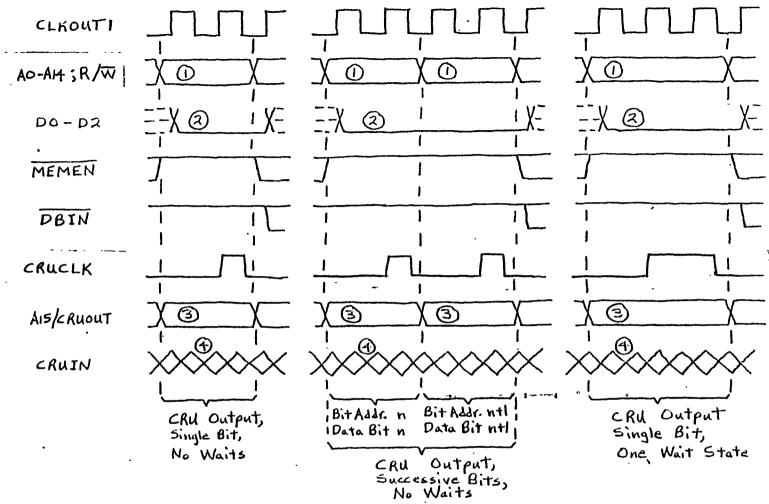

| 15.            | 9995 SE CRU Input Cycle                                                                  |            |     |

| 16.            | 9995 SE CRU Output Cycle                                                                 |            |     |

## LIST OF FIGURES (CONT.)

|    | FIGURE                 | TITLE                                                                                                                                                           | SHEET | NO. |

|----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

|    | 17.                    | Single Bit CRU Address Development                                                                                                                              | -     |     |

|    | 18.                    | LDCR/STCR Data Transfers                                                                                                                                        |       |     |

|    | <del>&gt;</del><br>25, | Execution Sequence Example                                                                                                                                      |       |     |

|    | 26.                    | 9995 SE Pin Assignments                                                                                                                                         |       |     |

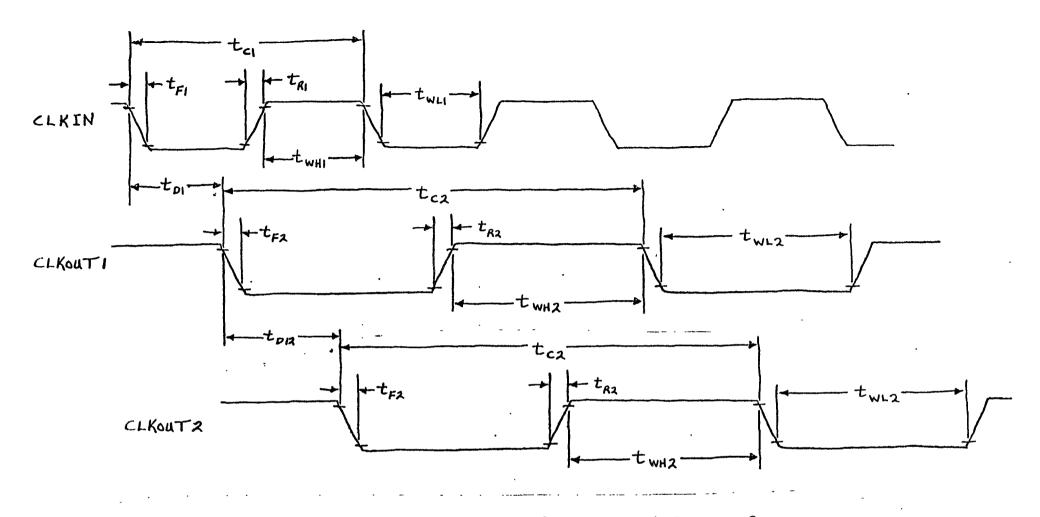

|    | 27.                    | 9995 SE Clock Timing                                                                                                                                            |       |     |

|    | 28,                    | 9995 SE Memory Interface Timing                                                                                                                                 |       |     |

|    | 29.                    | 9995 SE CRU, External Instruction Interface Timing                                                                                                              |       |     |

|    | 30,                    | 9995 SE HOLD-, RESET-, and NMI- Timing                                                                                                                          |       |     |

|    | 31.<br>32.             | 1995 SE INTREQ-, ICO-IC3 Timing Timing of Special Signals THE 1995 Event Counter Input Timing                                                                   |       |     |

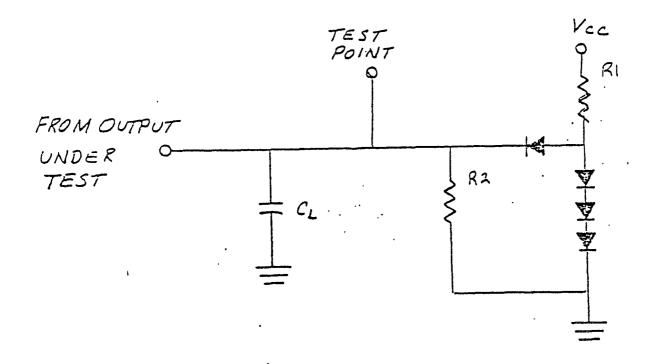

|    | 33.                    | Switching Characteristics Test Load Circuit                                                                                                                     |       |     |

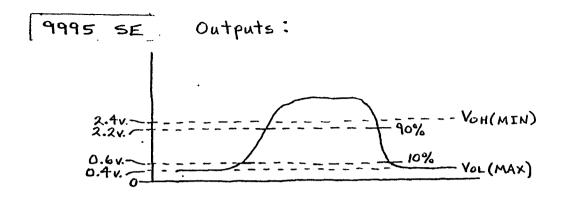

|    | 3 <del>1</del> .       | Measurement Points for Switching Characteristics                                                                                                                |       |     |

|    | 3 <i>5</i> .           | Internal Oscillator                                                                                                                                             |       |     |

|    | 36.                    | External Oscillator                                                                                                                                             |       |     |

|    | 37.                    | 9995 SE Mechanical Data                                                                                                                                         |       |     |

|    | , ·                    |                                                                                                                                                                 |       |     |

|    | (19.                   | Nait State Generation For Memory, CRU, and External Instruction Cycles External Circuitry For Invoking/Inhibiting Automatic First Wait State Generation Feature | •     |     |

| C, | Zai. "                 | 7995 SE/9990 - Signal Effect On Memory Read Cy                                                                                                                  |       |     |

|    |                        | 9995 SE/9990— Signal Effect On Memory Write C<br>DESTWRITE Signal Characteristics                                                                               | yeles |     |

|    |                        | FREEZE-Signal Characteristics                                                                                                                                   |       |     |

|    | 1                      |                                                                                                                                                                 |       |     |

# 1.0 SCOPE

This specification establishes the characteristics and performance requirements of the TMS 9995 System Emulator (9995 SE).

# 1.1 Description

The 9995 SE is a single-chip NN-channel silicon-gate MOS technology) of the CPU (central processing unit) of the TMS 9995 microprocessor. The 9995 SE, when combined with external circuitry that implements the on-chip "peripheral" functions of the TMS 9995 is intended to be the vehicle by which a full-function, real-time, completely controllable in-circuit emulator design can be executed.

# 1.2 <u>Characteristics</u>

The characteristics of the 9995 SE are identical to those of the TMS 9995 EXCEPT that the 9995 SE has:

- 10 no on-chip RAM

- · no on-chip Timer/Event Counter (Decrementer)

- . . no on-chip Filags

- 16-Bit Mamory Data Bus (95 hr an 8 bit DATA BUS

- · 18 Provitized Hardware Interrupta (95 hr 7)

- · Extra Control Signals For Emulation

2.1

Memory Allocation

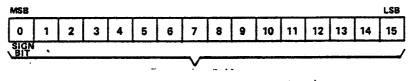

Addressing of 16-bit words and 8-bit bytes using the 16-bit data bus and the 16-bit byte address is

These 16 bits are folded into the 3 bit data path to external memory in the manner shown in Figure 1. A word is therefore defined as two consecutive 8 bit bytes in memory. All words (Instruction opcodes, operand addresses, word-length data, etc.) are restricted to be on even address boundaries (i.e. the most significant half or 8 bits resides at an even address and the least significant half resides at the subsequent odd address). Any memory access involving a full word that is directed by software to utilize an odd address to begin the word access with will result in the word starting with this odd address minus one to be accessed.

The instruction set of the 9995 SE allows both word and byte operations. Byte instructions may address either byte as necessary. A byte access of this type will not affect the other byte of the word involved since the other byte will not be accessed during the execution of the byte instruction.

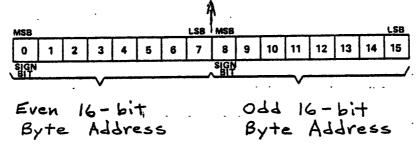

The 9995 SE memory map is shown in Figure 2. Shown are the locations in the memory address space for the Reset, NMI, other interrupt and XOP trap vectors, and the dedicated address segments for the on this RAM and the on this memory mapped I/O.

# 2.2 Management Organization

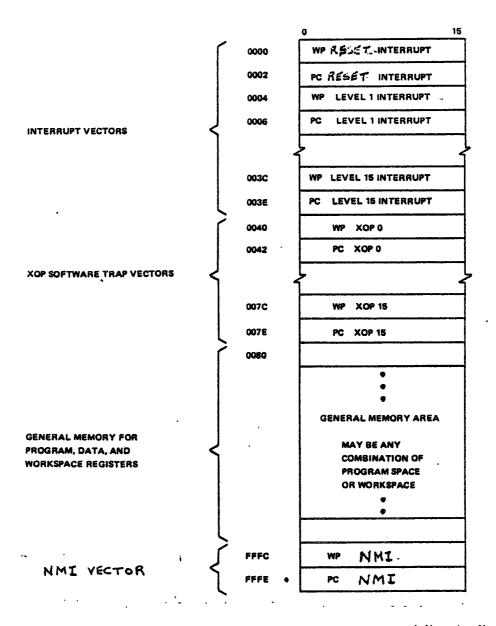

The block diagram of the 9995 SE is shown in Figure 3. A flow chart, representative of the 9995 SE functional operation, is shown in Figure 4.

# 2.2.1 Arithmetic Logic Unit

The arithmetic logic unit (ALU) is the computational component of the 9995 SE. It performs all arithmetic and logic functions required to execute instructions. The functions include addition, subtraction, AND, OR, exclusive OR, and complement. A separate comparison circuit performs the logic and arithmetic comparisons to control bits O through 2 of the status register. The ALU is arranged in two 8-bit halves to accommodate byte operations. Each half of the ALU operates on one byte of the operand. During word operand operations, both halves of the ALU function in conjunction with each other. However, during byte operand processing, results from the least significant half of the ALU are ignored. The most significant half of the ALU performs all operations on byte operands so that the status circuitry used in word operations is also used in byte operations.

circuitry used in word operations is also used in byte operations.

External logic must therefore be implemented to protect the other byte of a word when an individual when an wordler to byte word/BYTE (The word/BYTE signal individual when are bytes accessed).

#### 2.2.2 Internal Registers

The following three (3) internal registers are accessible to the user (programmer):

- (A) Program Counter (PC)

- (B) Status Register (ST)

- (C) Workspace Pointer (WP)

Other internal registers which are utilized during instruction acquisition or execution are inaccessible to the user.

### 2.2.2.1 Program Counter

The Program Counter (PC) is a 15-bit counter that contains the word address of the next instruction following the instruction currently executing. The microprocessor references this address to fetch the next instruction from memory and increments the address in the PC when the new instruction is executing. If the current instruction in the microprocessor alters the contents of PC, then a program branch occurs to the location specified by the altered contents of PC. All context switching operations plus simple branch and jump instructions affect the contents of PC.

#### 2.2.2.2 Status Register

The status register (ST) is a fully implemented 16-bit register that reports the results of program comparisons, indicates program status conditions, and supplies the arithmetic overflow enable and interrupt mask level to the interrupt priority circuits. Each bit position in the register signifies a particular function or condition that exists in the microprocessor. Figure 5 illustrates the bit position assignments. Some instructions use the status register to check for a prerequisite condition; others affect the values of the bits in the register; and others load the entire status register with a new set of parameters. Interrupts also modify the status register. The description of the instruction set later in this document details the effect of each instruction on the status register (see section 3.5). Table 1 lists each bit and identifies what conditions affect that bit.

#### 2.2.2.3 Workspace

The qqq5 SE uses blocks of memory words, called workspaces, for instruction operand manipulation instead of internal hardware registers. A workspace occupies 16 contiguous words in any part of memory that is not reserved for other use. The individual workspace registers may contain data or addresses, and function as operand registers, accumulators, address registers, or index registers. Some workspace registers take on special significance during execution of certain instructions. Table 2 lists each of these dedicated workspace registers and the instructions that use them. Figure 6 defines the workspace registers that are allowed

to be used as index registers. A larger number of workspaces may exist in memory simultaneously to provide a high degree of software flexibility.

#### 2.2.2.3.1 Workspace Pointer

To locate the workspace in memory, a hardware register called the workspace pointer (WP) is used. The workspace pointer is a 16 bit register that contains the memory address of the first word in the workspace. The address is left justified with the 16th bit (LSB) hardwired to logic zero. The 9995 SE accesses each register in the workspace by adding two times the register number to the contents of the workspace pointer and initiating a memory request for that word. Figure 7 illustrates the relationship between the workspace pointer and its corresponding workspace in memory.

For instructions performing byte operations, use of the workspace register addressing mode (see section 3.2) will result in the most significant byte of the workspace register involved to be used as the operand for the operation. Since the workspace is also addressable as a memory address, however, the least significant byte may be directly addressed, if desired, using any of the more general memory addressing modes.

#### 2.2.2.3.2 Context Switching

The workspace concept is particularly valuable during operations that require a context switch, which is a change from one program environment to another, as in the case of a subroutine or an interrupt service routine. Such an operation using a conventional multi-register arrangement requires that at least part of the contents of the register file be stored and reloaded using a memory cycle to store or fetch each word. The 9995 SE accomplishes this operation by changing the workspace pointer. A context switch requires only three store cycles and there fatch two cycles, exchanging the program counter, status register and workspace pointer. After the switch, the workpace pointer contains the starting address of a new 16-word workspace in memory for use in the new routine. A corresponding time saving occurs when the original context is restored. Instructions in the 9995 SE that result in a context switch include: - Branch and Load Workspace Pointer (BLWP), Return from Subroutine (RTWP) and the Extended Operation (XOP) instruction. All interrupts also cause a context switch by forcing the 9995 SE to trap to a service subroutine.

# 2.3 MANAGE INTERFACES

Each 9995 se system interface uses one or more of the signals from one or more of the signal groupings given in the pin description list in Table 3. Each interface is described in detail in the following paragraphs.

2.3.1 Memory Interface

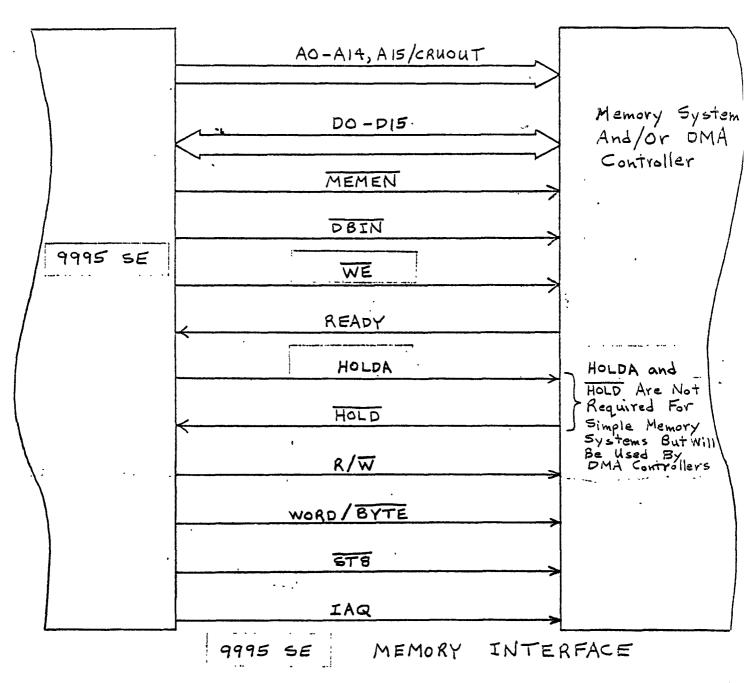

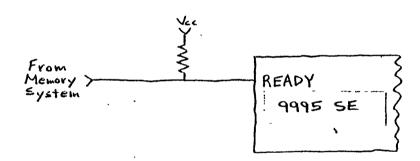

The signals used in the 9995 SE basic interface to system memory are shown in Figure 8.

# 2.3.1.1 Memory Read Operations

A Cortain appeiral signals who applicable to memory head operations of detailed in backin 2.3.7.

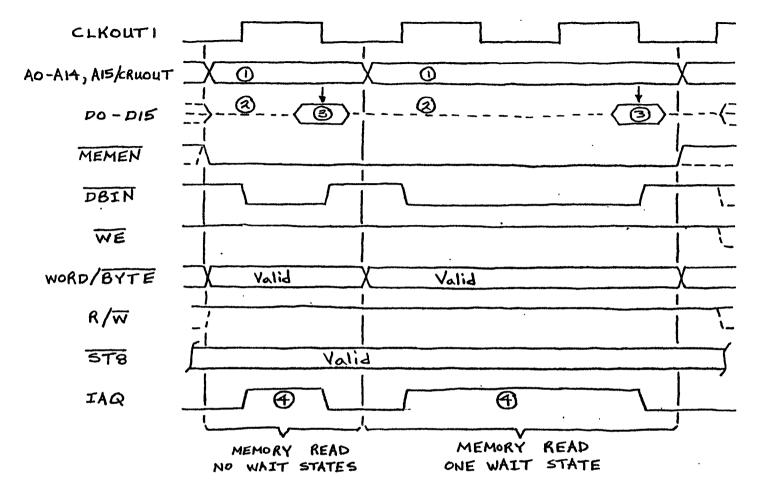

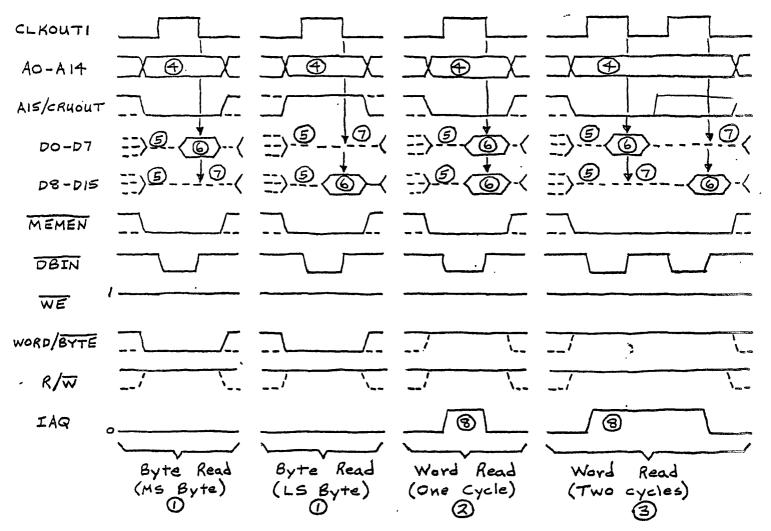

Timing relationships of the memory read sequent are shown in Figure 9. Completion of a memory read cycle and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.4. Note that MEMEN- remains active (low) between consecutive memory operations. Also during memory read cycles that an instruction opcode is being read, IAQ will be asserted as shown in Figure 9.

I f an instruction directs that a byte read is to be performed, WORD/BYTE- will be low and only the byte specifically addressed will be read on the half of the data bus that corresponds to the byte address.

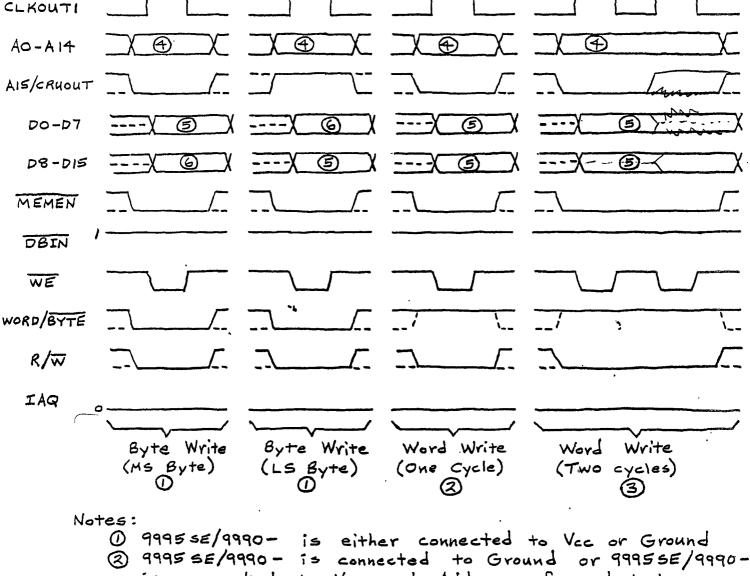

# 2.3.1.2 Memory Write Operations

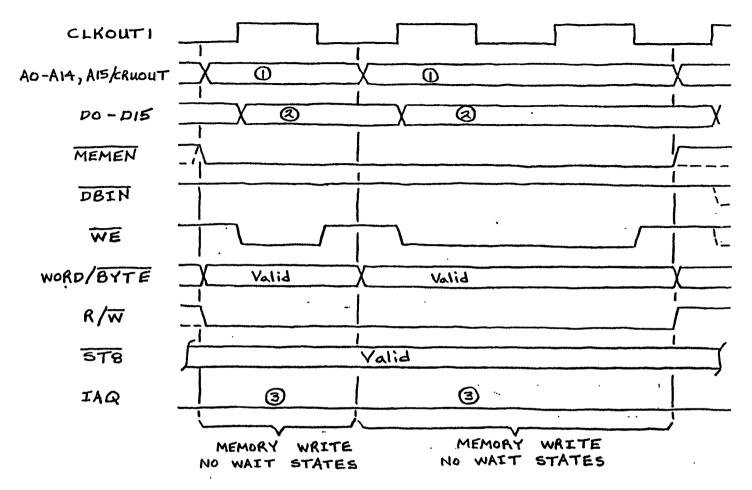

Timing relationships of the memory write sequence are shown in Figure 10. Completion of a memory write cycle and for generation of Wait states is determined by the READY input as detailed in Section 2.3.4. Note that MEMEN-remains active (low) between consecutive memory operations.

If an instruction directs that a byte write is to be performed, WORD/BYTE- will be low- and write data will be valid only on the half of the data bus that corresponds to the byte specifically addressed. External logic must use WORD/BYTE- to maintain the integrity of the contents of the other byte in the word.

Certain special signals are applicable to memory write operations as detailed in Section 2.3.7.

cight-bit bytes) to external memory requires two memory write cycles that will coom back to-back (Note: a Hold state request will not be granted between them). If an instruction directs that a byte write to external memory is to be performed, only the byte specifically addressed will be written to (one memory write eyele). External words are accessed most significant (even) byte first, followed by the least eignificant (odd) byte.

# 2.3.1.3

#### Direct Memory Access

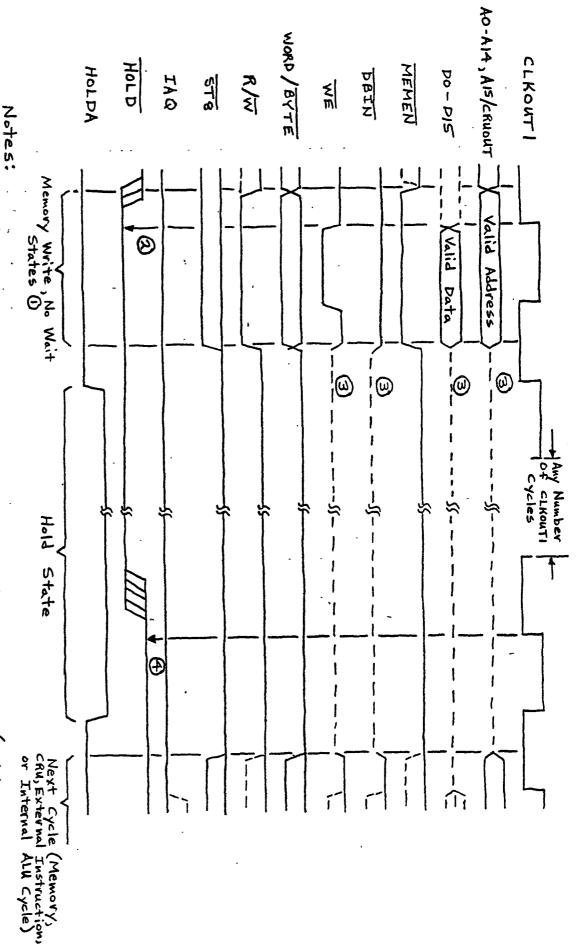

The 9995 SE Hold state allows both external devices and the 9995 E to share a common external memory. To gain direct memory access (DMA) to the common memory, the external device first requests the 9995 SE to enter a Hold state by asserting (taking low) the HOLD- input. The 9995 SE will then enter a Hold state following completion of the cycle (either memory, CRU, external Instruction, or internal ALU cycles) that it is currently performing. Note however, that a Hold state will not be entered between the first and second byte accesses of a full word excessed in the external memory address space, and a Weld-state will not be entered between the first and second clock cycles of a CRU cycle.

and control signal drivers into specific states,

Upon entry of a Hold state, the 9995 SE puts its address, data, DBIN, and WE-/CRUCKE drivers in the high impedance meda, and asserts HOLDA. The external device can then utilize these signal lines to communicate with the common memory. After the external device has completed its memory transactions, it releases HOLD, and the 9995 SE will continue instruction execution at the point where it had been suspended. Timing relationships for this sequence are shown in Figure 11.

In order to allow DMA loading of external memory on power-up, the 9995 SE will not begin instruction execution after a Reset state until HOLD has been removed if HOLD was active (low) at the time RESET was taken from low to high (RESET released).

External devices cannot access the internal (on calp) memory address space of the TMS 9995 when it is in the Hold state.

Since IAQ (Instruction Opcode Acquisition) and HOLDA (Hold Acknowledge) are multiplexed on a single signal, IAQ/HOLDA, this signal must be gated with MEMEN using external logic to separate IAQ and HOLDA (when MEMEN =0, IAQ/HOLDA can indicate IAQ, and when MEMEN =1, IAQ/HOLDA can indicate IAQ, and

# 2.3.1.2 Internal Memory Address Space

Acces of the internal (on chip) memory address opace is transparent to the TMS 9995 instruction set. That is, operands can be read from and written into locations in the internal memory space simply by using the appropriate addresses via any of the addressing modes in the TMS 9995 instruction set, and

Wait states cannot be generated during external instruction eyeles or internal All/other operation eyeles, and the RFADY input is ignored during these eyeles.

# 2.3.2 MANY Interrupts

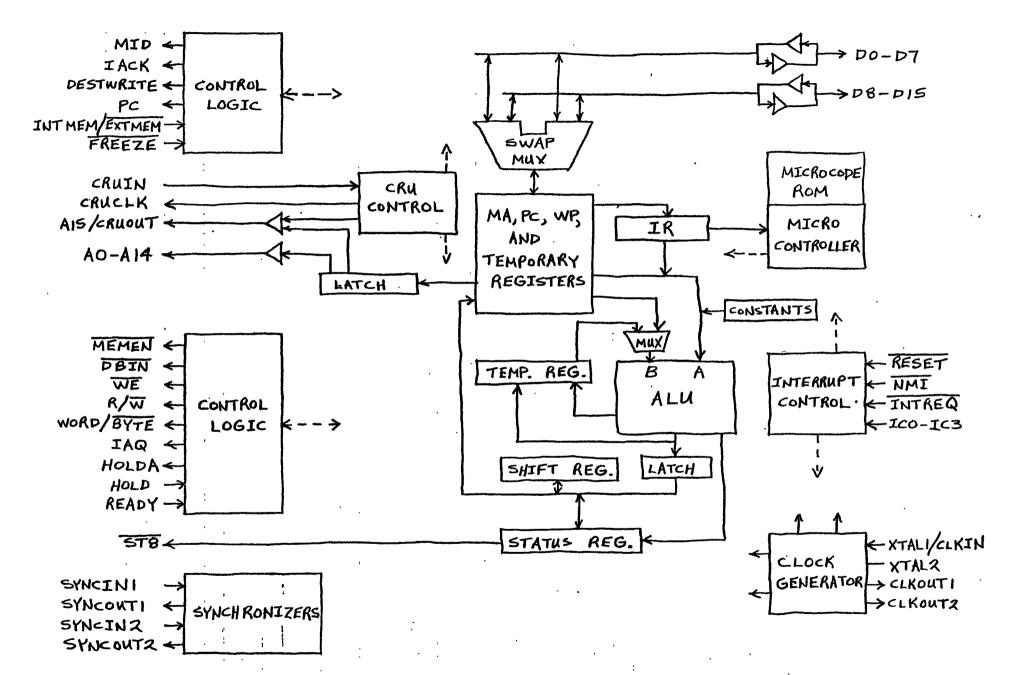

The 9995 SE implements seven prioritized, vectored interrupts, some of which are dedicated to predefined functions and the rest of which are user-definable. Table 4 defines the source (internal or exernal), assignment, priority level, trap vector location in memory, and enabling/resulting status register interrupt mask values for each interrupt.

The 1995 SE will grant interrupt requests only between instructions except for (Level 0) Reset, which will be granted whenever it is requested (i.e. in the middle of an instruction). The basic sequence that the 9995 SE performs to service all interrupt requests is as follows (Note that the 9995 SE performs additional functions for certain interrupts, and these functions will be detailed in subsequent sections):

- (1) Prioritize all pending requests and grant the request for the highest priority interrupt that is not masked by the current value of the interrupt mask in the status register or the instruction that has just been executed (See Section 3.5 for these instructions).

- (2) Make a context switch using the trap vector specified for the interrupt being granted.

- (3) Reset ST7 through ST11 in the status register to zero, and change the interrupt mask (ST12 through ST15) as appropriate for the level of the interrupt being granted.

- (4) Resume execution with the instruction located at the new address contained in the PC, and using the new WP. All interrupts will be disabled until after this first instruction is executed, unless: (a) Reset is requested, in which case it will be granted, or (b) the interrupt being granted is the MID request and the NMI interrupt is requested simultaneously, in which case the NMI request will be granted before the first instruction indicated by the MID trap vector will be executed.

Note that this sequence has several important characteristics. First of all, for those interrupts that are maskable with the interrupt mask in the status register, the mask will get changed to a value that will permit only interrupts of higher priority to interrupt their service routines. Secondly, status bit ST10 (overflow interrupt enable) gets reset to zero by the servicing of any interrupt so that overflow interrupt requests cannot be generated by an unrelated program segment. Thirdly, the disabling of other interrupts until after the first instruction

of the service routine is executed permits the routine to disable other interrupts by changing the interrupt mask with the first instruction (the exception with MID and NMI is explained in Section 2.3.2.2%). Lastly, the vectoring and prioritizing scheme of the 9995 5E permits interrupts to be automatically nested in most cases. If a higher priority interrupt occurs while in an interrupt service routine, a second context switch occurs to service the higher priority interrupt. When that routine is complete, a return instruction (RTWP) restores the saved context to complete processing of the lower priority interrupt. Interrupt routines should therefore terminate with the return instruction to restore original program parameters.

Additional details of the 9995 se interrupts are supplied in the following paragraphs.

## 2.3.2.1 • External Interrupt Requests

Each of these interrupts is requested when the designated signal is supplied to the 9995 SE.

## 2.3.2.1.1 Interrupt Level 0 (RESET-)

all control signals.

Interrupt Level 0 is dedicated to the RESET- input of the 9995 SE. When active (low), RESET- causes the 9995 SE to stop instruction execution and to inhibit (take to logic level) HEMEN, DETAIL AND THE CRUSHE. The 9995 SE will remain in this Reset state as long as RESET- is active.

When RESET- is released (low-to-high transistion), the 9995 SE performs a context switch with the Level 0 interrupt trap vector (WP and PC of trap vector are in memory word addresses 0000 g and 0002 g, respectively). Note that the old WP, PC and ST are stored in registers 13, 14, and 15 of the new workspace. The 9995 SE then resets all status register bits, the internal interrupt request latches (see Sections 2-3-2-1-3 and 2-3-2-2-3 for details of these latches), Flag Register bits FLAGO and FLACI (see Section 2-3-3-2-1 for details of the Flag Register), and the MID Flag (See Section 2-3-3-2-2-2). After this the 9995 SE starts execution with the new PC.

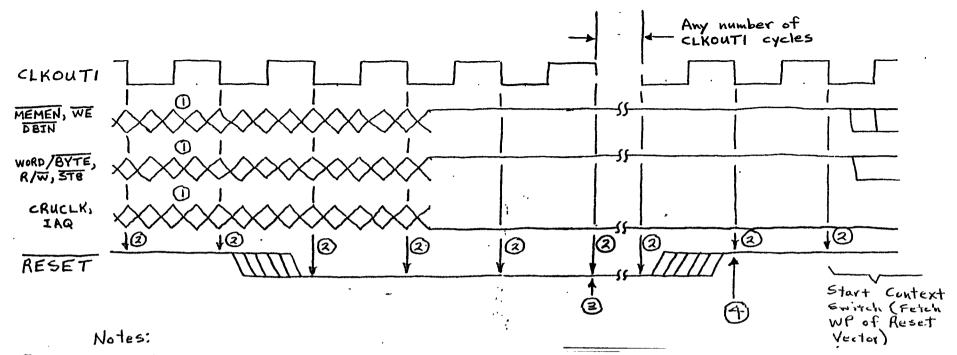

Timing relationships of the RESET- signal are shown in Figure 🔀

Release of the RESET- signal is also the time at which the Automatic First Wait State function of the 9995 se can be invoked (see Section 2.3.1.3).

#### 2.3.2.1.2 Non-Maskable Interrupt (NMI-)

The NMI- signal is the request input for the NMI level interrupt and allows ROM loaders, single-step/breakpoint/maintenance panel functions, or other user-defined functions to be implemented for the  $qqq \le se$  This signal and its associated interrupt level are

named "LOAD" in previous 9900 Family products.

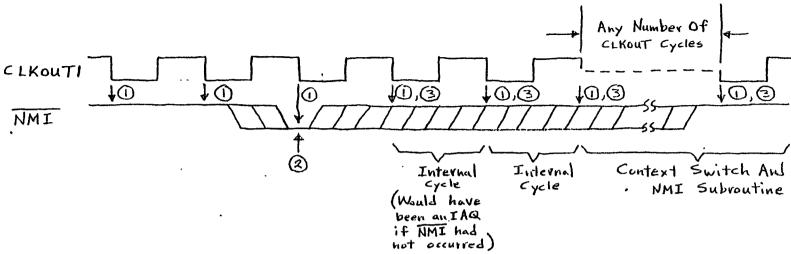

NMI- being active (low) according to the timing illustrated in Figure & constitutes a request for the NMI level interrupt. The 9995 SE services this request exactly according to the basic sequence previously described, with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 4. Note that the 9995 SE will always grant a request for the NMI level interrupt immediately after execution of the currently executing instruction is completed since NMI is exempt from the interrupt-disabling-after-execution characteristic of certain instructions and also the current value of the interrupt mask.

# 2.3.2.1.3 Interrupt Levels 1 Through 15

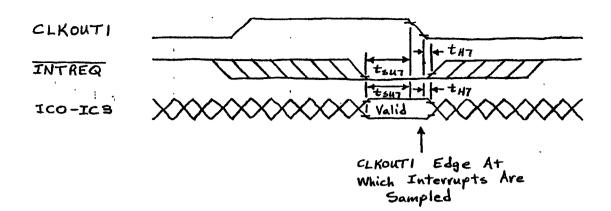

INTREQ - and ICO through IC3 are the request inputs for interrupt levels I through 15. A request is initiated by taking INTREQ - active (low) and simultaneously supplying the code for the desired interrupt level on ICO through IC3. The 9995 SE services each of these requests exactly according to the basic sequer previously described, with the priority levely, trap vector locations, and enabling/resulting status register interrupt mask values as defined in Table 4. All interrupt requests should remain active until recognized by the processor in the interrupt service routine. The individual service routines then reset the interrupt requests prior to returning from the routines.

## 2.3.2.2 Internally Generated Interrupts

Each of these interrupts is requested when the designated condition has occured in the 9995 be.

#### 2.3.2.2.1 Macro Instruction Detection (MID) Interrupt

The acquisition and attempted execution of an MID interrupt opcode will cause the MID level interrupt to be requested before execution of the next instruction will begin (MID interrupt) opcodes are defined in Section 3.5.15). In addition to requesting the MID level interrupt, the MID Flag is set to the (see Section 3.3.3.2.2). The 9995 services this request exactly according to the basic sequence previously described, with the priority level, trap vector location, and enabling/ resulting status register interrupt mask values as defined in Table 4. Note that the 9995 SE will always grant a request for the MID level interrupt since MID is not affected by the interrupt mask and is higher in priority than any other interrupt except for Level 0, Reset. If the NMI interrupt is requested during an MID interrupt context switch, the MID interrupt context switch will be immediately followed by the NMI interrupt service sequence before the first instruction indicated by the MID interrupt is executed. This is done so that the NMI interrupt can be used for a single-step function with MID opcodes. Servicing the MID interrupt request is viewed as "execution" of an MID interrupt opcode, and NMI will allow the 9995 SE to be halted immediately after encountering an MID opcode.

and also the external Level 2 request.

It should also be noted that the MID interrupt shares its trap vector with Level 2 the Arithmetic Overflow interrupt (Section 2.3.2.2.2). The interrupt subroutine beginning with the PC of this vector chould examine the MID Flag to determine the cause of the interrupt. If the MID Flag is set to one, an MID interrupt has occurred, and if the MID Flag is set to zero, an Arithmetic Overflow interrupt has occurred. The portion of this interrupt subroutine that handles MID interrupts should always, before returning from the subroutine, reset the MID Flag to zero.

The MID interrupt has basically two applications. The MID opcodes can be considered to be illegal opcodes and the MID interrupt is then used to detect errors of this nature. The second, and primary application of the MID interrupt is to allow the definition of additional instructions for the 9995 se. MID opcodes are used as the opcodes for these macro instructions and software in the MID interrupt service routine emulates the execution of these instructions. The benefit of this implementation of macros is that the macro instructions can be implemented in microcode in future processors and software will then be directly transportable to these future processors.

It should be noted that the 9995 SE interrupt request processing sequence does create some difficulties for re-entrant usage of

Signal is

must therefore do)

MID interrupt macro instructions. In general, to avoid possible errors, MID interrupt macro instructions should not be used in the NMI and Level 1 interrupt subroutines, and should only be used in the Reset subroutine if Reset is a complete initialization of the system.

#### 2.3.2.2.2 Arithmetic Overflow Interrupt

The occurrence of an arithmetic overflow condition, defined as status register bit 4 (ST4) getting set to one (See Table 1 for those conditions that set ST4 to one) can cause the Level 2 interrupt to be requested. Note that this request will occur at a time such that if the request is granted, it will be granted immediately after the instruction that caused the overflow condition. The 9995 SE services this request exactly according to the basic sequence previously described, with the priority level, trap vector location, and enabling/resulting status register interrupt mask values as defined in Table 4.

In addition to being maskable with the interrupt mask, the Level 2 overflow interrupt request is enabled/disabled by status register bit 10 (ST10), the Arithmetic Overflow Enable Bit (i.e., ST10=1 enables overflow interrupt request; ST10=0 disables overflow interrupt request). If servicing the overflow interrupt request is temporarily overridden by the servicing of a higher priority interrupt, the occurrence of the overflow condition will be retained in the contents of the status register (i.e. ST4=1), which is saved by the higher priority context switch. Returning from the higher priority interrupt subroutine via an RTWP instruction causes the overflow condition to be reloaded into status register bit ST4 and the overflow interrupt to be requested again (upon completion of RTWP instruction). arithmetic overflow interrupt subroutine must reset ST4 or ST10 to zero in the status word saved in register 15 before the routine is complete to prevent generating another overflow interrupt immediately after the return.

It should also be noted that the Level 2 arithmetic overflow interrupt shares its trap vector with the MID interrupt. Section 2.3.2.2.1 describes how the interrupt subroutine beginning with the FC of this vector can determine the cause of the interrupt.

# 2.3.2.2.3 Decrementer Interrupt

and the external Level 2 request, as discussed in the prévious section.

The securrence of an interrupt request by the decrementer (See Section 2.3.1.2.2) will cause the Level 3 internal interrupt request latch to get set. This latch is similar to those for Levels 1 and " in that it gets reset by servicing a Reset interrupt or when the context switch for its associated interrupt level occurs (Figure 17):

The Level 3 internal interrupt request latch being set constitutes a request for a bevel 3 interrupt, and the TMS 9995

proviously described, with the priority level, trap waston location, and enabling/resulting status register interrupt mask values as defined in Table 4.

#### 2.3.3 Communication Register Unit Interface

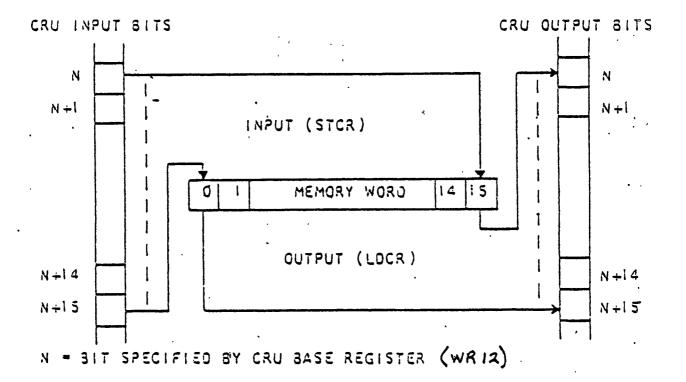

The 9995 55 communication register unit (CRU) is an instruction (software) driven bit-oriented I/O interface. The CRU can directly address, in bit-fields of one to sixteen-bits, up to 32768 input bits and 32768 output bits. The 9995 55 executes three single-bit and two multiple-bit instructions. The single-bit instructions are: TEST BIT (TB), SET BIT TO ONE (SBO), and SET BIT TO ZERO (SBZ); the multiple-bit instructions are: LOAD CRU (LDCR), and STORE CRU (STCR). Details of these instructions are given in Sections 3.5.6 and 3.5.7.

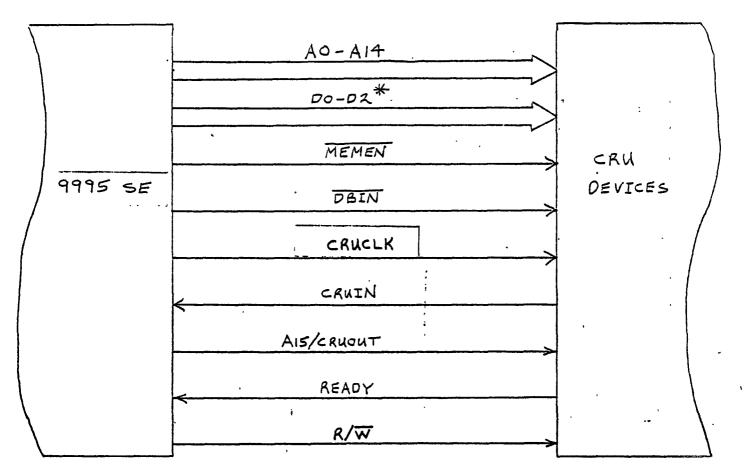

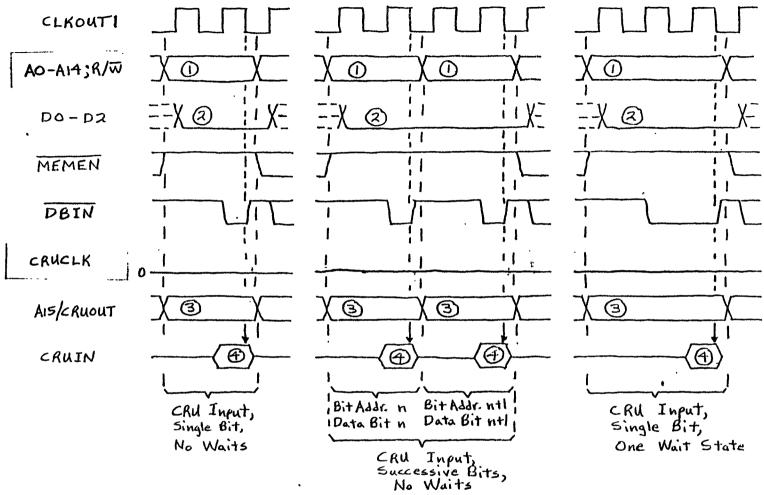

The signals used in the 9995 SE interface to the CRU are shown in Figure 35.14.

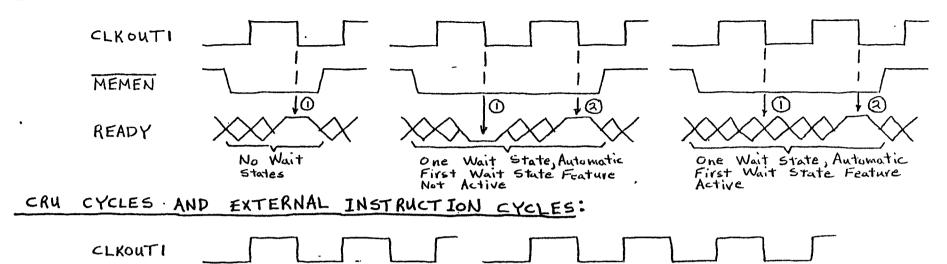

Timing relationships of the CRU input cycle and the CRU output cycle are shown in Figures 15 and 16, respectively. Completion of each CRU cycle and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.4.

2.3.3.1

20-

The output a data-bit to an external (off chip) CRU device, the TMS 9995 first outputs the appropriate address on AO A14. The TMS 9995 leaves MEMEN- high, outputs logic zeroes on DO D27 outputs the data bit on A15/CRUOUT, and strokes WE /CRUCLK Completion of each CRU output eyele and/or generation of Waitstates is determined by the READY input as detailed in Section 2.3.1.3. Timing relationships of the CRU output eyele are shown in Figure 27.

(LDCR or STCR instructions)

with the bit ddress incremented ach cycle)

repeated until transfers these input and output cycles are repeated until transfer of the entire field of data bits specified by the CRU instruction being executed has been accomplished. Hold states can occur between these cycles, but will never be granted during any bit cycle.

Single Bit CRU Operations

2.3.3.1

The 9995 SE performs three single-bit CRU functions: TEST BIT (TB), SET BIT TO ONE (SBO), and SET BIT TO ZERO (SBZ). The SBO instruction performs a CRU output cycle with logic one for the

data bit, and the SBZ instruction performs a CRU output cycle with logic zero for the data bit. A TB instruction transfers the addressed CRU bit from the CRUIN input line to bit 2 of the status register (bit ST2, the EQUAL bit).

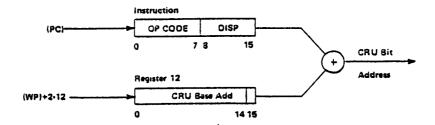

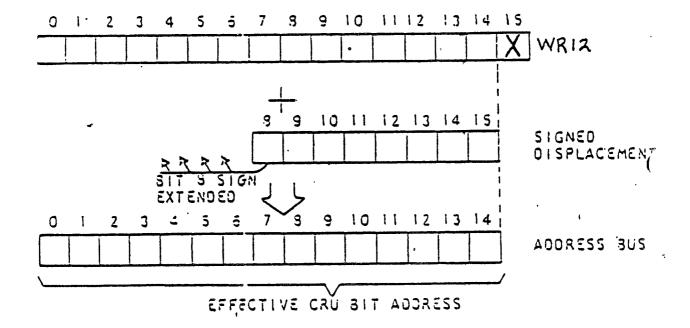

The 7995 SE develops a CRU bit address for the single-bit operations from the CRU base address contained in workspace register 12 and the signed displacement count contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The base address from WR12 is added to the signed displacement specified in the instruction and the result is placed onto the address bus. Figure 25 illustrates the development of a single-bit CRU address.

#### 2.3.3.2 <del>2.3.3.1.2</del>

#### Multiple Bit CRU Operations

The 9995 SE performs two multiple-bit CRU operations: store communications register (STCR) and load communications register (LDCR). Both operations perform a data transfer from the CRU-to-memory or from memory-to-CRU as illustrated in Figure 28.18. Although the figure illustrates a full 16-bit transfer operation, any number of bits from 1 through 16 may be involved.

The LDCR instruction fetches a word from memory and right shifts it to serially transfer it to CRU output bits. If the LDCR involves eight or fewer bits, those bits come from the right-justified field within the addressed byte of the memory word. If the LDCR involves nine or more bits, those bits come from the right-justified field within the whole memory word. Register 12, bits 0 through 14, defines the starting bit address. When transferred to the CRU interface, each successive bit receives an address that is sequentially greater than the address for the previous bit. This addressing mechanism results in an order reversal of the bits; that is, bit 15 of the memory word (or bit 7) becomes the lowest addressed bit in the CRU and bit 0 becomes the highest bit in the CRU field.

A STCR Instruction transfers data from the CRU to memory. If the operation involves a byte or less transfer, the transferred data will be stored right-justified in the memory byte with leading bits set to zero. If the operation involves from nine to 16 bits, the transferred data is stored right-justified in the memory word with leading bits set to zero. When the input from the CRU device is complete, the lowest addressed bit from the CRU is in the least significant bit position in the memory word or byte.

# 2.3.3.2 <u>Internal CRU Devices</u>

Access of internal (on chip) GRU devices is transparent to the TMS 9995 CRU instructions. That is, data can be input from and output to the bits of the internal CRU devices simply by using

and external instruction cycles

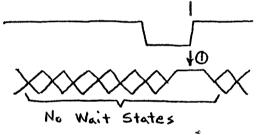

Wait states can be generated for Management memory cycles, and external CRU cycles for the 9995 SE using the READY input. A Wait state is defined as extention of the present cycle by one CLKOUT cycle. The timing relationship of the READY input to the memory interface and the CRU interface signals is shown in Figure 19. Material Wait states among the generated for memory cycles that access the internal memory address space or for SRU cycles that access the internal memory address space or for SRU cycles that access the internal CRU address spaces or for SRU cycles that access the internal cross cycles.

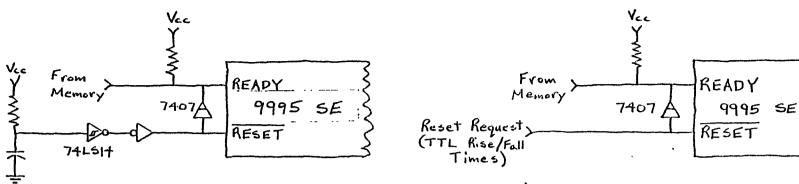

The Automatic First Wait State Generation feature of the 9995 SE allows a Wait state to be inserted in each external memory cycle, regardless of the READY input, as shown in Figure 12. The Automatic First Wait State Generation feature can be invoked when RESET is asserted. If READY is active (high) when RESET goes through a low-to-high transition, the first Wait state in each memory cycle will be automatically generated. If READY is inactive (low) when RESET goes through a low-to-high transition, no Wait state will be inserted automatically in each external memory cycle. There is a one and one-half CLKOUT.cycle time minimum setup time requirement on READY before the RESET low-to-high transition. The recommended external circuitry for invoking or inhibiting the Automatic First Wait State Generation 20 feature is shown in Figure Note that this feature does not apply to either internal memory address space assesses or any CRU cycles or external instruction cycles.

Wait states cannot be generated during the internal ALU/other operation cycles, and the READY input is ignored during these cycles.

# 2.3.5 External Instructions

The '9995 SE has five external instructions that allow user-defined external functions to be initiated under program control. These instructions are CKON, CKOF, RSET, IDLE, and LREX. These mnemonics, except for IDLE, relate to functions implemented in the 990 minicomputer and do not restrict use of the instructions to initiate various user-defined functions. Execution of an IDLE instruction causes the 1995 SE to enter the Idle state and remain in this state until a request occurs for an

Note that completion of each external instruction and/or generation of Wait states is determined by the READY input as detailed in Section 2.3.4.

ď

interrupt level that is not masked by the current value of the interrupt mask in the status register. (Note that the Reset and NMI interrupt levels are not masked by any interrupt mask value). When any of these five instructions are executed by the 9995 SEL the 9995 SE will use the CRU interface (See Figure 18) to perform a cycle that is identical to a single bit CRU output cycle (See Figure 21) except for the following: (1) the address being output will be non-specific, (2) the data bit being output will be non-specific, nd(3) a code, specified in Table 3,5, will be output on DO-D2 to indicate the external instruction being executed. When the 9995 SE is in the Idle state, cycles with the Idle code will occur repeatedly until a request for an interrupt level that is not masked by the interrupt mask in the status register occurs.

A Hold state can occur during an Idle state, with entry to and return from the Hold state occurring at the Idle code cycle boundaries (See Section 2.3.1,1.3 for details of entry to and 7.3.1.3 return from the Hold state).

2.3.6

## Internal ALU/Other Operation Cycles

When the 9995 SE is performing an operation internally and is not using the memory, CRU, or external instruction interfaces (internal memory space and internal CRU device accesses are defined as using the memory and GRU interfaces) or is not in the Hold state, the 9995 SE will, for as long (as many CLKOUT cycles) as the operation takes, do the following with its interface signals: (1) output a non-specific address on AO-A14 Do-F and A15/CRUOUT, (2) output non-specific data on DO D7, (3) output logic level high on MEMEN-, DBIN-, and WE / CRUCLE , (4) output logic level low on FAQ/HOLDA, and (5) ignore the READY and CRUIN inputs. The HOLD input is still active, however, as the 9995 SE can enter a Hold state while performing an internal ALU/other operation. Also, all interrupt inputs are still active. WE-, and R/W-,

IAQ, HOLDA, and cruck

# 2.3.7 Special Signals

The signals described in the following sections are required for emulation purposes.

# 2.3.7.1 9995 SE/9990 - Signal

The 9995 SE/9990 - signal, which is permanently connected to either VCC or ground in a system tells the 9995 SE device which memory map to use with its internal memory control logic. When 9995 SE/9990 - is connected to VCC the 9995 SE will use one cycle or two cycle memory word accesses according to the on-chip/off-chip memory addresses of the 9995, as shown in Figures 21 and 22. When 9995 SE/9990 - is connected to ground the 9995 SE will always use one cycle memory word accesse as shown in Figures 21 and 22.

It should be noted that whenever a two cycle word access is taking place (WORD/BYTE-=1), 9995 SE/9990 - connected to VCC, and address of the word being accessed is in the off-chip memory address space of the TMS 9995) a Hold state request will not be granted between the two consecutive cycles.

Also, whenever 9995 SE/9990 - is connected to VCC and the address of the word or byte being accessed is in the on-chip memory address space of the TMS 9995 the first Wait state of the access is determined by the READY input regardless of whether the Automatic First Wait State Veneration feature has been invoked or inhibited.

99955E/9990- does not affect any non-memory cycles.

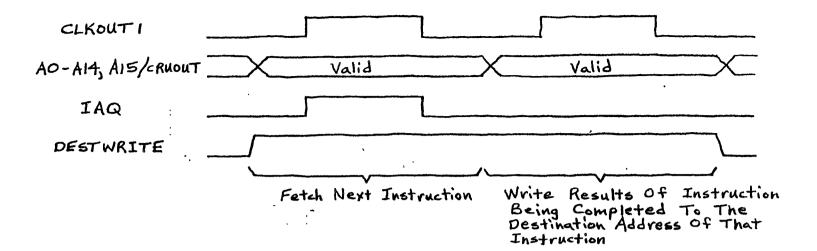

# 2.3.7.2 DESTWRITE Signal

The DESTWRITE output becomes active (high) during an instruction opcode prefetch that occurs when the results of the currently executing instruction have yet to be written to their designated destination address. Timing relationships of this sequence are shown in Figure 23. DESTWRITE is low at all other times.

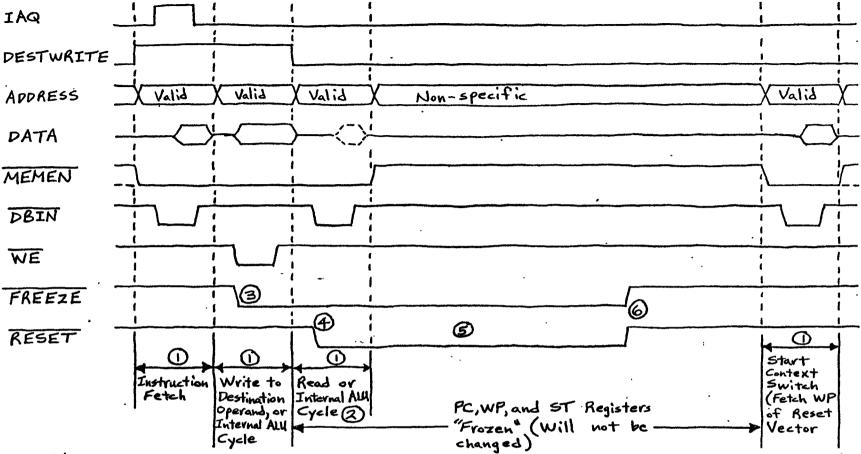

# 2.3.7.3 FREEZE-Signal

The FREEZE-input signal conditions the 9995 SE for an immediately following RESET-. The conditioning consists of ensuring that during the following RESET- the 9995 SE inhibits (beeps at inactive logic level) WE-, DBIN-, MEMEN-, and CRUCLK, and the 9995 SE will not change the contents of its PC, WP, or ST registers. Timing relationships of the FREEZE-signal are shown in Figure 24.

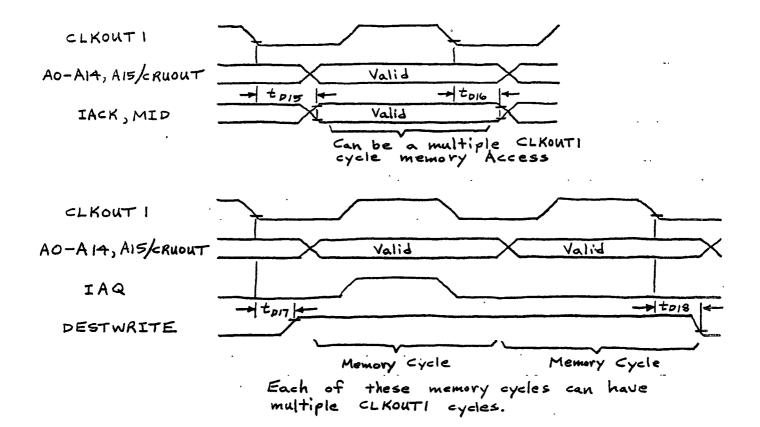

# 2.3.7.4 IACK Signal

The IACK signal provides a means to acknowledge (reset) interrupt stimuli. IACK is active (high) when the 9995 SE is reading the WP of the vector during an interrupt (any interrupt, including RESET, N. I and MID) context switch. IACK is low at all other times. The timing of IACK is exactly the same as AO-AI4 for the memory cycle to which it pertains.

# 2.3.7.5 MID Signal

The MID signal provides a means of setting an externally implemented MID Flag. MID is active (high) when the 9995 SE is reading the WP of the vector during an MID interrupt context switch. MID is low at all other times. The timing of MID is exactly the same as AO-AI4 for the memory cycle to which it pertains.

# 3.0 INSTRUCTION SET

#### 3.1 Definition

Each 9995 SE instruction performs one of the following operations:

- Arithmetic, logical, comparison, or manipulation operations on data

- Loading or storage of internal registers (program counter, workspace pointer, or status)

- Data transfer between memory and external devices via the CRU

- Control functions

#### 3.2 \* Addressing Modes

The 9995 E instructions contain a variety of available modes for addressing random memory data (e.g., program parameters and flags), or formatted memory data (character strings, data lists, etc.). These addressing modes are:

- Workspace Register Addressing

- Workspace Register Indirect Addressing

- Workspace Register Indirect Auto Increment Addressing

- Symbolic (Direct) Addressing

- Indexed Addressing

- Immediate Addressing

- Program Counter Relative Addressing

- CRU Relative Addressing

The following figures graphically describe the derivation of effective address for each addressing mode. The applicability of addressing modes to particular instructions is described in Section 3.5 along with the description of the operations performed by each instruction. The symbols following the names of the addressing modes (R, \*R, \*R+, @LABEL or @TABLE (R) are the general forms used by 1995 SE assemblers to select the addressing modes for register R.

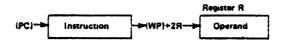

#### 3.2.1 Workspace Register Addressing, R

Workspace Register R contains the operand

The Workspace Register addressing mode is specified by setting the two-bit T-field ( $T_S$  or  $T_D$ ) of the instruction word equal to 00.

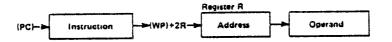

## 3.2.2 Workspace Register Indirect Addressing, \*R

Workspace Register R contains the address of the operand.

The Workspace Register Indirect addressing mode is specified by setting the two-bit T-field (TS or TD) in the instruction word equal to 01.

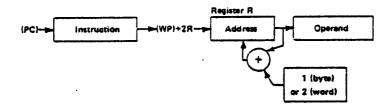

# 3.2.3 Workspace Register Indirect Auto Increment Addressing, \*R+

Workspace Register R contains the address of the operand. After acquiring the address of the operand, the contents of Workspace Register R are incremented.

The Workspace Register Indirect Auto Increment addressing mode is specified by setting the two-bit T-field (TS or TD) in the instruction word equal to 11.

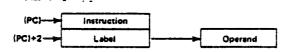

# 3.2.4 Symbolic (Direct) Addressing, @LABEL

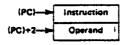

The word following the instruction contains the address of the operand.

The Symbolic addressing mode is specified by setting the two-bit T-field (TS or TD) in the instruction word equal to 10 and setting the corresponding S or D field equal to 0.

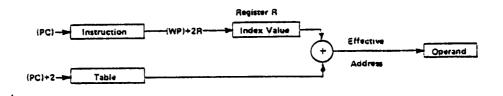

## 3.2.5 Indexed Addressing, @TABLE (R)

The word following the instruction contains the base address. Workspace Register R contains the index value. The sum of the base address and the index value results in the effective address of the operand.

The indexed addressing mode is specified by setting the two-bit T-field ( $T_S$  or  $T_D$ ) of the instruction word equal to 10 and setting the corresponding S or D field not equal to 0. The value in the S or D field is the register which contains the index value.

#### 3.2.6 Immediate Addressing

The word following the instruction contains the operand.

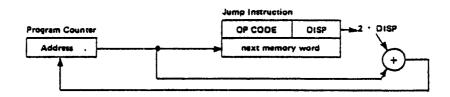

### 3.2.7 Program Counter Relative Addressing

The eight-bit signed displacement in the right byte (bits 8 through 15) of the instruction is multiplied by 2 and added to the updated contents of the program counter. The result is placed in the PC.

#### 3.2.8 CRU Relative Addressing

The eight-bit signed displacement in the right byte of the instruction is added to the CRU base address (bits 0 through 14 of workspace register 12). The result is the CRU address of the selected CRU bit.

#### 3.3 Definition of Terminology

The terminology used in describing the instructions of the 9995 St is defined in Table X 6.

#### 3.4 Status Register Manipulation

Various 7995 SE machine instructions affect the status register. Figure 5 shows the status register bit assignments. Table 1 lists the instructions and their effect on the status register.

#### 3.5 <u>Instructions</u>

# 3.5.1 Dual Operand Instructions with Multiple Addressing for Source and Destination Operand

General 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Format: OP CODE | B | TD | D | TS | S

If B=1, the operands are bytes and the operand addresses are byte addresses. If B=0, the operands are words and the LSB of the operand address is ignored.

The addressing mode for each operand is determined by the T-field of that operand.

| T <sub>S or TD</sub>       | S or D                                | ADDRESSING MODE                                                                                            | NOTES              |

|----------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|

| 00<br>01<br>10<br>10<br>11 | 0,115<br>0,115<br>0<br>1,215<br>0,115 | Workspace register Workspace register indirect Symbolic Indexed Workspace register indirect auto increment | 1<br>4<br>2,4<br>3 |

NOTES: 1. When a workspace register is the operand of a byte instruction (bit 3 = 1), the left byte (bits 0 through 7) is the operand and the right byte (bits 8 through 15) is unchanged.

- 2. Workspace register 0 may not be used for indexing.

- 3. The workspace register is incremented by 1 for byte instructions (bit 3 = 1) and is incremented by 2 for word instructions (bit 3 = 0).

- 4. When TS = TD = 10, two words are required in addition to the instruction word. The first word is the source operand base address and the second word is the destination operand base address.

| MNEMONIC | OP CO |   | COOF |   | 8 |                                | RESULT   | STATUS   |                              |  |

|----------|-------|---|------|---|---|--------------------------------|----------|----------|------------------------------|--|

|          | 0     | ÷ | _    | 2 | 3 | MEANING                        | COMPARED | BITS     | DESCRIPTION                  |  |

|          | 0     | 1 |      | • | ٠ |                                | TO 0     | AFFECTED |                              |  |

| A        | 1     | 0 |      | 1 | 0 | Add                            | Yes      | 0-4      | (SA)+(DA) (DA)               |  |

| AB       | 1     | 0 |      | 1 | 1 | Add bytes                      | Yes      | 0-5      | (SA)+(DA) (DA)               |  |

| С        | 1     | 0 |      | o | 0 | Compare                        | No       | 0-2      | Compare (SA) to (DA) and set |  |

|          |       |   |      |   |   |                                |          | ,        | appropriate status bits      |  |

| св       | 1     | Q | į    | 0 | 1 | Compare bytes                  | No       | 0-2.5    | Compare (SA) to (DA) and set |  |

|          |       |   |      | 1 |   |                                |          | l        | appropriate status bits      |  |

| s        | 0     | 1 |      | 1 | 0 | Subtract                       | Yes      | 0-4      | (DA) - (SA) - (DA)           |  |

| SB       | 0     | 1 |      | 1 | 1 | Subtract bytes                 | Yes      | 0-5      | (DA) - (SA) - (DA)           |  |

| soc      | 1     | 1 |      | 1 | 0 | Set ones corresponding         | Yes      | 0-2      | (DA) OR (SA) - (DA)          |  |

| SOC8     | ١,    | 1 |      | 1 | 1 | Set ones corresponding by tas  | Yes      | 0-2.5    | (DA) OR (SA) → (DA)          |  |

| szc      | 0     | 1 |      | 0 | 0 | Set zeroes corresponding       | Yes      | 0-2      | (DA) AND (SA) - (DA)         |  |

| SZC8     | 0     | 1 |      | Q | 1 | Set zeroes corresponding bytes | Yes      | 0-2.5    | (DA) AND (SA) + (DA)         |  |

| MOV      | 1     | 1 |      | 0 | 0 | Move                           | Yes      | 0-2      | (SA) + (DA)                  |  |

| MOVB     | 1     | 1 |      | o | 1 | Move bytes                     | Yes      | 0-2,5    | (SA) → (DA)                  |  |

3.5.2 <u>Dual Operand Instructions with Multiple Addressing Modes for the Source Operand and Workspace Register Addressing for the Destination</u>

|                 | . 0 | 1 | 2     | 3   | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|-----------------|-----|---|-------|-----|---|---|---|---|---|---|----|----|----|----|----|----|

| General format: |     |   | OP CC | )OE |   |   |   | 0 |   |   | 1  | s  |    |    | 3  |    |

The addressing mode for the source operand is determined by the TS field.

| Ts | s          | ADDRESSING MODE                            | NOTES |

|----|------------|--------------------------------------------|-------|

| 00 | 0, 1, 15   | Workspace register                         |       |

| 01 | 0, 1, 15   | Workspace register indirect                |       |

| 10 | 0          | Symbolic                                   |       |

| 10 | . 1, 2, 15 | indexed                                    | 1     |

| 11 | 0, 1, 15   | Workspace register indirect auto increment | 2     |

NOTES: 1. Workspace register 0 may not be used for indexing.

2. The workspace register is incremented by 2.

| MNEMONIC | OP CODE<br>0 1 2 3 4 5 | MEANING                       | RESULT<br>COMPARED<br>TO 0 | STATUS<br>BITS<br>AFFECTED | DESCRIPTION                                                                                                                                                                                                                                                            |

|----------|------------------------|-------------------------------|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| coc      | 001000                 | Compare ones<br>corresponding | No                         | 2                          | Test (D) to determine if 1's are in each bit position where 1's are in (SA), if so, set ST2.                                                                                                                                                                           |

| czc      | 001001                 | Compare zeros corresponding   | No                         | 2                          | Test (D) to determine if 0's are in each bit position where 1's are in (SA). If so, set ST2.                                                                                                                                                                           |

| XOR      | 001010                 | Exclusive OR                  | Yes                        | 0-2-                       | (D) (SA) + (D)                                                                                                                                                                                                                                                         |

| мрү      | 001110                 | Multiply                      | No                         | •                          | Multiply unsigned (D) by unsigned (SA) and place unsigned 32-bit product in 0 (most significant) and 0+1 (least significant). If WR15 is 0, the next word in memory after WR15 will be used for the least significant half of the product.                             |

| OIV      | 001111                 | Divide                        | No                         | •                          | If unsigned (SA) is less than or equal to unsigned (D), perform no operation and set ST4. Otherwise, divide unsigned (D) and (D+1) by unsigned (SA). Quotient — (D), remainder — (D+1). If D = 15, the next word in memory after WR 15 will be used for the remainder. |

# 3.5.3 Signed Multiply and Divide Instructions

| General | 0 | 1 | 2 | 3 | 4   | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|---|---|---|---|-----|---|---|---|---|---|----|----|----|----|----|----|

| Format: |   |   | 0 | P | COD | Ξ |   |   |   |   | T  | s  |    | S  |    |    |

|         |   |   |   |   |     |   |   |   |   |   |    |    |    |    |    |    |

The addressing mode for the source operand is determined by the TS field.

| $T_{\rm S}$ | S      | ADDRESSING MODE                            | NOTES |

|-------------|--------|--------------------------------------------|-------|

| 00          | 0,1 15 | Workspace register                         | 1     |

| 01          | 0,1 15 | Workspace register indirect                | 1     |

| 10          | 0      | Symbolic                                   | 1     |

| 10          | 1,2 15 | Indexed                                    | 1,2   |

| 11          | 0,1 15 | Workspace register indirect auto increment | 1,3   |

NOTES: 1. Workspace registers 0 and 1 contain operands used in the signed multiply and divide operations.

- 2. Workspace register 0 may not be used for indexing.

- 3. The workspace register is incremented by 2.

| MNEMONIC | OP CODE<br>0123456789 | MEANING            | RESULT<br>COMPARED<br>TO O | STATUS<br>BITS<br>AFFECTED | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----------------------|--------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPYS     | 0000000111            | Signed<br>Multiply | Yes                        | 0 <b>-</b> 2               | Multiply signed two's complement integer in WRO by signed two's complement integer (SA) and place signed 32-bit product in WRO (most significant) and WR1 least significant).                                                                                                                                                                                                                                                                                         |

| DIVS     | 000000110             | Signed             | Yes                        | 0-2,4                      | If the quotient cannot be expressed as a signed 16 bit quantity (8000(hex) is a valid negative number), set ST4.  Otherwise, divide signed, two's com- plement integer in WRO and WR1 by the signed two's comple- ment integer (SA) and place the signed quo- tient in WRO and the signed remainder in WR1. The sign of the quotient is deter- mined by algebraic rules. The sign of the remainder is the same as the sign of the dividend and  REMAINDER  <  DIVISOR |

#### 3.5.4 Extended Operation (XOP) Instruction

| General | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Format: | 0 | 0 | 1 | 0 | 1 | 1 |   |   | D |   | T  | S  |    | S  |    |    |

The TS and S fields provide multiple mode addressing capability for the source operand. When the XOP is executed, the following transfers occur:

After these transfers have been made, ST6 is set to one, and ST7, ST8, ST9, ST10 (Overflow Interrupt Enable), and ST11 are all set to zero.

The 9995 SE does not service interrupt trap requests (except for the Reset and NMI Requests) at the end of the XOP isoptruction.

## 3.5.5 <u>Single Operand Instructions</u>

| General | 0 | 1 | 2 | 3 | 4  | 5   | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |   |

|---------|---|---|---|---|----|-----|---|---|---|---|----|----|----|----|----|----|---|

| Format: |   |   |   |   | OP | COD | E |   |   |   | T  | S  |    | S  |    |    | l |

The TS and S fields provide multiple mode addressing capability for the source operand.

| MNEMONIC | OP CODE<br>0123456789 | MEANING                                    | RESULT<br>COMPARED<br>TO O | STATUS<br>BITS<br>AFFECTED | DESCRIPTION                                                                                                                                                                                                                                       |

|----------|-----------------------|--------------------------------------------|----------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | 0000010001            | Branch                                     | Мо                         |                            | SA→(PC)                                                                                                                                                                                                                                           |

| BL       | 0000011010            | Branch<br>and link                         | No                         |                            | (PC)→(WR11); SA—(PC)                                                                                                                                                                                                                              |

| BLWP     |                       | Branch<br>and load<br>workspace<br>pointer | No                         |                            | (SA)→(WP); (SA+2)—(PC);<br>(old WP)→(new WR13);<br>(old PC)→(new WR14);<br>(old ST)→(new WR15);<br>The 9995 SEdoes not<br>service interrupt trap<br>requests (except for the<br>Reset and NMI Requests)<br>at the end of the BLWP<br>instruction. |

| CLR      | 0000010011            | Clear<br>Operand                           | No                         |                            | 0- <b>&gt;</b> (SA)                                                                                                                                                                                                                               |

| SETO     | 0000011100            | Set to ones                                | No                         |                            | FFFF <sub>16</sub> →(SA)                                                                                                                                                                                                                          |

| INV      | 0000010101            | Invert                                     | Yes                        | 0-2                        | (SA)→(SA)                                                                                                                                                                                                                                         |