Please do not upload this copyright pdf document to any other website. Breach of copyright may result in a criminal conviction.

This pdf document was generated by me Colin Hinson from a Crown copyright document held at R.A.F. Henlow Signals Museum. It is presented here (for free) under the Open Government Licence (O.G.L.) and this pdf version of the document is my copyright (along with the Crown Copyright) in much the same way as a photograph would be.

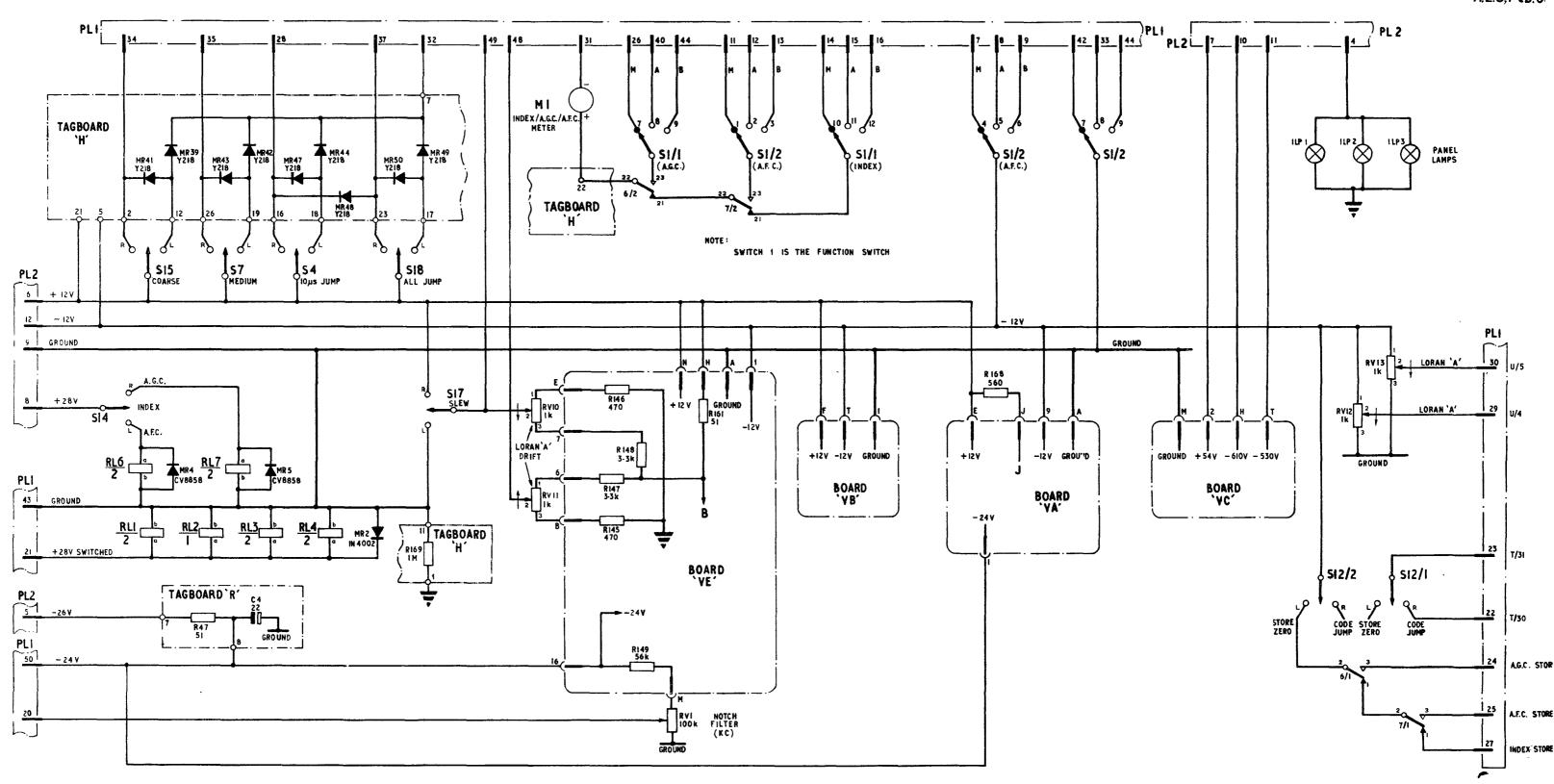

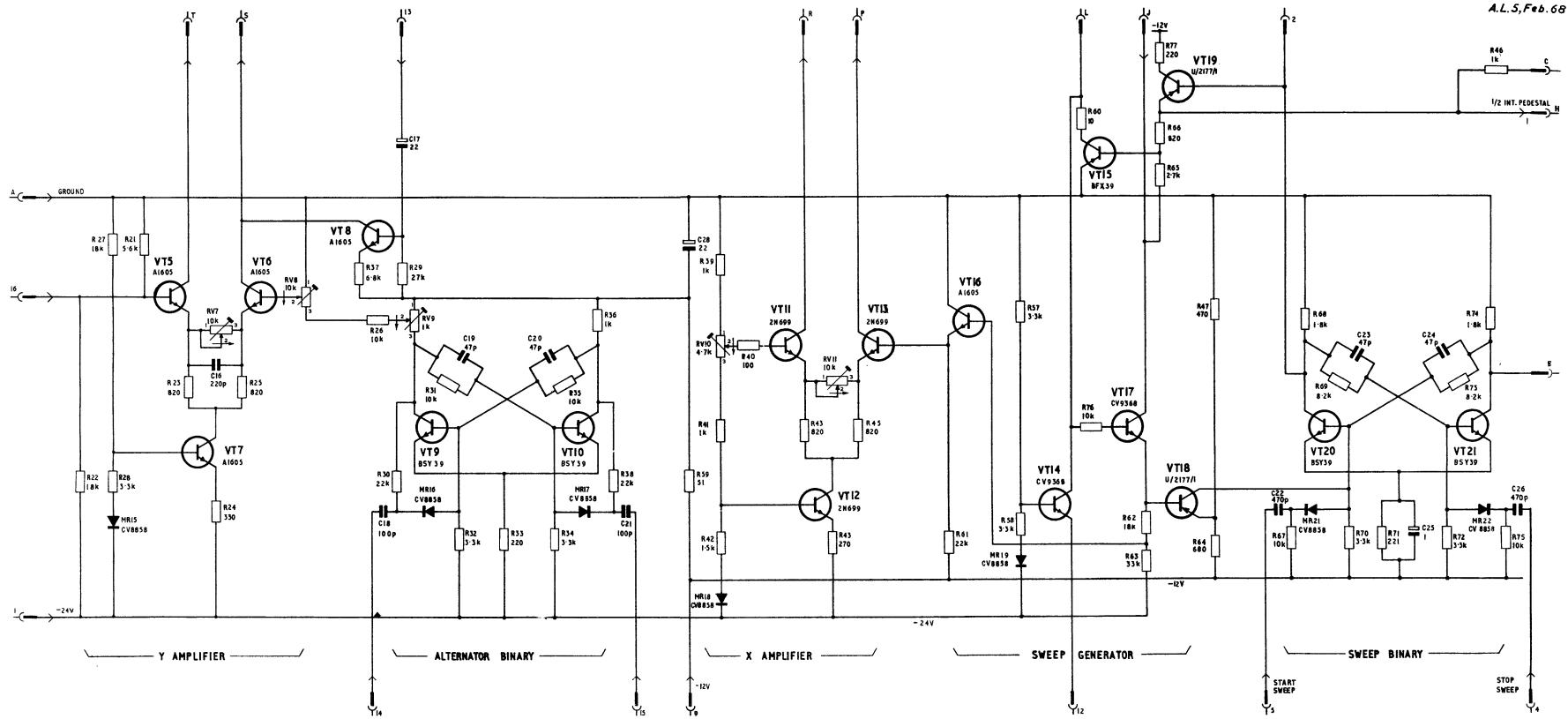

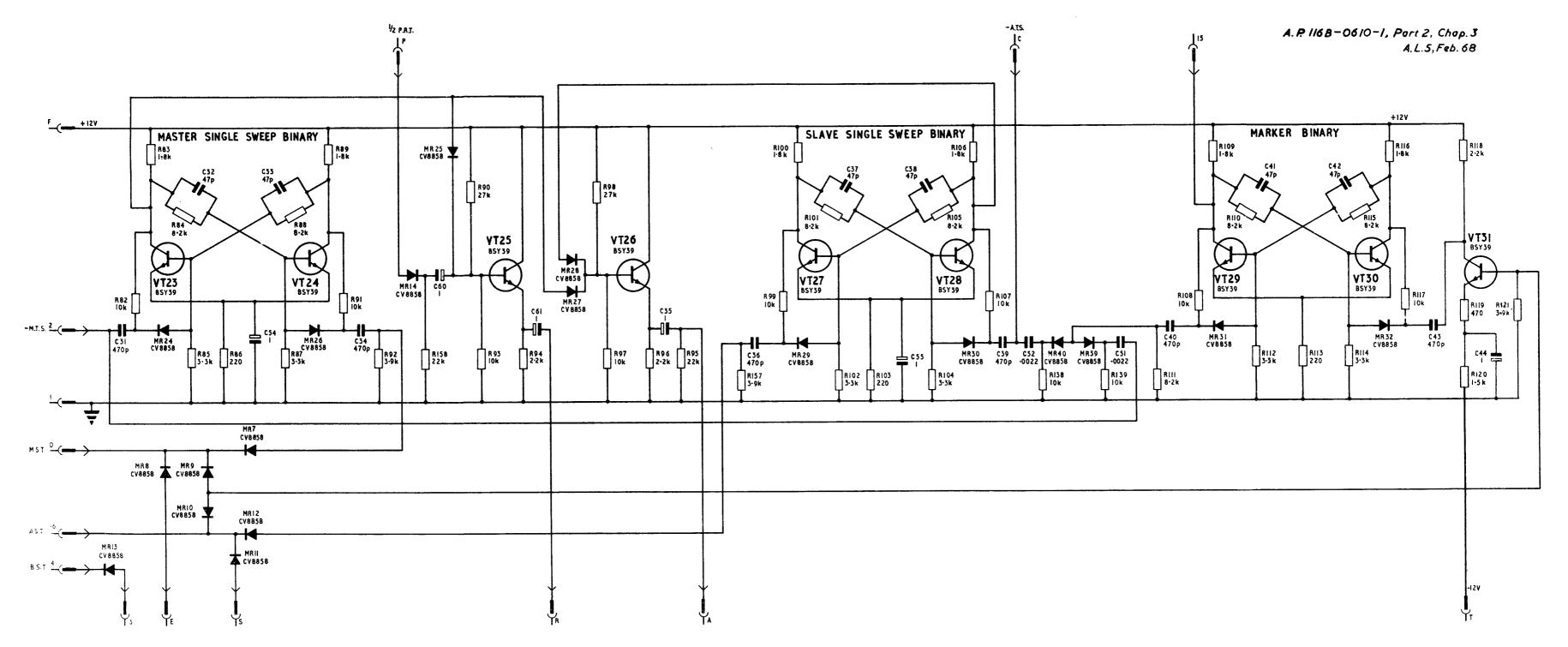

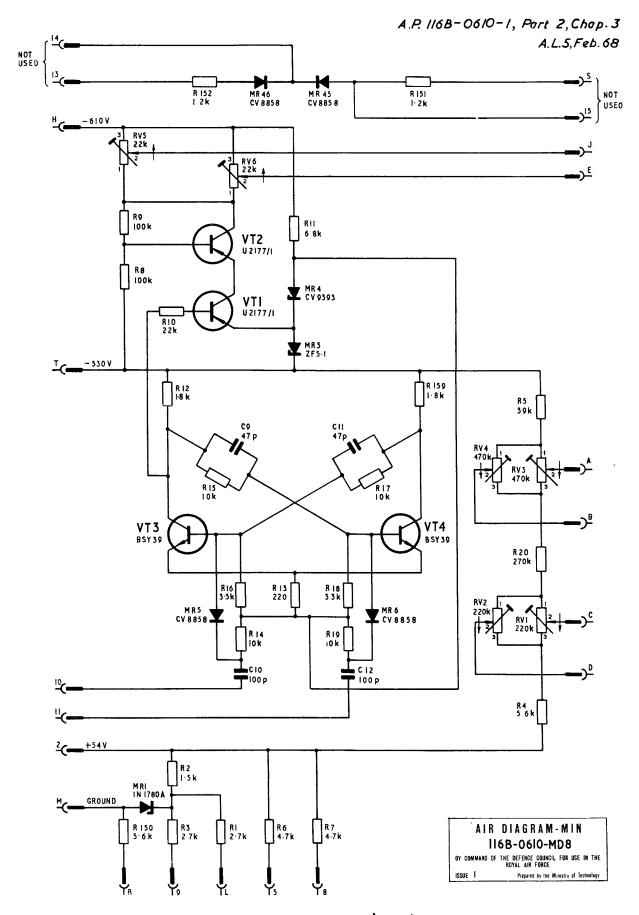

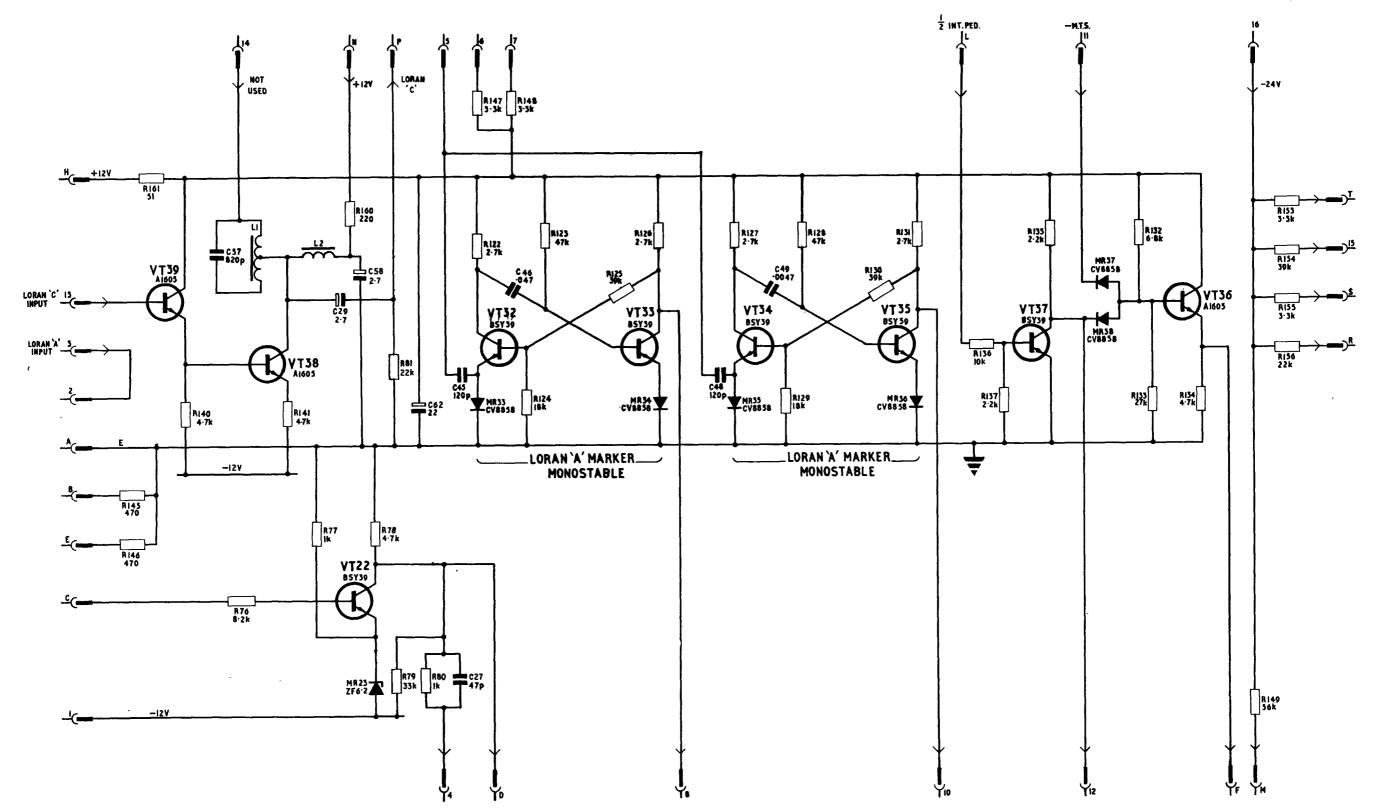

The document should have been downloaded from my website <a href="https://blunham.com/Radar">https://blunham.com/Radar</a>, or any mirror site named on that site. If you downloaded it from elsewhere, please let me know (particularly if you were charged for it). You can contact me via my Genuki email page: <a href="https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin">https://www.genuki.org.uk/big/eng/YKS/various?recipient=colin</a>

You may not copy the file for onward transmission of the data nor attempt to make monetary gain by the use of these files. If you want someone else to have a copy of the file, point them at the website. (<a href="https://blunham.com/Radar">https://blunham.com/Radar</a>). Please do not point them at the file itself as it may move or the site may be updated.

| It should be noted that most of the pages are identifiable as having been processed by me |

|-------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------|

I put a lot of time into producing these files which is why you are met with this page when you open the file.

In order to generate this file, I need to scan the pages, split the double pages and remove any edge marks such as punch holes, clean up the pages, set the relevant pages to be all the same size and alignment. I then run Omnipage (OCR) to generate the searchable text and then generate the pdf file.

Hopefully after all that, I end up with a presentable file. If you find missing pages, pages in the wrong order, anything else wrong with the file or simply want to make a comment, please drop me a line (see above).

It is my hope that you find the file of use to you personally – I know that I would have liked to have found some of these files years ago – they would have saved me a lot of time!

Colin Hinson

In the village of Blunham, Bedfordshire.

# COPY FOR OFFICIAL USE

AIR PUBLICATION

116B-0610-1

# DECCA LORAN C/A TYPE ADL21, RECEIVER ARI. 23180 AND ASSOCIATED TEST EQUIPMENT

GENERAL AND TECHNICAL INFORMATION

BY COMMAND OF THE DEFENCE COUNCIL

17. Dunnitt

Ministry of Defence

FOR USE IN THE ROYAL AIR FORCE

(Prepared by the Ministry of Technology)

Issued Apr. 67

#### NOTE TO READERS

The subject matter of this publication may be affected by Defence Council Instructions, Servicing schedules (Volume 4), or "General Orders and Modifications" leaflets in this A.P., in the associated publications listed below, or even in some others. If possible, Amendment Lists are issued to correct this publication accordingly, but it is not always practicable to do so. When an Instruction, Servicing schedule, or leaflet contradicts any portion of this publication, the instruction, Servicing schedule, or leaflet is to be taken as the overriding authority.

The inclusion of reference to items of equipment does not constitute authority for demanding the items.

Each leaf, except the original issue of preliminaries, bears the date of issue and the number of the Amendment List with which it was issued. New or amended technical matter will be indicated by black triangles positioned in the text thus: — \ to show the extent of amended text, and thus: — \ to show where text has been deleted. When a Part, Section, or Chapter is issued in a completely revised form, the triangles will not appear.

## LIST OF ASSOCIATED PUBLICATIONS

Air Navigation — Manual of Radio Aids

A.P.1234C

◆ Decca Loran C/A Type ADL21 receiver ARI.23180 and associated test equipment: servicing diagrams manual A.P.116B-0610-10 ▶

# CONTENTS OF VOLUME 1

#### **CONTENTS**

#### PRELIMINARY PAGES

Amendment record sheet

Note to readers

List of associated publications

#### PART 1

#### General Information

#### Leading Particulars

#### Chap.

- 1 General principles of Loran C and Loran A.

- 2 General and functional description of ARI.

- 3 Installation and operation of ARI.

#### PART 2

#### **Technical Description**

#### Chap.

- 1 Amplifier, Antenna (Decca Type 1953)

- 2 Receiver, Loran (Decca Type 1831)

- 3 Indicator, Loran (CRT Controller Decca Type 1832)

- 4 Indicator, Digital Display (Read-out unit Decca Type 1833)

#### PART 3

#### Servicing and Fault Diagnosis

## Chap.

- 1 Test set Type 1863

- 2 First line servicing

- 3 Test set Type 1958

- 4 Second line servicing: receiver, Loran (Decca Type 1831)

- 5 Second line servicing: indicator, Loran (Decca CRT controller Type 1832)

- 6 Second line servicing: indicator, digital display (Decca Type 1833)

- 7 Second line servicing: amplifier, antenna (Decca Type 1953)

# PART 1

# **GENERAL INFORMATION**

# LEADING PARTICULARS

| Function            |          |     |     |     | The ARI.23180 is an airborne radio installation employing the Decca Loran Type ADL21 receiver which provides position-fix information derived from the transmissions from any of the currently available chains of Loran C or Loran A stations.  In the Loran C mode, signals are acquired                                             |

|---------------------|----------|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |          |     |     |     | manually, but thereafter, master and slave signals are tracked automatically. Loran A operation is manual.                                                                                                                                                                                                                             |

| Display             | •••      | ••• | ••• |     | A five-digit numerical display provides a direct read out, in microseconds, of the time differences applicable to the selected transmissions. In the Loran C mode, the read-out may be switched to display time difference for either one of two selected master/slave pairs, or to alternate automatically between the two readings . |

|                     |          |     |     |     | A cathode ray tube (CRT) display is provided for signal acquisition and Loran A interpretation.                                                                                                                                                                                                                                        |

| Frequency           |          |     |     |     |                                                                                                                                                                                                                                                                                                                                        |

| Loran C:            | •••      | ••• | ••• | ••• | 100 kc/s                                                                                                                                                                                                                                                                                                                               |

| Loran A:            |          | ••• |     |     | 1850 kc/s<br>1900 kc/s<br>1950 kc/s                                                                                                                                                                                                                                                                                                    |

| Bandwith            |          |     |     |     |                                                                                                                                                                                                                                                                                                                                        |

| Loran C:            | •••      | ••• |     |     | Switch selected, 20 kc/s to 3dB points or 6 kc/s to 3dB points                                                                                                                                                                                                                                                                         |

| Loran A:            | •••      | ••• | ••• | ••• | 40 kc/s to 3dB points                                                                                                                                                                                                                                                                                                                  |

| Sensitivi <b>ty</b> |          |     |     |     |                                                                                                                                                                                                                                                                                                                                        |

| Loran C:            | •••      | ••• | ••• | ••• | The system will continue to track (at the 3rd cycle) down to $1\mu V$ into the antenna amplifier.                                                                                                                                                                                                                                      |

| Loran A:            |          | ••• | ••• | ••• | $20\mu V$ r.m.s. (measured at the peak of the pulse) to provide a useful deflection on the CRT.                                                                                                                                                                                                                                        |

| Signal/Noise to     | lerance  |     |     |     |                                                                                                                                                                                                                                                                                                                                        |

| Loran C:            |          | ••• | ••• |     | Third cycle signal tracking will continue with signal/white noise conditions as poor as 1/10.                                                                                                                                                                                                                                          |

| Loran A:            | •••      | ••• | ••• | ••• | Satisfactory operation will continue at signal/noise ratio of 3/1.                                                                                                                                                                                                                                                                     |

| Normal operatir     | ig range | ?   |     |     |                                                                                                                                                                                                                                                                                                                                        |

| Loran C:            |          | ••• |     |     | 1200 n.m. over sea water (ground wave) 900 n.m. over land (ground wave) 2500 n.m. using skywave.                                                                                                                                                                                                                                       |

| Loran A:            |          |     |     | ••• | 700 n.m. over sea water (ground wave) 150 n.m. over land (ground wave) 1500 n.m. using skywave                                                                                                                                                                                                                                         |

| Probable ac         | curacy                         |                             |                 |                    |          |                                 |                                               |                                              |                      |

|---------------------|--------------------------------|-----------------------------|-----------------|--------------------|----------|---------------------------------|-----------------------------------------------|----------------------------------------------|----------------------|

| Loran (             | C:                             | •••                         |                 | •••                |          | $\frac{1}{2}$ -1 n.             | 00 yd. in goo<br>m. at range o<br>n.m. when u |                                              | d wave)              |

| Loran .             | <b>A</b> :                     | •••                         |                 |                    |          |                                 | m. in good co<br>ı.m. when usir               | ver (ground wa<br>1g skywave.                | ve)                  |

| Antenna             |                                |                             |                 |                    | •••      |                                 | eraft skin and                                | plate which for<br>is unique to e            |                      |

| Power su            | pplies                         |                             |                 |                    |          |                                 |                                               | , 400 c/s, sing<br>28V, d.c. negati          |                      |

| Power co            | nsumpi                         | tion                        |                 |                    |          |                                 |                                               |                                              |                      |

| a.c.                |                                |                             | •••             | •••                |          |                                 |                                               | Normal power                                 | is 45W               |

|                     |                                |                             |                 |                    |          | Maximum<br>is 55W.              | power during                                  | g oven warm-u                                | p period             |

| d.c.                | •••                            | •••                         | •••             | •••                | •••      |                                 | ith lighting do<br>out not exceed             | emand, mode o<br>ling <b>4</b> 2A <b>)</b> . | f opera-             |

| Units of e          | quipm                          | ent                         |                 |                    |          |                                 |                                               |                                              |                      |

| Receive<br>Indicate | er, Lore<br>or, Lor<br>or, Dig | an (De<br>ran (C<br>gital D | RT Co<br>isplay | ontrolle<br>(Read- | r) (Dec  | <br>ca Type 183<br>it) (Decca T | <br>2)<br>ype 1833)                           | 5826-99-9<br>5826-99-9<br>5826-99-9          | 955-8337<br>955-8338 |

| Dimensio            | ne and                         | weioh                       | t c             |                    |          |                                 |                                               |                                              |                      |

| Dingerator          | us unu                         | weign                       |                 |                    |          | Width<br>(in)                   | Depth<br>(in)                                 | Height<br>(in)                               | Weight<br>(lb)       |

| Receive             | er                             |                             |                 | •••                |          | 10.250                          | 22-215                                        | 7.750                                        | 39                   |

| CRT $U$             | Init                           | •••                         | • • • •         |                    |          | 5.750                           | 13.750                                        | 6.000                                        | 8                    |

| Read-o              | ut Uni                         | t                           | •••             | • • •              | •••      | 5.750                           | 5.469                                         | 2.625                                        | 2                    |

| Antenn              | a Am                           | plifier                     | •••             | •••                | •••      | 3.875                           | 6.438                                         | 3.875                                        | 1.5                  |

| Note.—The           | se are                         | maxin                       | num di          | imensio            | ns (i.e. | over knobs                      | , handles or o                                | ther projection.                             | s).                  |

| Special te          | est equ                        | ipmeni                      | t               |                    |          |                                 |                                               |                                              |                      |

| <b>4</b> Test S     | _                              | -                           |                 | pe 186             | 3)       |                                 |                                               | 6625-99-                                     | 107-1415             |

|                     |                                |                             |                 |                    | pe 195   |                                 | •••                                           | 5826-99-                                     |                      |

| _                   | -                              |                             | ecca Ty         |                    |          |                                 | •••                                           | 5826-99-19                                   |                      |

#### Chapter 1

#### GENERAL PRINCIPLES OF LORAN C AND LORAN A

#### LIST OF CONTENTS

|              |           |    |      | P | ara. |                             | P    | ara. |

|--------------|-----------|----|------|---|------|-----------------------------|------|------|

| Loran C      |           |    | <br> |   | 1    | Basic measurement technique | <br> | 14   |

| Principle of | f operati | on | <br> |   | 3    | Loran A                     | <br> | 15   |

#### LIST OF TABLES

|          |                  |                | $\boldsymbol{I}$ | `able |

|----------|------------------|----------------|------------------|-------|

| Loran C: | Pulse repetition | rates          |                  | 1     |

| Loran C: | Phase coding of  | transmissions  |                  | 2     |

| Loran A: | Frequency and    | basic rate cod | ing              | 3     |

#### LIST OF ILLUSTRATIONS

|                                     |        | Fig.  |                                   | Fig.  |

|-------------------------------------|--------|-------|-----------------------------------|-------|

| Loran system configurations         | •••    | <br>1 | Loran C: multipulse time sharing  | <br>4 |

| Time relationship of transmitted si | ignals | <br>2 | Loran C: phase definition         | <br>5 |

| Typical Loran C pulse shape         |        | <br>3 | Typical Loran C pattern numbering | <br>6 |

#### Loran C

- 1. Loran C (Loran with phase-matching or cyclematching) is so termed to distinguish it from the original Loran system, now generally termed Loran A (see, for example, A.P. 1234C, Vol. 3, Sect. 7, Chap. 3). The system stems from efforts to improve the range and accuracy of Loran. Between 1946 and 1951, an experimental system operating on 180 kc/s and 200 kc/s was developed: this was named CYCLAN (Cycle-matching air navigation). In 1952 the basis of the current system was established, employing a 100 kc/s carrier frequency and using both time and phase measurement. This was initially referred to as CYTAC (Cycle-matching tatical navigational system). CYTAC was under field evaluation from 1955 to 1957 after which the system was renamed Loran C.

- 2. The system is similar to Loran A in principle,

being a pulse technique hyperbolic position fixing aid, but it differs in three important respects:—

- (1) A single transmission channel is used based on carrier frequency of 100 kc/s (Loran A uses a group of channels in the band 1800 kc/s to 1950 kc/s).

- (2) A multiple pulse coded transmission sequence is used.

- (3) Both pulse and phase-matching techniques are employed in the receiver.

These changes result in considerably improved range and higher accuracy and permit the use of automatic tracking of signals with continuous or cyclic readout of the time differences. Automatic acquisition of signals, also, is possible with Loran C but this places some restriction on operating range and the facility is not included in the present receiver.

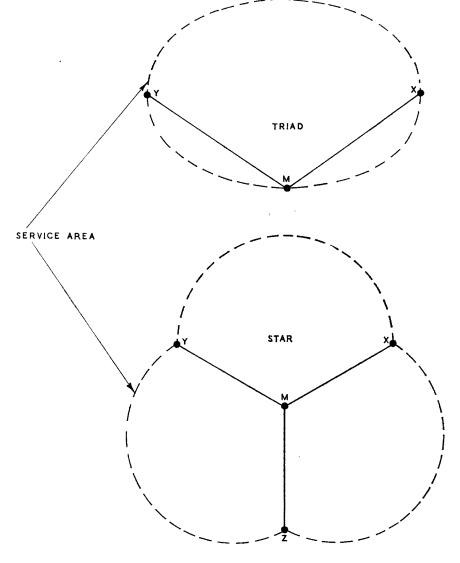

Fig. 1. Loran system configurations

#### Principle of operation

- 3. Fig. 1 illustrates two Loran system configurations. Three to five land-based pulse transmitting stations comprise a Loran C chain and consist of a master (M) and two, three or four slave stations (X, Y, Z and W). When two slave stations are employed the chain is called a triad. When three or four slaves are used, it is known as a star. The precisely timed pulse transmissions from all stations are made on a time shared basis, utilizing the common carrier frequency of 100 kc/s. The transmissions occupy a spectrum of 20 kc/s, 99% of the radiated energy lying within the band 90 kc/s to 110 kc/s.

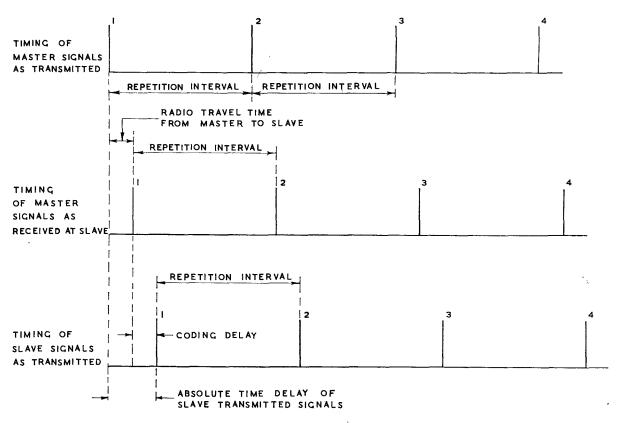

- 4. The transmissions propagated from the master station are received at a slave station and at the receiving set in the service area. The slave station delays by a precise time interval known as the coding delay and then transmits its own signal.

- 5. Figure 2 illustrates time relationships between transmitted signals. A receiver in the service area will receive the pulses from the slave station delayed in time from the master by an amount depending upon both the location of the receiver and the coding delay indicated in fig. 2. Since the receiver is at a constant time difference with respect to the two stations, the time difference between the reception of pulses from them establishes hyperbolic contours with the two stations as foci. A second slave station performing the same function as the first slave also generates a family of hyperbolic contours. The receiver establishes the difference in time of the two slave signals relative to the master thus creating two hyperbolic contours, the intersection of which defines the location of the receiver.

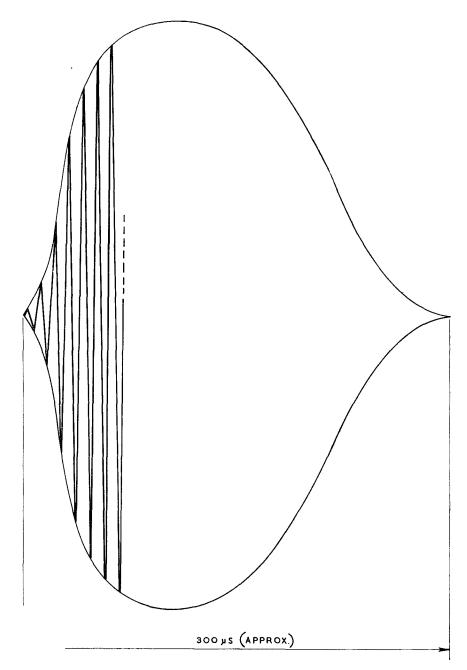

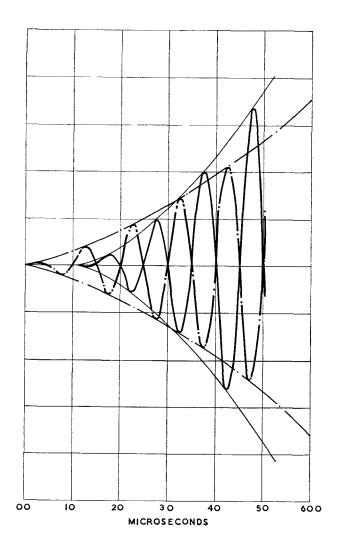

- 6. The Loran transmitted pulse (fig. 3) is approximately  $300\mu S$  in duration and rises to greater than 90% of its maximum amplitude within  $70\mu S$ . At about  $30\mu S$ , from the com-

Fig. 2. Time relationship of transmitted signals

mencement of the pulse the signal amplitude is approximately 60% of the peak amplitude. This point is chosen as the latest point at which measurements in the receiver (phase sampling) can be made, before contamination from the first hop sky waves can occur. Normal or ground wave Loran signal measurements are thus referred to a point  $30\mu$ S from the start of the signal.

- 7. The low basic frequency of the system allows the ground wave propagational path to follow the curvature of the earth. The same transmissions reflect off the ionosphere and the sky waves thus formed, depending upon the height of the ionosphere and the distance of the user from the transmitting station, appear at the receiver some time after the reception of the ground wave signals. However, the sampling of a given pulse in the receiver occurs before the earliest possible arrival time of the skywave. This enables positional accuracy of the order of  $0.1\mu S$  to be obtained continuously within the groundwave coverage area. This accuracy is obtained through the use of coherent detection techniques for measuring the phase of the received pulse and techniques for determining the fixed reference point on the leading edge of the pulse irrespective of pulse amplitude.

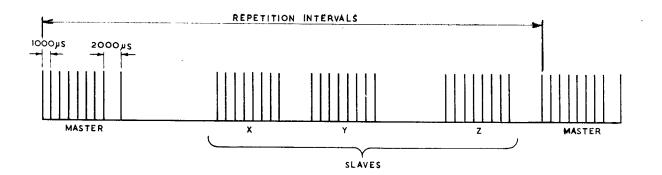

- **8.** Figure 4 illustrates the multipulse time sharing. The coding delays at the slave stations are so arranged that a receiver placed anywhere within the service area will always receive the master transmissions first, followed in order by the X, Y and Z slaves. The master station transmits a burst of eight pulses each approximately 300µS long spaced 1mS apart (followed by a ninth pulse 2mS later, which is used for identification and fault signalling). The X slave is the next to transmit, followed in turn by the Y and then the Z slave if incorporated in the chain. (A fourth slave, the W slave, may also be incorporated). Each slave sends eight pulses. The time which elapses between the initiating pulse transmission from the master station and the next initiating pulse transmission from the same station is known as the repetition interval.

- 9. Since the whole of the Loran C system operates on a single 100 kc/s carrier frequency, identification of a particular chain must be provided by some means other than r.f. channel selection. This identification is achieved by the use of 48 different pulse repetition rates. All the stations in a particular chain use the same pulse repetition rate but a different rate must be used for each chain. The 48 pulse repetition rates are

Fig. 3. Typical Loran C pulse shape

selected from six basic rates designated by letters H, L, S, SH, SL & SS. These designations correspond with group repetition intervals of 30,000, 40,000, 50,000, 60,000, 80,000 and  $100,000\mu$ S. In addition for each of these basic rates there are eight specific rates, 0, 1, 2, 3, 4, 5, 6 and 7. To obtain the repetition rate, 0, 100, 200, 300, 400, 500, 600 or  $700\mu$ S is subtracted from the basic rate according to whether the specific rate code is 0 to 7 respectively, each digit representing  $100\mu$ S.

10. In order to provide both an automatic search capability and some measures of skywave

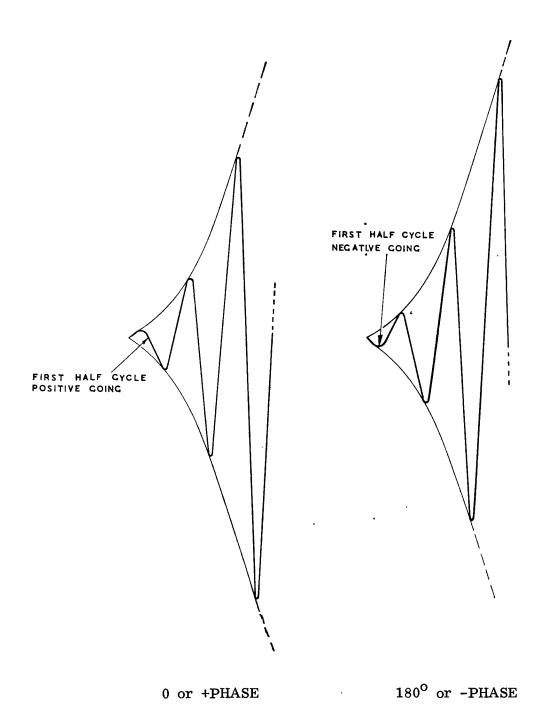

rejection, the pulses are phase coded. The phase of the r.f. carrier relative to the pulse envelope is given one of two values. When the first half cycle of the carrier is positive going the coding is said to be positive. When the first half cycle of the carrier is negative going the coding is negative. The r.f. within the envelope of the negative phase coded pulse is 180° out of phase with the r.f. of a positive coded pulse. These phase definitions are illustrated in fig. 5.

11. The phase-coding of master and slave stations is given in Table 2. The master transmits alternately two types of coding, M1 and M2

respectively. Similarly the slaves all transmit a phase code identical to each other but use two coding patterns S1 and S2. Thus one repetition interval will consist of M1, S1 (X), S1 (Y), S1 (Z) followed in the next repetition interval by M2, S2 (X), S2 (Y), S2 (Z). The whole sequence then repeats. On a four-slave chain, Slave W precedes X.

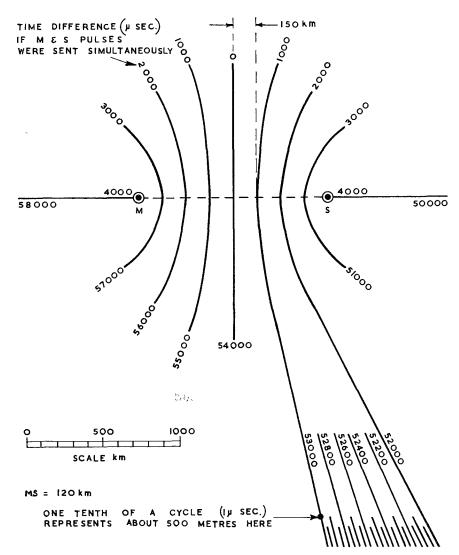

- 12. The generation of a Loran pattern by the transmissions from a master and slave station is shown in fig 6 with a typical baseline length of 1200 km and to clarify this description the upper half of the hyperbolic pattern is annotated with the master/slave time differences in  $\mu s$  that would exist were the pulses transmitted simultaneously. The time difference would then be zero on the baseline bisector, rising to -4000 $\mu s$  (master advance on slave) on the master baseline extension and to +4000 $\mu s$  (slave advance on master) on the slave baseline extension. A total range of time difference of 8000 $\mu s$  is thus represented by this pattern.

- 13. If an absolute time delay (fig 2) of more than  $4000\mu s$  is introduced into the slave transmission the master pulse will always be received before the slave pulse. The lower half of fig 6 indicates the actual pattern numbering that would be used with a cooling delay of  $46,000\mu s$  (absolute time delay being  $50,000\mu s$ ). The interpolated figures show the  $100\mu s$  intervals which are usually adopted for Loran C charts and the  $50\mu s$  sub-divisions that may also be used. The  $100\mu s$  intervals each represent 15 km on the baseline. The appropriate time-delay readout of the receiver is directly referred to the chart to establish the aircraft position on a hyperbola within that pattern. The readout corresponding with the second slave transmission is similarly referred to the pattern generated by that slave in conjunction with the master and the fix is unambiguously established by the intersection of the two hyperbolae so defined.

Fig. 4 Loran C: multipulse time sharing

#### Basic measurement techniques

14. The primary stage in time measurements on Loran C is similar to that of Loran A. Gates (in the present instance, groups of gates) are aligned with the received pulse groups to establish the coarse time measurement. The second stage, known as 'indexing' consists of aligning the gates, derived from the output of an internal 100 kHz pulse generator, with the 3rd cycle of the received master and slave pulses (ie at the 30ms sampling point defined in para 6). The accurate time measurements are then made by automatic counting of the 100 kHz pulse train between master and slave gating points. The time difference is then read directly in microseconds on the Read-out Unit display.

#### LORAN A

- 15. Loran A is fundamentally similar to Loran C but it operates from 1850 kHz to 1950 kHz with only basic pulse time measurement. The signals are transmitted on one of three frequencies in that band, coded by channel number, and on one of three basic pulse recurrence rates (Table 3). The latter are further augmented by 8 specific recurrence rates 0 to 7 which have the same significance as with Loran C (para 9), the digits 0 to 7 representing successive reductions in recurrence interval of 0 to 700µs in 100µs decrements. For example 2S6 represents transmissions on 1850 kHz with a recurrence frequency of 20 Hz (50,000µs interval) less 600µs or an actual interval of 49,400µs.

- 16. Individual measurements must be made on each Master:Slave pair of transmissions to obtain a fix and the automatic tracking facility cannot be employed. The received signals are identified on the double-trace oscilloscope display of the receiver and the time measurement, in the present receiver, is effected by first aligning two gate waveforms (termed 'pedestals') with the two displayed pulses and then adjusting the display to bring both gated pulses into visual coincidence. The time difference may then be read directly in microseconds from the digital readout of the receiver. This operation must then be repeated for the master and the second slave to obtain a position fix.

Fig.5 Loran C: phase definition

Fig. 6. Typical Loran C pattern numbering

TABLE 1

Loran C: Pulse repetition rates

|               | Pu      | lse repetition       | n rates (Mic | roseconds) |        |        |  |  |  |  |

|---------------|---------|----------------------|--------------|------------|--------|--------|--|--|--|--|

| Specific rate |         | Basic rate selection |              |            |        |        |  |  |  |  |

| selection     | SS      | SL                   | SH           | S          | L      | Н      |  |  |  |  |

| 0             | 100,000 | 80,000               | 60,000       | 50,000     | 40,000 | 30,000 |  |  |  |  |

| 1             | 99,900  | 79,900               | 59,900       | 49,900     | 39,900 | 29,900 |  |  |  |  |

| 2             | 99,800  | 79,800               | 59,800       | 49,800     | 39,800 | 29,800 |  |  |  |  |

| 3             | 99,700  | 79,700               | 59,700       | 49,700     | 39,700 | 29,700 |  |  |  |  |

| 4             | 99,600  | 79,600               | 59,600       | 49,600     | 39,600 | 29,600 |  |  |  |  |

| 5             | 99,500  | 79,500               | 59,500       | 49,500     | 39,500 | 29,500 |  |  |  |  |

| 6             | 99,400  | 79,400               | 59,400       | 49,400     | 39,400 | 29,400 |  |  |  |  |

| 7             | 99,300  | 79,300               | 59,300       | 49,300     | 39,300 | 29,300 |  |  |  |  |

TABLE 2

Loran C: Phase coding of transmissions

| Interval | Master                                                                                                           | Slave<br>X, Y, Z All identical                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 1        | M1 + + + - + -                                                                                                   | S1 ++++++                                                                                            |

| 2        | M2 + + + + + + +                                                                                                 | \$2 + - + - + +                                                                                      |

| 3        | M1 + + + - + -                                                                                                   | S1 + + + + + +                                                                                       |

| 4        | M2 + + + + + +                                                                                                   | S2 + - + - + +                                                                                       |

| 5        | All master signals repeat as interval 1, 3, etc. for odd intervals and as interval 2, 4 etc. for even intervals. | All slaves repeat as interval 1, 3, etc. for odd intervals and as interval 2, 4, for even intervals. |

TABLE 3

Loran A: Frequency and basic rate coding

| Code      | Frequency           | Interval  |

|-----------|---------------------|-----------|

| CHANNEL 1 | 1950 kc/s           |           |

| CHANNEL 2 | 1850 kc/s           |           |

| CHANNEL 3 | 1900 kc/s           |           |

| P.R.F. S  | 20 c/s              | 50,000 μS |

| P.R.F. L  | 25 c/s              | 40,000 μS |

| P.R.F. H  | $33\frac{1}{3}$ c/s | 30,000 μS |

#### Chapter 2

#### GENERAL AND FUNCTIONAL DESCRIPTION OF ARI.

#### LIST OF CONTENTS

|                            |      | P | ara. |                      |      | P | ara. |

|----------------------------|------|---|------|----------------------|------|---|------|

| Units of equipment         | <br> |   | 1    | Outline of operation | <br> |   | 6    |

| Brief description of units | <br> |   | 2    | Loran A operation    | <br> |   | 22   |

#### LIST OF ILLUSTRATIONS

|             |                        |          |       |     | Fig. |

|-------------|------------------------|----------|-------|-----|------|

| Index deriv | ation <mark>a</mark> n | d gating |       |     | 1    |

| Functional  | block                  | diagram  | Loran | C/A |      |

| receiver    |                        |          |       |     | 2    |

#### Units of Equipment

- 1. ARI.23180 comprises four major units:—

- (1) Receiver, Decca Type 1831 (Receiver, Loran 5826-99-955-8336)

- (2) CRT Unit, Decca Type 1832 (Indicator, Loran 5826-99-955-8337)

- (3) Read-out Unit, Decca Type 1833 (Indicator, Digital Display 5826-99-955-8338)

- (4) Aerial Amplifier, Decca Type 1953 (Amplifier, Antenna 5826-99-955-8339)

#### **Brief Description of units**

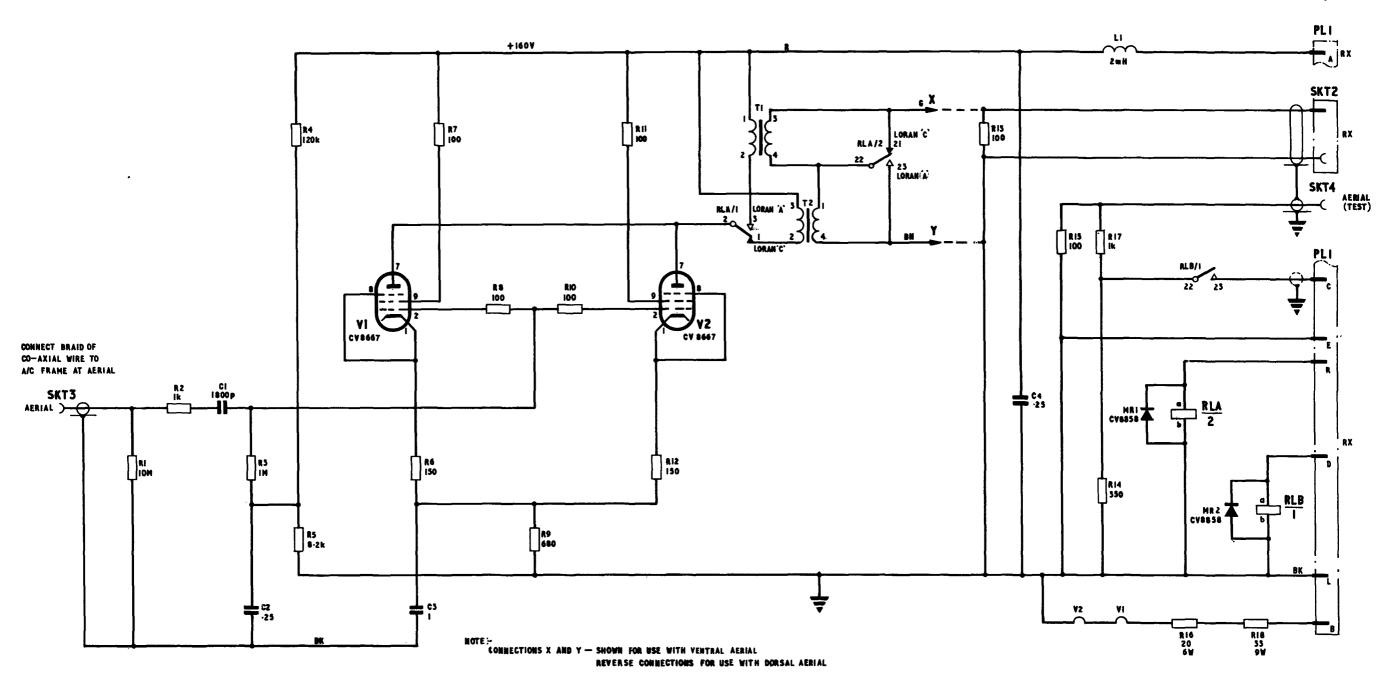

2. The Aerial Amplifier Type 1953 is a two-valve unit mounted adjacent to the aerial. The primary function of this unit is to isolate the aerial which represents a high impedance source, from the necessarily long and high capacitance feeder to the receiver. The amplifier provides a useful gain of the order of 6. Essential features are a low capacitance, high resistance input, low noise factor and low output impedance, the absence of phase distortion within the frequency bands 70-130 kc/s (Loran C) and 1.8 Mc/s to approximately 2.5 Mc/s (Loran A) and good linearity up to inputs greatly in excess of normal

- operating level. These characteristics ensure a high signal to noise ratio with minimum phase error within the Loran frequency bands, and permit operation in the presence of high level signals at other frequencies without appreciable harmonic or cross-modulation interference appearing on the wanted signal.

- 3. The Receiver Type 1831 incorporates all the circuitry necessary for the processing of the received Loran C and Loran A signals, together with the power supply circuits for the receiver and the other three units. There are no operator controls on the receiver, thus it may be mounted remote from the control/display units.

- 4. The CRT Unit Type 1832 houses the cathode ray tube and all the controls necessary for an operator to adjust the display. The function of the unit is to provide a visual display of the received Loran signals together with their selected comparison or tracking gates. A meter on this unit enables the index channel, the a.g.c. channel and the a.f.c. channel sampling voltages to be verified.

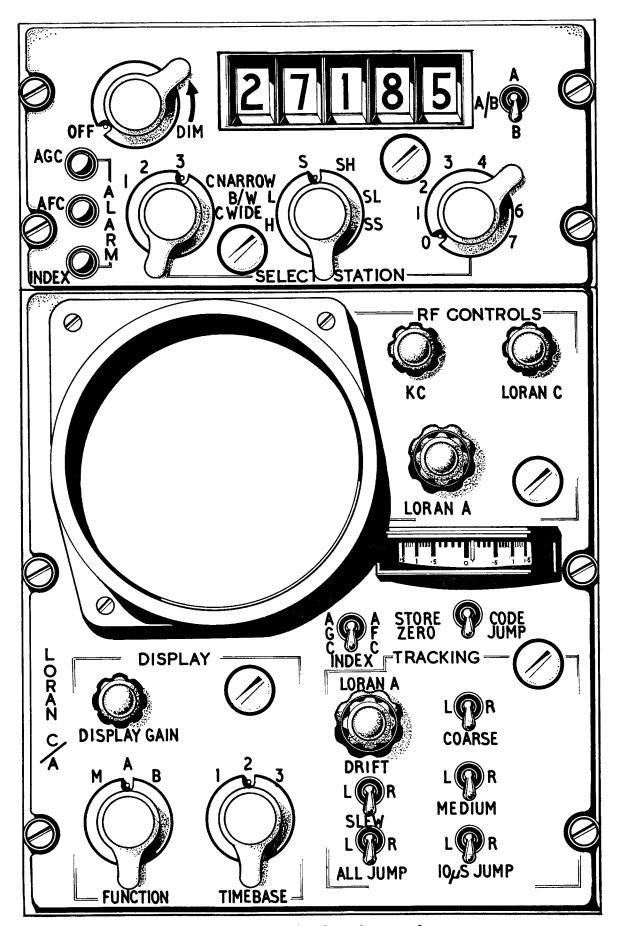

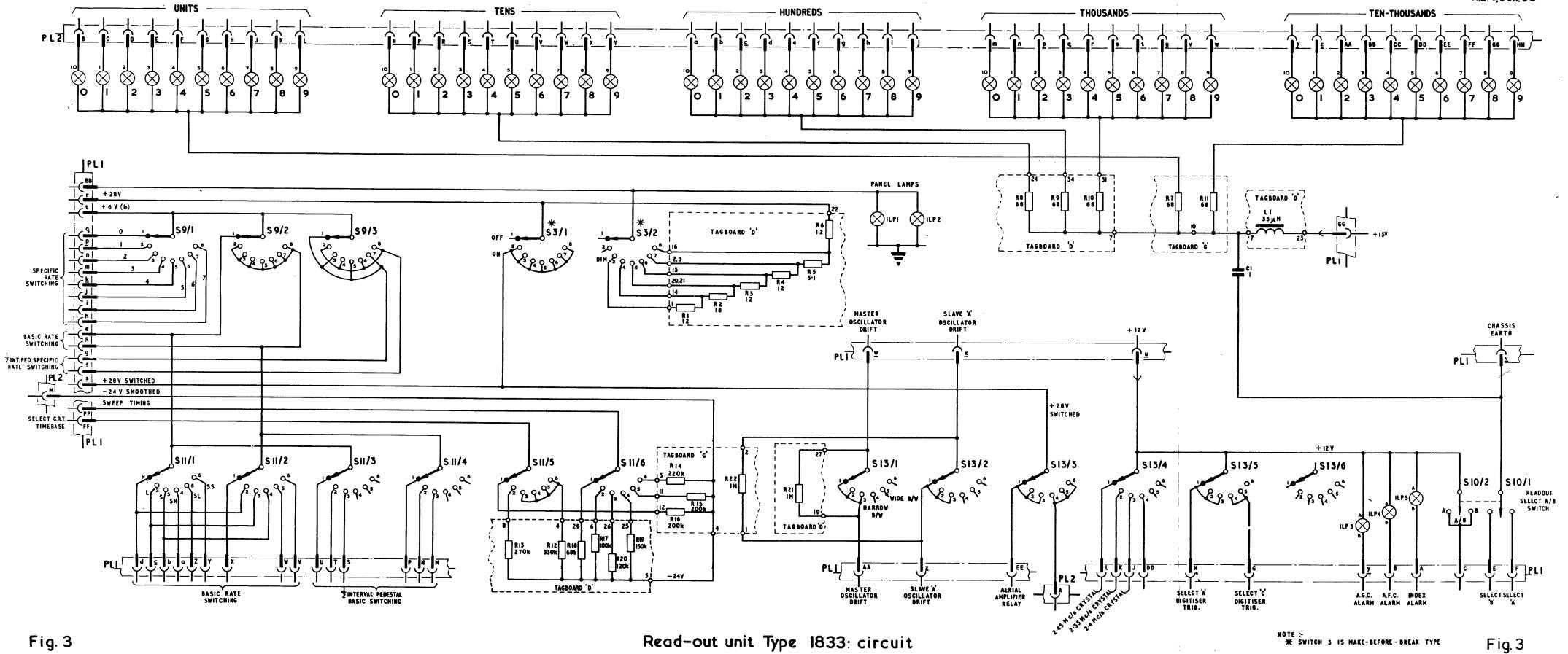

- 5. The Read-out Unit Type 1833 indicates the time difference in microseconds between the master pulses and selected slave pulses. This measurement is displayed on a five-digit read-out. Also on this unit are the alarm lights, a dimmer

control for the display, and switches to select the basic mode of operation and chain pulse-repetition rate. The switch to the right of the display selects display of slave 'A' or slave 'B' measurement, or automatic display of slave 'A' and slave 'B' measurements alternately. These identities 'A' and 'B' are used throughout the receiver as either measuring channel may be operationally used for any one of the X, Y, Z and/or W slave inputs.

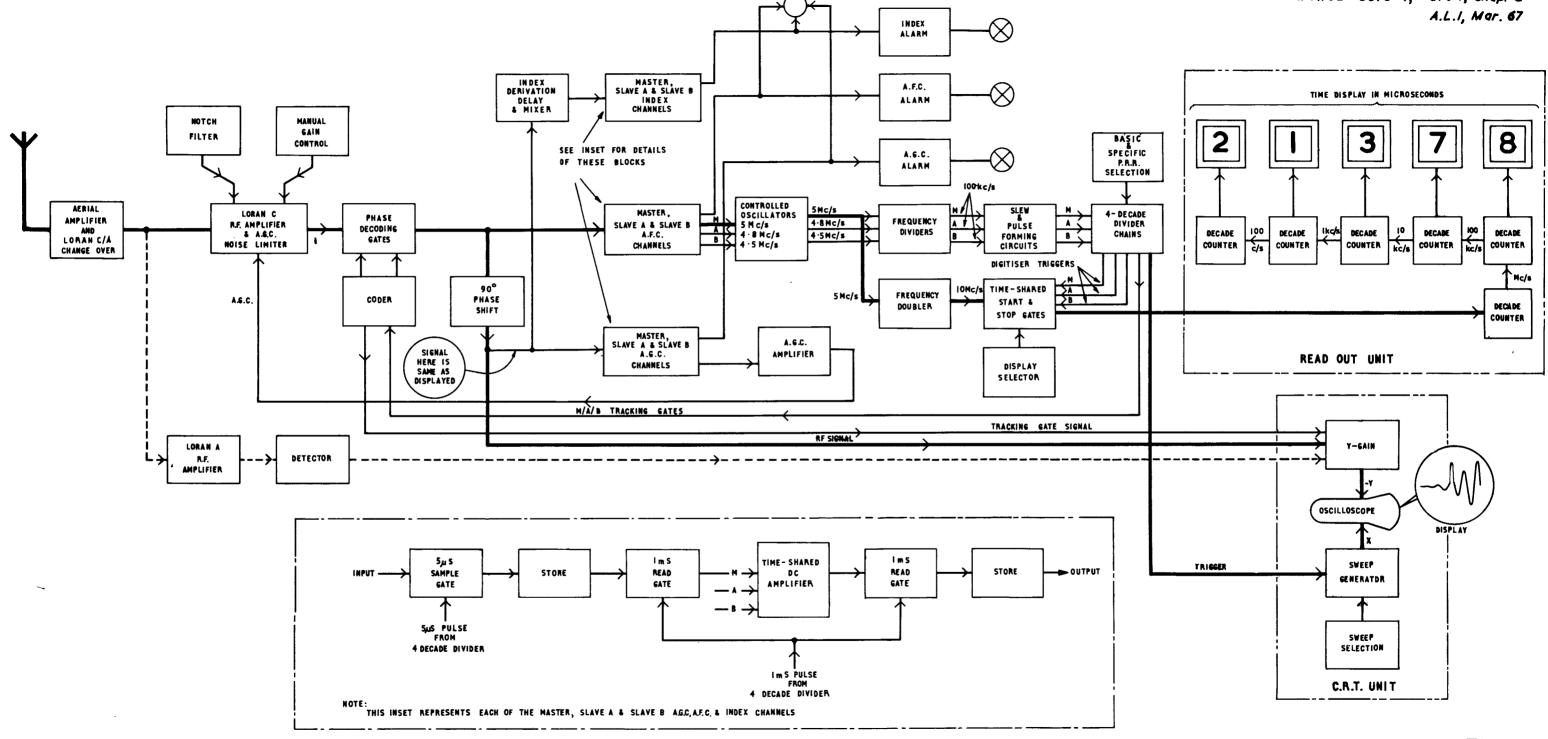

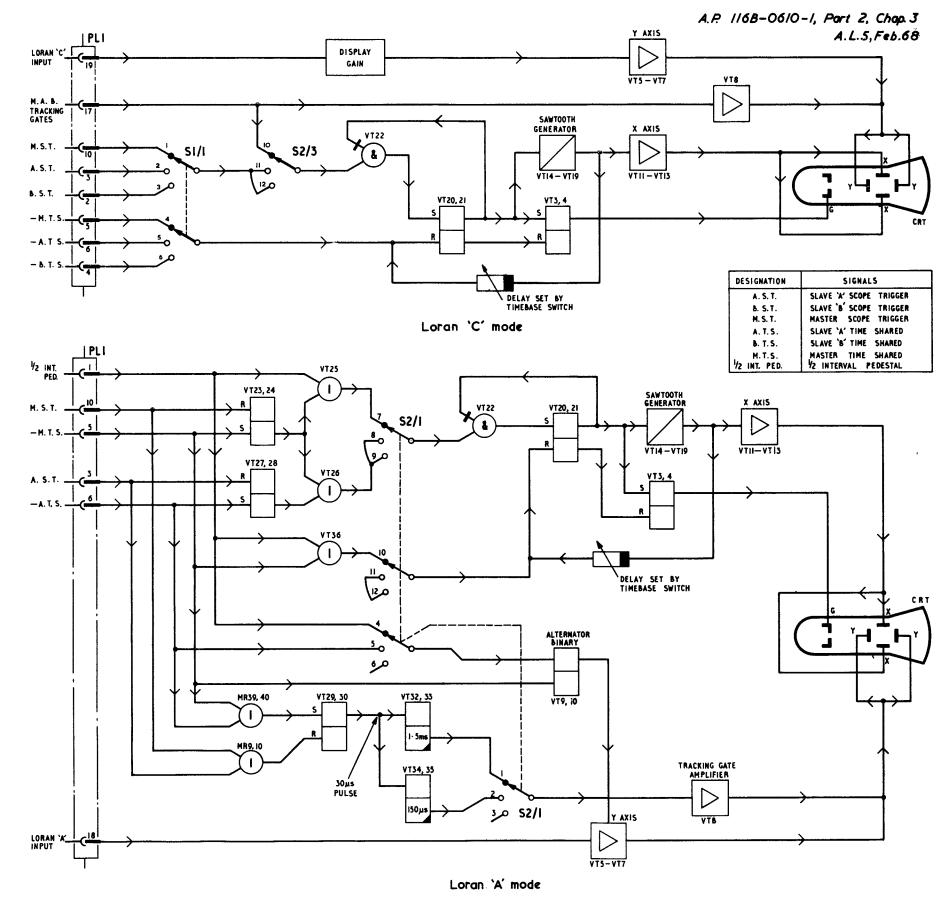

#### Outline of operation (fig. 1, 2)

- 6. The following paragraphs describe the functional operation of the ADL21 equipment. Reference should be made to the functional block diagram (fig. 2). This description follows the primary (Loran C) function of the installation. Changes in the mode of operation for Loran A use are outlined in para. 22.

- 7. A radio-frequency amplifier accepts the lowlevel input signal from the aerial amplifier and amplifies it to a level suitable for the signal sampling process, and for the oscilloscope display in the c.r.t. unit, Type 1832. The r.f. amplifier output is controlled by two a.g.c. detectors which maintain the signal level during tracking of the pulsed signals at 0.4 volts and, where the received signals are extremely weak, limit the r.m.s. signalplus-noise output level to less than 10 volts to avoid non-linearities associated with overdriving the amplifier or gating circuits which follow. The specified output of the r.f. amplifier is maintained over an input range of 2 microvolts to approximately 0.5 volts. A manual gain control is used to adjust the gain prior to acquisition when timegated samples of each signal level are not available to the a.g.c. loops.

- 8. Two types of filtering are accomplished within the r.f. amplifier:

- (1) Bandpass filtering around the 100 kc/s carrier frequency is manually switched, with 3 dB bandwidths of either 30 or 6 kc/s. The former is sufficiently wide to avoid distortion of the leading edge of the pulse during tracking, while the latter provides improved signal-to-noise to assist signal acquisition.

- (2) A notch filter is provided to reject interfering signals. This is tuned manually over a range of 72 to 125 kc/s using the c.r.t. display to measure their effect.

- 9. The output of the r.f. amplifier is presented, via a 90° phase shift circuit and a manually-adjustable Y gain control, on the Y-axis of the c.r.t. display. This display, when properly synchronised by other circuits and controls, enables manual signal acquisition and monitors signal tracking after acquisition.

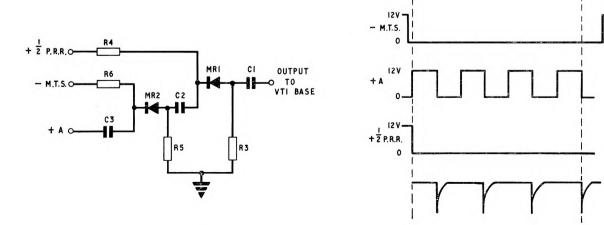

- 10. A phase-code generator (the coder) uses timing signals developed in the master and slave divider chains (para. 13) to position a flip-flop

to the binary states corresponding to the phase-codes of the transmitted signals (Chap. 1, Table 2). This coding, as described in Chap. 1, is intended to permit rejection of multi-hop skywave contamination and consists of 180-degree phase reversals of the transmitted carrier. These are removed prior to signal sampling and integration by applying the coder output to a pair of phase decoding gates which select either the real or inverted phase of the r.f. amplifier output according to the state of the output flip-flop in the phase-code generator.

- 11. The filtered and decoded r.f. signal is applied to three sets of three sampling and filtering channels:—

- (1) The a.f.c. channels detect phase deviations in each of the three signals and provide the appropriate control voltages for phase-locking three local oscillators to the filtered signals received from the three transmitters.

- (2) The a.g.c. channels detect amplitude deviations in each of the three signals and provide the appropriate automatic gain control waveforms for adjusting r.f. amplifier gain sequentially to the level of each of the received signals.

- (3) The index channels measure the phase relation between the signal sampling point and the envelope of the appropriate received pulse. This measurement enables resolution of the 10-microsecond ambiguity otherwise associated with the 100 kc/s phase measurement in the a.f.c. channel, and permits adjustment of the signal sampling point sufficiently early on in the pulse to avoid skywave contamination (i.e. normally at the 3rd cycle).

- **12.** Filtering of the time difference measurements on the incoming signals is accomplished by phase-locking separate oscillators to each of the three signals. These oscillators employ crystals in a temperature-controlled environment to provide long-term frequency stability of the order of 5 parts in 10<sup>7</sup>. To avoid "cross-talk" between the three channels, the oscillators operate on different harmonics of 100 kc/s, viz. 5·0, 4·8 and 4·5 Mc/s. Analogue frequency division by 50, 48 and 45, respectively, then converts each to the required 100 kc/s carrier frequency.

- 13. The 100 kc/s outputs of the frequency dividers are then applied to separate decade dividers which count the pulse-repetition interval and are automatically reset at a count corresponding to the manually selected pulse repetition rate for the desired chain. The three oscillator-divider systems are referred to as Master, A and B clocks. The current logic of each decade divider is decoded to provide five time-related trigger signals.

- (1) 1 mS tracking gate pulses: these control the phase decoding of the received signals via the coder (para. 10) and are also applied via

the coder, to the c.r.t. to provide visual indication of gate alignment with the incoming signals during acquisition.

- (2) 5 microsecond pulse: this opens the gates which sample the incoming signal in the a.f.c., a.g.c. and index channels described above.

- (3) 1 mS read pulses: these connect a time-shared d.c. amplifier between master and slave transmissions, to update stored analogue outputs of the three channels according to the latest information available from the input stores. Phase errors which might result from unbalance or drift are eliminated by use of a time-shared amplifier as the same phase offset occurs in the master and both slave oscillator channels, and the time-difference measurement is thus unaffected.

- (4) A trigger applied to the c.r.t. sweep generator.

- (5) A digitizing trigger: this defines the phase of each clock to the decade counters which provide the output time-difference readings.

- 14. The stored output of each a.f.c. channel gated by the 1mS pulse is applied to a variable-capacitance diode to pull the frequency of the corresponding local oscillator until the 5 microsecond sampling gate generated by its divider chain is centered about the zero crossover of the incoming r.f. signal, completing the phase-locking loop.

- 15. The a.g.c. channels operate in a similar manner using the same 5 microsecond gating pulses, except that the r.f. input is shifted 90 degrees, so that, when the a.f.c. loop has phase-locked the local oscillator establishing automatic tracking, the output of the a.g.c. channel will be at maximum and thus it will be proportional to the amplitude of the r.f. amplifier output. The stored outputs of the three a.g.c. channels are combined to form a time-shared gain control waveform which is applied to the r.f. amplifier to control the input levels to the sampling gates for each of the three signals.

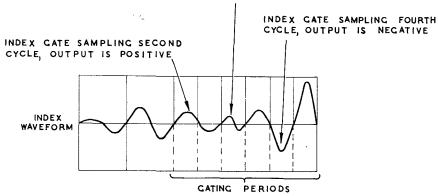

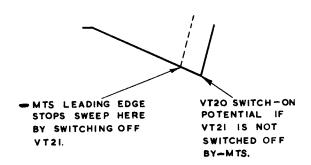

- 16. The index channels again operate in a similar manner gated by the same 5 microsecond pulses but the input r.f. signal passes through the index derivation/mixer circuit so that the waveform may be adjusted to have a zero crossover at any desired point on the r.f. pulse. This derivation is illustrated in fig. 1. The 90° shifted signal, used as an input to the a.g.c. channel, is delayed 10 microseconds and added to a selected portion of the undelayed signal in an r.f. mixing circuit. As shown in fig. 1, the signals then cancel each other and provide an amplitude null at a point 30 microseconds after the start of the pulse ( the required

- "3rd cycle" sampling point). Should the sampling point be set less than  $30\mu S$ , a positive output is obtained whilst if it occurs more than  $30\mu S$  after the start of the pulse the output is negative.

- 17. The stored outputs of the three index channels are routed to the d.c. voltmeter on the panel of the c.r.t. unit (as are the a.f.c. and a.g.c. channel outputs). A meter selector switch selects a.f.c., a.g.c. or index channels for display. Positioning the function switch to M, A or B selects the signal to be monitored. Additionally, the three index channels are connected via a nand gate to an alarm warning light so that an indexing fault in any channel gives rise to an alarm lamp indication. Similar alarm provision is made for the a.f.c. and a.g.c. channel outputs.

- 18. The index channel output, unlike the a.f.c. and a.g.c. outputs, is not part of a closed-loop servo system but is under the control of the operator, who is required to position the sampling gate on the proper portion of the received signal pulse. When the a.f.c. channel has established lock-on of the local oscillator, the polarity of the index channel output displayed on the meter indicates the direction of error in the sampling point position with respect to the correct  $30\mu S$  point. The operator corrects this in 10 microsecond steps to obtain a null indication (zero meter reading). The sampling point is changed in  $10\mu S$  steps by a process termed "slewing" in which the triggering of the 4 decade divider chain of the affected channel is stepped 1 cycle at a time with respect to the applied 100 kc/s input from the associated oscillator/divider system. Manual slew control in this manner has the advantage under poor signal-to-noise conditions when third cycle sampling is impracticable, that providing the c.r.t. display indicates tolerable skywave contamination later into the pulse, all three station sampling triggers may be jumped in 10 microsecond steps toward the peak of the pulse to increase the signal level in the sample.

- 19. Each of the three divider chains is capable of being manually slewed by the operator at three different rates. As indicated in para. 18, the operator may insert or blank input pulses one at a time to slew the dividers 10 microseconds in either direction. For signal acquisition when the equipment is first turned on, however, much more rapid slew is required to synchronize the entire four-decade counter to the incoming signal. For this purpose, switches are provided which select either a 50 c/s or 500 c/s signal from the divider, and these are used to slew the clock in either direction. With the coarse slew switch on the c.r.t. unit in the LEFT position, the 500 c/s signal blanks one input pulse every 2 microseconds. This slows the clock which is producing the triggers so that the signals drift to the left on the c.r.t. display at a rate which will traverse the maximum Loran repetition interval (100 milliseconds) in twenty seconds.

Fig. 1. Index derivation and gating

20. When the pulse group corresponding to the channel being slewed has reached the left edge of the sweep, and the first pulse has just started to re-appear at the right, the operator increases sweep speed to correspond to a 10 millisecond trace length (which contains the pulse group), and operates the MEDIUM slew to right. In this position, the 50 c/s signal adds one input pulse

every 20 milliseconds. This speeds up the clock which is producing the triggers so that the signals drift to the right on the c.r.t. display at a rate of 500 microseconds per second. When the first pulse of the desired group appears at the left edge of the trace, slew is stopped, the sweep rate is increased to 150 microseconds trace-length (one pulse-length) and the 10 microsecond jump is used

to position the sampling trigger on the third r.f. cycle as verified by both the c.r.t. display and the metered output of the index channel. Once a signal has been so acquired by its respective oscillator-divider combination, it will be tracked by its a.f.c. sampling and integration channel which controls local oscillator frequency to maintain the clock in synchronism with the received signal.

21. When the three clocks are synchronized with their respective signals, in other words when the receiver is tracking all three signals, the time measurements are made by comparing the phase of the A and B slave clocks with that of the master clock. To this end each divider chain develops a digitizing trigger once each clock interval (PRR): the trigger has a fixed time relation to the sampling pulse controlling its phase. 10 megacycle clock pulses derived by doubling the master oscillator frequency are gated into a binary-coded decimal counter, the length of the gate being the time-difference between the master digitizing trigger and the selected slave trigger.

The resulting count of the BCD counter is decoded and displayed on five decimal projection indicators. This single display is shared between the two slave signals. The operator may select A slave, B slave or both alternately, on an automatic time-cycling basis. The rate of display updating is internally adjustable.

#### Loran A operation

22. For LORAN-A operation, the same local oscillator and decade divider chains are used. The received pulses, after amplification and filtering in a separate r.f. amplifier, are presented to the c.r.t. along with master and slave timing pedestals decoded from their respective divider chains. The operator then manually slews the two clocks to synchronize each with its respective signal, and, as before, the output counters measure and display the phase difference between the master and slave clocks as a time difference. This operation is then repeated for the second slave. The three sampling and filtering channels described above for LORAN C are not used during LORAN A operation.

# Chapter 3

#### INSTALLATION AND OPERATION

#### LIST OF CONTENTS

|                                 |       | P       | ara.   |                                  |       | - 1     | Para.      |

|---------------------------------|-------|---------|--------|----------------------------------|-------|---------|------------|

| Units of equipment              |       |         | 1      | Control functions. Read-out unit |       | • • •   | 15         |

| Mounting and location of units  | • • • |         | 3      | Control functions. C.R.T. unit   |       |         | 16         |

| Antenna                         |       |         | 4      | Pre-set controls. C.R.T. unit    |       |         | 17         |

| Antenna amplifier. Decca Type 1 | 1953  | • • • • | 7      | Operating. Loran C               |       |         | 18         |

| Receiver, Decca Type 1831       |       |         | 9      | Mantan mai-iti au                |       |         | 20         |

| Cathode Ray Tube (C.R.T.) Un    | nit.  | Decca   |        | 7                                | •••   | • • • • |            |

| <i>Type</i> 1832                | •••   |         | 11     | Slave acquisition                | • • • | •••     | 21         |

| Read-out Unit. Decca Type 1833  | 3     |         | 12     | No master signals                | • • • |         | 22         |

| Inter-unit cables               |       |         | 13     | Use of notch filter              |       |         | <b>2</b> 3 |

| Operation                       | •••   | •••     | 14     | Operating. Loran A               | •••   | •••     | 24         |

|                                 |       | L       | IST O  | F TABLES                         |       |         | ,          |

|                                 |       | T       | 'able  |                                  |       | 7       | Table      |

| ARI.23180. Dimensions and weig  | ghts  | •••     | 1      | Connector No. 5                  |       |         | 6          |

| Connector No. 1                 | • • • | •••     | 2      | Connector No. 6                  |       |         | 7          |

| Connector No. 2                 | •••   |         | 3      | Connector No. 7                  |       |         | 8          |

| Connector No. 3                 |       |         | 4      | Connector No. 10                 |       |         | 9          |

| Connector No. 4                 | •••   | •••     | 5      | Connector No. 11                 | • • • | •••     | 10         |

|                                 |       | LIST    | OF ILI | LUSTRATIONS                      |       |         |            |

|                                 |       |         | Fig.   |                                  |       |         | Fig.       |

| Antenna amplifier Type 1953     | •••   |         | 1      | Read-out Unit Type 1833          |       |         | 4          |

| Receiver Type 1831              |       | •••     | 2      | ARI.23180. Operating controls    | • • • |         | 5          |

| CRT Unit Type 1832              |       |         | 3      | ARI.23180. Unit interconnections | z.    |         | 6          |

#### UNITS OF EQUIPMENT

1. ARI.23180 comprises the four major units listed in Table 1 and illustrated in Fig. 1 to 4. Fig. 6 illustrates the unit interconnections. Details of inter-unit cables, together with Part Numbers

for the associated cable-end plugs or sockets are listed in Tables 2 to 10.

2. In addition to the four major units of Table 1, an antenna is required. This is normally of the suppressed plate type which is specifically designed for each aircraft type to be fitted.

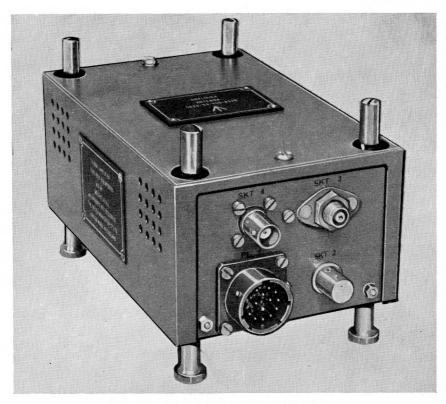

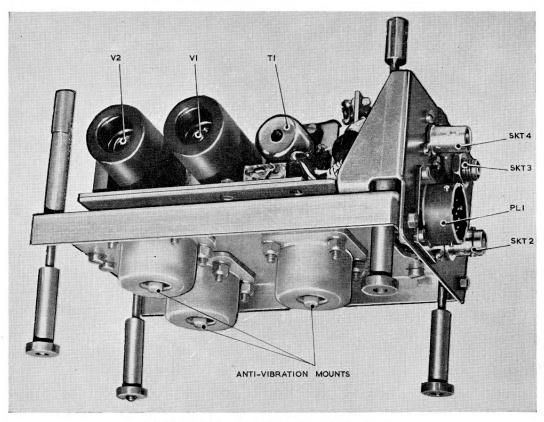

Fig. 1. Antenna amplifier Type 1953

#### MOUNTING AND LOCATION OF UNITS

**3.** In general, a large degree of flexibility exists in the siting of units, subject only to the limitations noted in the following paragraphs. On all units, plug or socket connectors are of differing types or have differing orientations to prevent insertion of a cable connector into the wrong receptacle.

#### Antenna

4. The suppressed plate antenna is a construction

of synthetic resin bonded, laminated glass fibre with an embedded wire mesh antenna element. Due the the wide variation in airframes and available locations, antennae vary considerably in shape; only general information is therefore given in this Air Publication.

5. The location of the antenna, as indicated in para. 4, is physically restricted by considerations of aircraft construction and existing obstructions, but electrically the controlling factors are that it should be as far as possible either below or above the longitudinal electrical centre of the aircraft, which

TABLE 1

ARI.23180. Dimensions and weights

|                                                 | Dimensions (inches) We |        | Weight |       |

|-------------------------------------------------|------------------------|--------|--------|-------|

|                                                 | Width                  | Depth  | Height | (lb.) |

| Receiver Unit, Type 1831 5826-99-955-8336       | 10.250                 | 22.215 | 7.750  | 39    |

| CRT Unit, Type 1832 5826-99-955-8337            | 5.750                  | 13.750 | 6.0    | 8     |

| Read-out Unit, Type 1833 5826-99-955-8338       | 5.750                  | 5.500  | 2.625  | 2     |

| Antenna Amplifier Type 1953<br>5826-99-955-8339 | 6.438                  | 3.875  | 3.875  | 1.5   |

Maximum dimensions are quoted (i.e. over knobs, handles or other projections).

Block diagram of ARI. 23180 (LORAN C/A)

is analagous to a ground plane, and that it should be positioned where the minimum static due, for example, to impact of charged precipitation is experienced. It is normally necessary to employ static dischargers at selected points on the aircraft to minimise radio noise due to the uncontrolled discharge of accumulated static electricity which would otherwise occur at wing tips, extremities of tail surfaces, jet effluxes etc. The location of such dischargers is peculiar to the aircraft configuration. Note that the indiscriminate attachment of such dischargers can produce the opposite effect to that intended (i.e. an increase in static noise on radio equipment in the aircraft).

6. Electrical connections to the antenna are made to a hexagonal stud moulded into the antenna. Where possible, two such studs are preferred to provide separate attachments for the r.f. feeder cable (Connector No. 10) and the test signal cable (Connector No. 11). Thus the test signal (which originates in the Test Set and passes via receiver SKT. 8, SKT 5, Connector No. 5, antenna amplifier PL1, SKT. 4 and Connector No. 11) is injected

into the antenna at a point which will provide test facilities to the complete installation, including antenna connections.

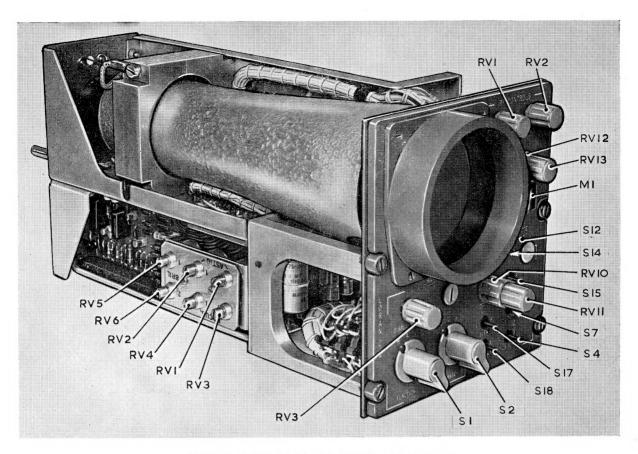

#### Antenna Amplifier. Decca Type 1953 (fig. 1)

- 7. The antenna amplifier is secured by four 10-32 UNF captive screws. Anti-vibration mounts are not required and the mounting attitude is unrestricted. The antenna amplifier is mounted so that the length of the screened feeder from the antenna (Connector No. 10) does not exceed 18 inches, with an additional 6 inches of the insulated inner conductor protruding beyond the screen.

- **8.** The outer screen of Connector No. 10 is bonded to the airframe at the antenna end only. At the amplifier end, the feeder screen is connected to the shell of the coaxial plug/socket (SKT 3) which is isolated from the amplifier case. The amplifier case is bonded to the airframe by a bonding tail secured beneath one of the cover retaining screws. The inner conductor of the test lead to the antenna (Connector No. 11) is connected via a series capacitor to the antenna. The

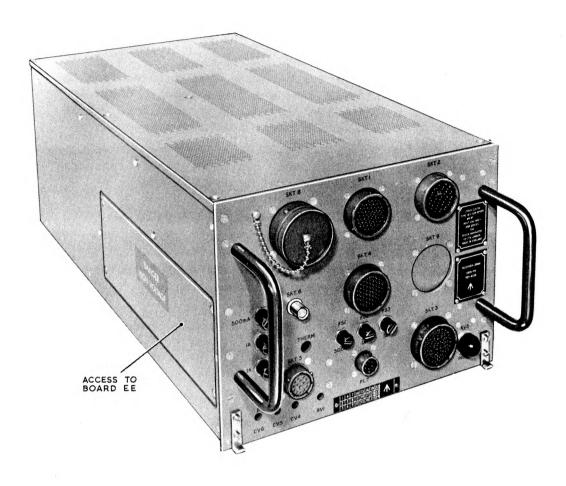

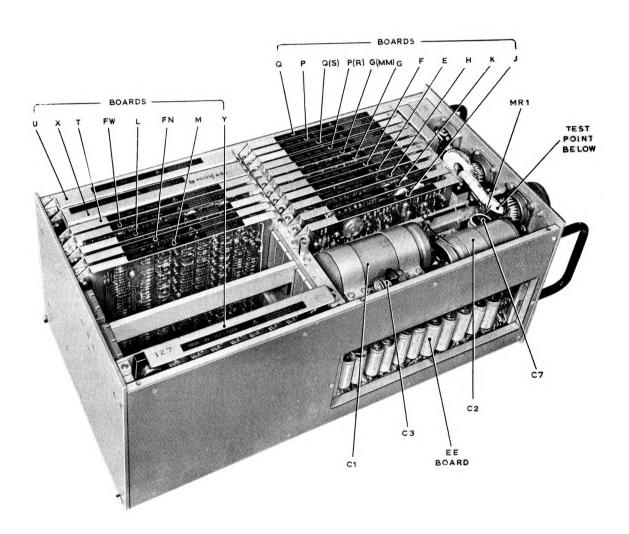

Fig. 2. Receiver Type 1831

outer screen of Connector No. 11 is left unconnected at the antenna end. Connectors No. 10 and 11 must not be interrupted by additional plug/socket connectors; where is it necessary to pass through a pressure bulkhead, a pressure bung is used.

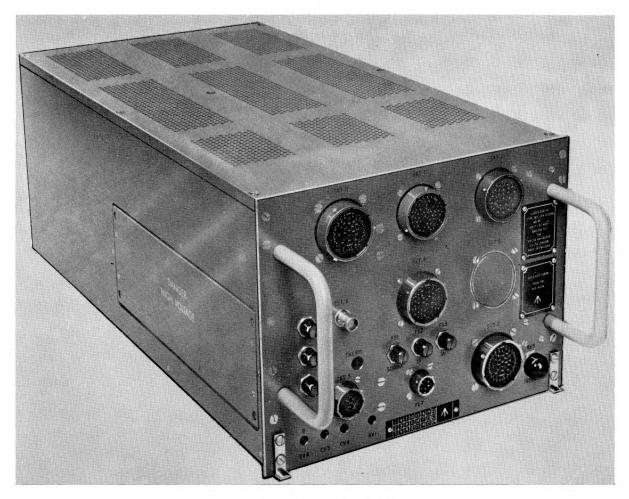

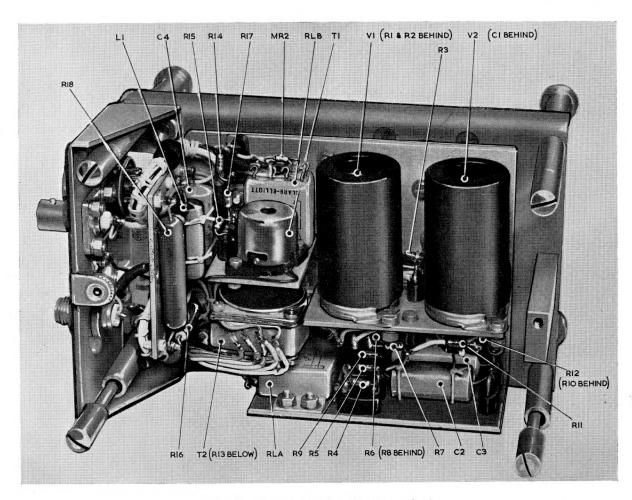

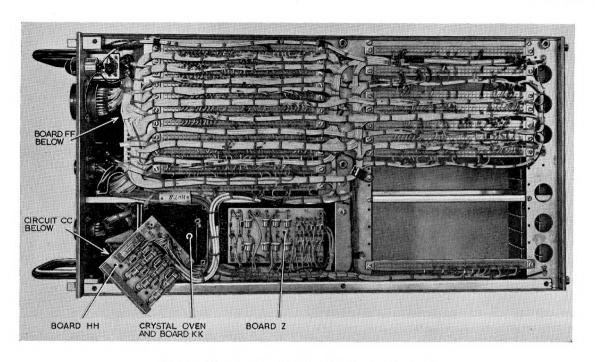

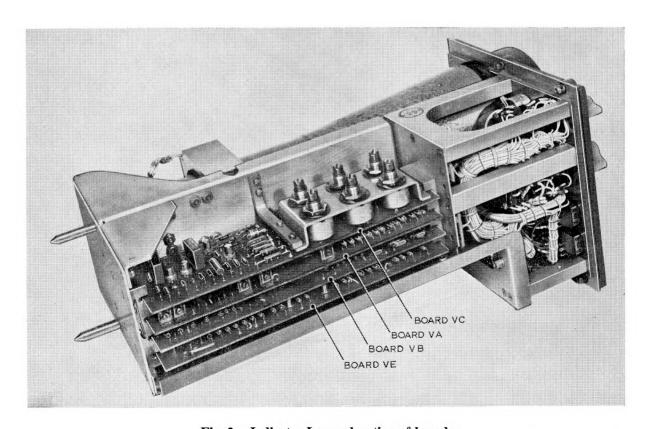

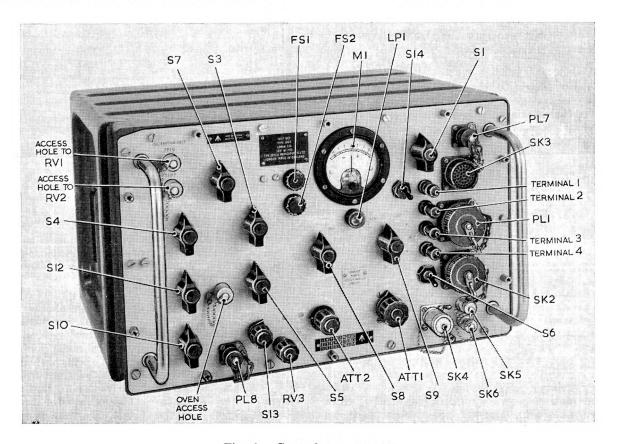

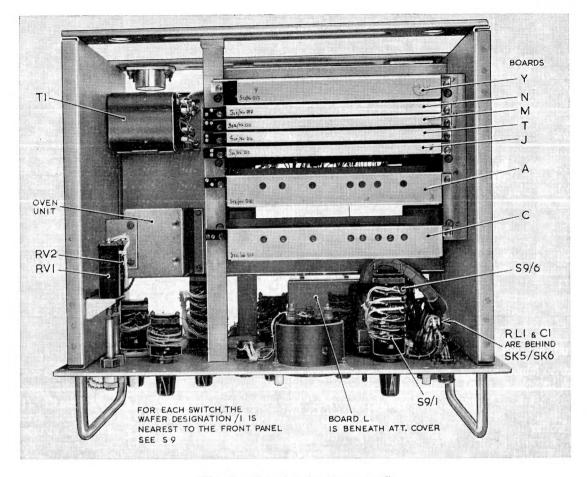

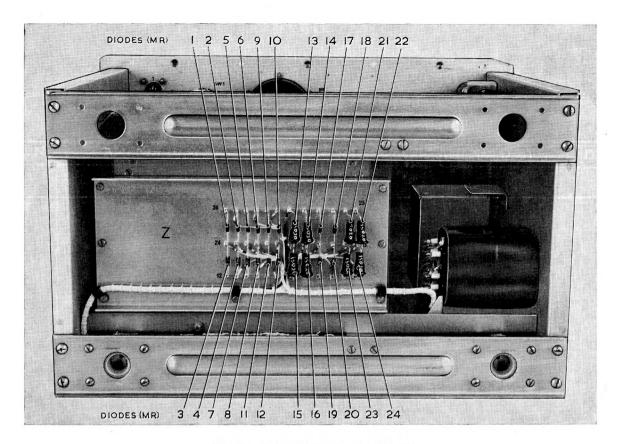

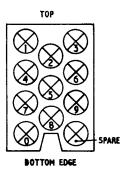

#### Receiver. Decca Type 1831 (fig. 2)

9. The Loran receiver in a 1 ATR (long) case, is secured to its mounting rack by two locking devices at the front and by two dowels on the rack which enter dowel receptacles at the rear of the

unit. The receiver must be sited within the pressurized area of the aircraft. Neither anti-vibration mounts, nor forced cooling is required. Cooling is by natural convection and sufficient space must be allowed to permit a free flow of air through the holes in top and bottom of the receiver case.

10. All installation connections are made via plugs or sockets on the front panel of the receiver. The front panel also carries fuses, a test plug for connecting a test set and pre-set controls which are required only during ground test and adjustment procedures.

Fig. 3. CRT Unit Type 1832

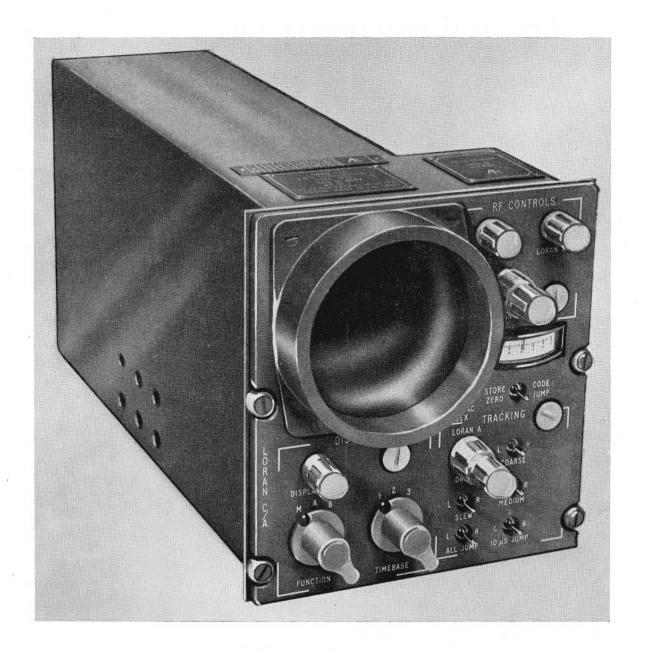

# Cathode Ray Tube (CRT) Unit. Decca Type 1832 (fig. 3)

11. The CRT unit is sited so that it may be viewed and operated by the navigator or other crew member as required. Mounting attitude is otherwise unrestricted. Anti-vibration mounts are not required. The front panel conforms to the recommendations of ARINC specification No. 306, but the front-to-rear dimension exceeds the ARINC maximum. Rear support (e.g. a backplate) must be provided to hold the unit by means of the two dowels on the rear of the unit. Electrical connections are to two plugs, of different sizes, on the stepped rear face of the unit. Note that the two cables (Connectors No. 1 and 2) between the CRT unit and the receiver should not be longer than 25 feet. During test and adjustment, access is required at the left hand side (viewed from the front) of the CRT unit, without disconnecting electrical connections.

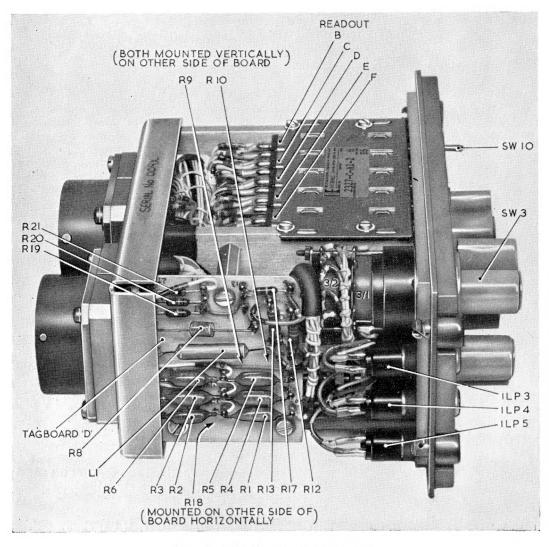

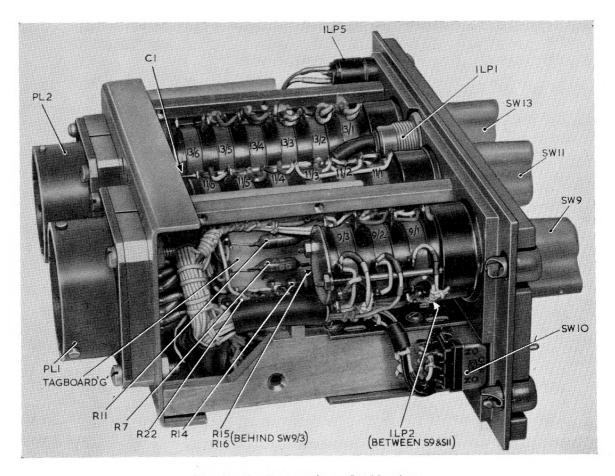

#### Read-out Unit. Decca Type 1833 (fig. 4)

12. As with the CRT unit (para. 11) this unit must be easily viewed and operated by the navigator (or other crew member as required). The unit conforms to ARINC specification No. 306. Mounting attitude is unrestricted and antivibration mounts are not required.

#### **INTER-UNIT CABLES**

13. The interconnections for ARI.23180 are shown in Fig. 6. Connectors are numbered 1 to 7 inclusive and 10 and 11 (i.e. Connectors No. 8 and 9 are omitted). Details of these connectors are listed in Tables 2 to 10. Unless otherwise stated, screening braids of all connectors must be connected to the shell of the plug or socket, at both ends of the connector.

Fig. 4. Read-out Unit Type 1833

TABLE 2

#### Connector No. 1. Receiver to CRT unit

Cable Type:

50 × Minyvin 22

Terminations:

(a) Receiver SKT1: — MS3126F-22-55PX

(b) CRT Unit PL1 ITT Cannon Electric DD50S with junction shell DD20964

(round clamp) or DD19678-4 (straight clamp). Male screw lock assemblies D20420-12.

Maximum length:

25 ft.

| Receiver SKT1 | CRT Unit PL1 | Receiver SKT1 | CRT Unit PL1 |

|---------------|--------------|---------------|--------------|

| Α             | 1            | c             | 26           |

| В             | 2            | d             | 27           |

| C             | 3            | e             | 28           |

| D             | 4            | f             | 29           |

| E             | 5            | g             | 30           |

| F             | 6            | h             | 31           |

| G             | 7            | i             | 32           |

| H             | 8            | j             | 33           |

| J             | 9            | k             | 34           |

| K             | 10           | m             | 35           |

| L             | 11           | n             | 36           |

| M             | 12           | p             | 37           |

| N             | 13           | q             | 38           |

| P             | - 14         | r             | 39           |

| R             | 15           | S             | 40           |

| S             | 16           | t             | 41           |

| T             | 17           | u             | 42           |

| U             | 18           | v             | 43           |

| V             | 19           | w             | 44           |

| W             | 20           | X             | 45           |

| X             | 21           | y             | 46           |

| Y             | 22           | z             | 47           |

| ${f Z}$       | 23           | AA            | 48           |

| a             | 24           | BB            | 49           |

| ь             | 25           | CC            | 50           |

TABLE 3

## Connector No. 2. Receiver to CRT unit

Cable Type:

13 × Minyvin 20

2 × Nyvin 20

2 × Unimedten No. 1

Terminations:

(a) Receiver SKT2: — MS3126F-22-21P

(b) CRT Unit PL2

ITT Cannon Electric DBM17 W2S with high tension inserts, DM51155 (for pins A1, A2).

Junction shell DB20962 (round clamp) or DB24659 (deep straight clamp) Male screw lock assemblies D20419-16

Maximum length: 25 ft.

| Receiver SKT2 | CRT Unit PL2 | Wire Type                               | Function |

|---------------|--------------|-----------------------------------------|----------|

| Α             | <b>A</b> 1   | Unimedten No. 1                         | 1kV      |

| В             | 1            | Minyvin 20                              | ,        |

| G             | 2            | ,,                                      | 6.3V     |

| C             | 3            | 77                                      |          |

| R             | 4            | ;,                                      |          |

| S             | 5            | ,,                                      | -24V     |

| D             | 6            | **                                      |          |

| L             | 7            | ,,                                      | +52V     |

| E             | 8            | ,,                                      |          |

| X             | 9            | ,,                                      |          |

| $\mathbf{H}$  | 10           | Nyvin 20                                | -580V    |

| F             | 11           | • • • • • • • • • • • • • • • • • • • • | -500V    |

| V             | 12           | Minyvin 20                              |          |

| M             | 13           | 22                                      |          |

| P             | 14           | 33                                      |          |

| J             | 15           | **                                      |          |

| N             | A2           | Unimedten No. 1                         | 2kV      |

TABLE 4

Connector No. 3. Receiver to read-out unit

Cable Type:

61 × Minyvin 22

Terminations:

(a) Receiver SKT3: — MS3126F-24-61P

(b) Read-out Unit PL1: — RS3126F-24-61S

| Receiver SKT3 | Read-out Unit<br>PL1 | Receiver SKT3 | Read-out Unit |

|---------------|----------------------|---------------|---------------|

| Α             | Α                    | i             | i             |

| В             | В                    | j             | j             |

| C             | C                    | k             | k             |

| D             | D                    | m             | m             |

| E             | E                    | n             | n             |

| F             | F                    | p             | p             |

| G             | G                    | q             | q             |

| H             | H                    | r             | r             |

| J             | J                    | S             | S             |

| K             | K                    | t             | t             |

| L             | L                    | u             | u             |

| M             | M                    | v             | v             |

| N             | N                    | w             | w             |

| P             | P                    | x             | X             |

| R             | R                    | y             | y             |

| S             | S                    | Z             | z             |

| T             | T                    | AA            | AA            |

| U             | $\mathbf{U}$         | BB            | BB            |

| V             | V                    | CC            | CC            |

| W             | W                    | DD            | DD            |

| X             | X                    | EE            | EE            |

| Y             | Y                    | FF            | FF            |

| ${f Z}$       | Z                    | GG            | GG            |

| a             | a                    | HH            | HH            |

| Ъ             | ь                    | JJ            | JJ            |

| С             | С                    | KK            | KK            |

| d             | . <b>d</b>           | LL            | LL            |

| e             | e                    | MM            | MM            |

| ${f f}$       | ${f f}$              | NN            | NN            |

| g             | g                    | PP            | PP            |

| ħ             | h                    |               |               |

TABLE 5

Connector No. 4. Receiver to Read-out unit

Cable Type:

55 × Minyvin 22

Terminations:

(a) Receiver SKT4: — MS3126F-22-55P

(b) Read-out Unit PL2: — MS3126F-22-55S.

| Receiver SKT4 | Read-out Unit<br>PL2 | Receiver SKT4 | Read-out Unit<br>PL2 |

|---------------|----------------------|---------------|----------------------|

| Α             | Α                    | f             | ${f f}$              |

| В             | В                    | g             | g                    |

| $\mathbf{C}$  | $\mathbf{C}$         | h             | h                    |

| D             | <b>D</b> .           | i             | i                    |

| E             | E                    | j             | j                    |

| F             | F                    | k             | k                    |

| G             | G                    | m             | m                    |

| Н             | H                    | n             | n                    |

| J             | J                    | p             | p                    |

| K             | K                    | q             | q                    |

| L             | L                    | r             | r                    |

| M             | M                    | S             | S                    |

| N             | N                    | t             | t                    |

| P             | P                    | u             | u                    |

| R             | R                    | v             | v                    |

| S             | S                    | W             | w                    |

| T             | T                    | X             | X                    |

| U             | U                    | y             | у                    |

| V             | V                    | Z             | Z                    |

| W             | W                    | AA            | AA                   |

| X             | X                    | BB            | BB                   |

| Y             | Y                    | CC            | CC                   |

| ${f Z}$       | $\mathbf{Z}$         | DD            | DD                   |

| a             | a                    | EE            | EE                   |

| b             | b                    | FF            | FF                   |

| c             | c                    | GG            | GG                   |

| d             | d                    | HH            | HH                   |

| e             | e                    |               |                      |

#### TABLE 6

#### Connector No. 5. Receiver to antenna amplifier

Cable Type:

9 × Minyvinmetsheath 22

(or 9 × Minyvin 22, collectively screened and sheathed).

Terminations:

(a) Receiver SKT5: — MS3126F-14-15P

(b) Antenna amplifier PL1: - MS3126F-14-15S

| Receiver SKT5 | Antenna Amplifier PL1 | Function                  |

|---------------|-----------------------|---------------------------|

| Α             | Α                     | 160V +                    |

| В             | В                     | 28V (Heater)              |

| C             | $\mathbf{C}$          | Test signal               |

| D             | D                     | 28V test                  |

| E             | E                     | Earth                     |

| L             | L                     | Earth                     |

| M             | M                     |                           |

| N             | N                     |                           |

| R             | R                     | 28V (Loran C/A switching) |

TABLE 7

Connector No. 6. Receiver to antenna amplifier

Cable Type:

1 × Transradio MC02E (or Duradio 68 — see Note 2)

Terminations:

(a) Receiver SKT6: — Amphenol 31-224 (Note 2)

(b) Antenna Amplifier SKT2: — Amphenol 31-224

(Note 2)

| • | Receiver SKT6 | Antenna Amplifier SKT2 |

|---|---------------|------------------------|

|   | 1             | 1                      |

|   | 2             | 2                      |

#### Notes ...

- 1. The screening braid must be earthed to the plug shell at both ends.

- 2. If Duradio 68 is used, the washer and clamp gasket of the cable-end plugs should be replaced by:—

Washer 31GB-0114 Clamp Gasket 31-1051-02

#### TABLE 8

#### Connector No. 7. Power supply to receiver

Cable Type:

$4 \times \text{Nyvin } 22 \text{ (or Minyvin } 22)$

Terminations:

(a) Power Supply (via fuses or circuit breakers): — Open ends, Fittings as required.

(b) Receiver PL7: — MS3126F-10-6S

| Power Supply            | Receiver PL7 |

|-------------------------|--------------|

| 115V 400 c/s Line       | Α            |

| 115V 400 c/s Neutral    | В            |

| 28V d.c. return (earth) | C            |

| 28V d.c. +ve            | E            |

#### TABLE 9

#### Connector No. 10. Antenna to antenna amplifier

Maximum length:

18" screened feeder (plus 6" unscreened \*)

Cable Type:

T 3283 (B.I.C.C)

Terminations:

(a) Antenna:

Inner conductor: 2BA eyelet tag (e.g. AMP lug) to antenna

terminal.

Outer screen: 2BA Z tag (or similar) to airframe

(b) Antenna Amplifier SKT3 P.E.T. 101

\* Outer screen must be stripped back 6" from antenna terminal to avoid the risk of short circuit due to condensation in the feeder.

Earth screen to airframe at antenna end only.

#### TABLE 10

#### Connector No. 11. Antenna amplifier to antenna

Cable Type:

T 3283 (B.I.C.C.)

Terminations:

(a) Antenna Amplifier SKT4 ITT Cannon Electric UG-260A/U

(b) Antenna

Outer screen: Not connected

Inner conductor: via a series-connected 2.7pF capacitor

(Erie Type NPO.AD) to the antenna terminal.

#### Note ...

Outer screen must be stripped back approximately 6" from the antenna terminal to avoid the risk of short circuit due to condensation: this screen is left un-connected at the antenna end.

Fig. 5. ARI.23180. Operating controls

#### **OPERATION**

14. All operating controls for ARI.23180 are carried either on the Read-out Unit or the CRT Unit. The functions of these controls are described in the following paragraphs (fig. 5).

#### Control Functions. Read-out unit

- 15. (1) OFF/DIM. This control combines the functions of main on/off switch and panel lamp dimmer.

- (2) A, A/B, B—selects time difference displayed on Read-out Unit. In position A, master-to-slave A time difference is displayed at 1 second intervals. In position B, master-to-slave B time difference is displayed. In position A/B the display alternates between A and B readings at approximately 1 second intervals.

- (3) SELECT STATION. The first (i.e. left-hand) of these three switches selects the frequency (1=1950 kc/s; 2=1850 kc/s; 3=1900 kc/s, C=100 kc/s) and the bandwidth for Loran-C operation (C Narrow=6 kc/s; C Wide=20kc/s). The second and third switches select basic and specific pulse recurrence rate (p.r.r.) respectively and are common to both Loran-A and Loran-C (see Chap. 1, para. 9 and 15).